# The NEORV32 RISC-V Processor Datasheet

Version v1.7.0-r8-gcc64b5cd

#### Documentation

The online documentation of the project (a.k.a. the **data sheet**) is available on GitHub-pages: https://stnolting.github.io/neorv32/

The online documentation of the **software framework** is also available on GitHubpages: https://stnolting.github.io/neorv32/sw/files.html

# **Table of Contents**

| 1. Overview                             | 9 |

|-----------------------------------------|---|

| 1.1. Rationale                          | 0 |

| 1.2. Project Key Features               | 1 |

| 1.3. Project Folder Structure           | 3 |

| 1.4. VHDL File Hierarchy                | 4 |

| 1.5. FPGA Implementation Results        | 7 |

| 1.5.1. CPU                              | 7 |

| 1.5.2. Processor - Modules              | 8 |

| 1.5.3. Exemplary Setups                 | 0 |

| 1.6. CPU Performance 2                  | 1 |

| 2. NEORV32 Processor (SoC) 2            | 3 |

| 2.1. Processor Top Entity - Signals     | 5 |

| 2.2. Processor Top Entity - Generics. 2 | 8 |

| 2.2.1. General                          | 9 |

| CLOCK_FREQUENCY. 2                      | 9 |

| INT_BOOTLOADER_EN                       | 9 |

| HW_THREAD_ID                            | 9 |

| ON_CHIP_DEBUGGER_EN 2                   | 9 |

| 2.2.2. RISC-V CPU Extensions. 2         | 9 |

| CPU_EXTENSION_RISCV_A 2                 | 9 |

| CPU_EXTENSION_RISCV_B                   | 0 |

| CPU_EXTENSION_RISCV_C                   | 0 |

| CPU_EXTENSION_RISCV_E                   | 0 |

| CPU_EXTENSION_RISCV_M                   | 0 |

| CPU_EXTENSION_RISCV_U                   | 0 |

| CPU_EXTENSION_RISCV_Zfinx               | 0 |

| CPU_EXTENSION_RISCV_Zicsr               | 0 |

| CPU_EXTENSION_RISCV_Zicntr              | 1 |

| CPU_EXTENSION_RISCV_Zihpm               | 1 |

| CPU_EXTENSION_RISCV_Zifencei            | 1 |

| CPU_EXTENSION_RISCV_Zmmul               | 1 |

| CPU_EXTENSION_RISCV_Zxcfu               | 1 |

| 2.2.3. Tuning Options                   | 1 |

| FAST_MUL_EN                             | 2 |

| FAST_SHIFT_EN                           | 2 |

| CPU_CNT_WIDTH                           | 2 |

| CPU_IPB_ENTRIES                         | 2 |

|                                         |   |

| 2.2.4. Physical Memory Protection (PMP)    | . 32 |

|--------------------------------------------|------|

| PMP_NUM_REGIONS                            | . 32 |

| PMP_MIN_GRANULARITY.                       | . 33 |

| 2.2.5. Hardware Performance Monitors (HPM) | . 33 |

| HPM_NUM_CNTS.                              | . 33 |

| HPM_CNT_WIDTH.                             | . 33 |

| 2.2.6. Internal Instruction Memory         | . 33 |

| MEM_INT_IMEM_EN                            | . 33 |

| MEM_INT_IMEM_SIZE                          | . 33 |

| 2.2.7. Internal Data Memory                | . 34 |

| MEM_INT_DMEM_EN.                           | . 34 |

| MEM_INT_DMEM_SIZE                          | . 34 |

| 2.2.8. Internal Cache Memory.              | . 34 |

| ICACHE_EN                                  | . 34 |

| ICACHE_NUM_BLOCKS                          | . 34 |

| ICACHE_BLOCK_SIZE                          | . 34 |

| ICACHE_ASSOCIATIVITY                       | . 34 |

| 2.2.9. External Memory Interface           | . 35 |

| MEM_EXT_EN.                                | . 35 |

| MEM_EXT_TIMEOUT                            | . 35 |

| MEM_EXT_PIPE_MODE                          | . 35 |

| MEM_EXT_BIG_ENDIAN                         | . 35 |

| MEM_EXT_ASYNC_RX                           | . 35 |

| 2.2.10. Stream Link Interface              | . 35 |

| SLINK_NUM_TX                               | . 35 |

| SLINK_NUM_RX                               | . 36 |

| SLINK_TX_FIFO                              | . 36 |

| SLINK_RX_FIFO                              | . 36 |

| 2.2.11. External Interrupt Controller      | . 36 |

| XIRQ_NUM_CH                                | . 36 |

| XIRQ_TRIGGER_TYPE                          | . 36 |

| XIRQ_TRIGGER_POLARITY                      | . 36 |

| 2.2.12. Processor Peripheral/IO Modules    | . 36 |

| IO_GPIO_EN                                 | . 37 |

| IO_MTIME_EN                                | . 37 |

| IO_UART0_EN                                | . 37 |

| IO_UART0_RX_FIFO                           | . 37 |

| IO_UART0_TX_FIFO.                          | . 37 |

| IO_UART1_EN                                | . 37 |

|                                            |      |

|      | IO_UART1_RX_FIFO                                                 | 37 |

|------|------------------------------------------------------------------|----|

|      | IO_UART1_TX_FIFO.                                                | 38 |

|      | IO_SPI_EN                                                        | 38 |

|      | IO_TWI_EN                                                        | 38 |

|      | IO_PWM_NUM_CH                                                    | 38 |

|      | IO_WDT_EN                                                        | 38 |

|      | IO_TRNG_EN                                                       | 38 |

|      | IO_CFS_EN                                                        | 39 |

|      | IO_CFS_CONFIG                                                    | 39 |

|      | IO_CFS_IN_SIZE                                                   | 39 |

|      | IO_CFS_OUT_SIZE                                                  | 39 |

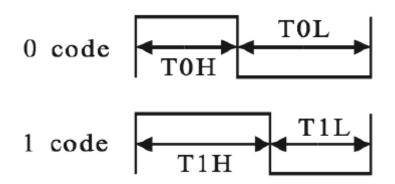

|      | IO_NEOLED_EN                                                     | 39 |

|      | IO_NEOLED_TX_FIFO                                                | 39 |

|      | IO_GPTMR_EN                                                      | 39 |

|      | IO_XIP_EN                                                        | 40 |

| 2.3. | Processor Interrupts                                             | 41 |

| 2    | .3.1. RISC-V Standard Interrupts                                 | 41 |

| 2    | .3.2. Platform External Interrupts                               | 41 |

| 2    | .3.3. NEORV32-Specific Fast Interrupt Requests                   | 42 |

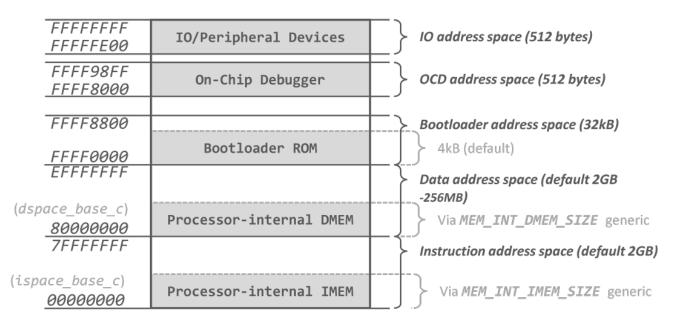

| 2.4. | Address Space                                                    | 43 |

| 2    | .4.1. CPU Data and Instruction Access                            | 43 |

| 2    | .4.2. Address Space Layout                                       | 44 |

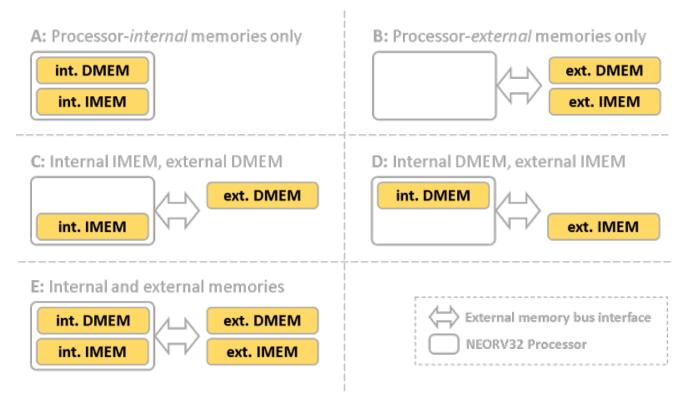

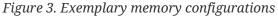

| 2    | .4.3. Memory Configuration                                       | 45 |

|      | Internal Memories                                                | 46 |

|      | External Memories                                                | 46 |

| 2    | .4.4. Boot Configuration                                         | 47 |

|      | Indirect Boot.                                                   | 48 |

|      | Direct Boot                                                      | 48 |

| 2.5. | Processor-Internal Modules                                       | 49 |

| 2    | .5.1. Instruction Memory (IMEM)                                  | 52 |

| 2    | .5.2. Data Memory (DMEM)                                         | 53 |

| 2    | .5.3. Bootloader ROM (BOOTROM).                                  | 54 |

| 2    | .5.4. Processor-Internal Instruction Cache (iCACHE)              | 55 |

| 2    | .5.5. Processor-External Memory Interface (WISHBONE) (AXI4-Lite) | 57 |

| 2    | .5.6. Internal Bus Monitor (BUSKEEPER)                           | 62 |

| 2    | .5.7. Stream Link Interface (SLINK).                             | 64 |

| 2    | .5.8. General Purpose Input and Output Port (GPIO)               | 74 |

| 2    | .5.9. Watchdog Timer (WDT)                                       | 75 |

| 2    | .5.10. Machine System Timer (MTIME)                              | 78 |

| 2.5.11. Primary Universal Asynchronous Receiver and Transmitter (UART0)    |     |

|----------------------------------------------------------------------------|-----|

| 2.5.12. Secondary Universal Asynchronous Receiver and Transmitter (UART1)  |     |

| 2.5.13. Serial Peripheral Interface Controller (SPI)                       |     |

| 2.5.14. Two-Wire Serial Interface Controller (TWI).                        |     |

| 2.5.15. Pulse-Width Modulation Controller (PWM)                            |     |

| 2.5.16. True Random-Number Generator (TRNG)                                |     |

| 2.5.17. Custom Functions Subsystem (CFS)                                   |     |

| 2.5.18. Smart LED Interface (NEOLED).                                      |     |

| 2.5.19. External Interrupt Controller (XIRQ)                               |     |

| 2.5.20. General Purpose Timer (GPTMR)                                      |     |

| 2.5.21. Execute In Place Module (XIP).                                     |     |

| 2.5.22. System Configuration Information Memory (SYSINFO)                  |     |

| SYSINFO - SoC Configuration                                                |     |

| SYSINFO - Cache Configuration                                              |     |

| 3. NEORV32 Central Processing Unit (CPU)                                   |     |

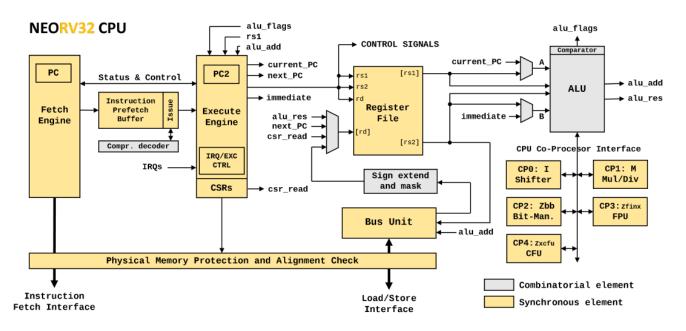

| 3.1. Architecture                                                          | 124 |

| 3.2. Full Virtualization                                                   |     |

| 3.3. RISC-V Compatibility                                                  |     |

| 3.3.1. RISC-V Incompatibility Issues and Limitations                       |     |

| 3.4. CPU Top Entity - Signals                                              | 130 |

| 3.5. CPU Top Entity - Generics                                             |     |

| 3.6. Instruction Sets and Extensions                                       |     |

| 3.6.1. A - Atomic Memory Access                                            |     |

| 3.6.2. <mark>B</mark> - Bit-Manipulation Operations                        |     |

| 3.6.3. C - Compressed Instructions                                         | 135 |

| 3.6.4. E - Embedded CPU                                                    | 135 |

| 3.6.5. I - Base Integer ISA                                                | 135 |

| 3.6.6. M - Integer Multiplication and Division                             | 136 |

| 3.6.7. Zmmul - Integer Multiplication                                      | 136 |

| 3.6.8. <mark>U</mark> - Less-Privileged User Mode                          |     |

| 3.6.9. <mark>X</mark> - NEORV32-Specific (Custom) Extensions               |     |

| 3.6.10. Zfinx Single-Precision Floating-Point Operations.                  |     |

| 3.6.11. Zicsr Control and Status Register Access / Privileged Architecture |     |

| 3.6.12. Zicntr CPU Base Counters.                                          |     |

| 3.6.13. Zihpm Hardware Performance Monitors                                |     |

| 3.6.14. Zifencei Instruction Stream Synchronization                        |     |

| 3.6.15. Zxcfu Custom Instructions Extension (CFU)                          |     |

| 3.6.16. PMP Physical Memory Protection                                     |     |

| 3.7. Custom Functions Unit (CFU)                                           |     |

| 3.7.1. Custom CFU Instructions - General        |     |

|-------------------------------------------------|-----|

| 3.7.2. Using Custom Instructions in Software    |     |

| 3.7.3. Custom Instructions Hardware             |     |

| 3.8. Instruction Timing                         |     |

| 3.9. Control and Status Registers (CSRs)        |     |

| 3.9.1. Floating-Point CSRs.                     |     |

| fflags                                          |     |

| frm                                             |     |

| fcsr                                            |     |

| 3.9.2. Machine Configuration CSRs               |     |

| menvcfg                                         | 155 |

| menvcfgh                                        |     |

| 3.9.3. Machine Trap Setup CSRs                  | 156 |

| mstatus                                         | 156 |

| misa                                            | 156 |

| mie                                             | 157 |

| mtvec                                           | 157 |

| mcounteren                                      |     |

| mstatush                                        | 159 |

| 3.9.4. Machine Trap Handling CSRs               |     |

| mscratch                                        |     |

| mepc                                            |     |

| mcause                                          |     |

| mtval                                           |     |

| mip                                             |     |

| 3.9.5. Machine Physical Memory Protection CSRs  |     |

| pmpcfg                                          |     |

| pmpaddr                                         |     |

| 3.9.6. (Machine) Counter and Timer CSRs         |     |

| cycle[h]                                        |     |

| time[h]                                         |     |

| <pre>instret[h]</pre>                           |     |

| <pre>mcycle[h]</pre>                            |     |

| <pre>minstret[h]</pre>                          |     |

| 3.9.7. Hardware Performance Monitors (HPM) CSRs |     |

| mhpmevent                                       |     |

| <pre>mhpmcounter[h]</pre>                       |     |

| 3.9.8. Machine Counter Setup CSRs               |     |

| mcountinhibit                                   |     |

| 3.9.9. Machine Information CSRs          |  |

|------------------------------------------|--|

| mvendorid                                |  |

| marchid                                  |  |

| mimpid                                   |  |

| mhartid                                  |  |

| mconfigptr                               |  |

| 3.9.10. NEORV32-Specific CSRs            |  |

| mxisa                                    |  |

| 3.9.11. Traps, Exceptions and Interrupts |  |

| Memory Access Exceptions                 |  |

| Custom Fast Interrupt Request Lines      |  |

| NEORV32 Trap Listing                     |  |

| 3.9.12. Bus Interface                    |  |

| Protocol                                 |  |

| 3.9.13. CPU Hardware Reset               |  |

| 4. Software Framework                    |  |

| 4.1. Compiler Toolchain                  |  |

| 4.2. Core Libraries                      |  |

| 4.3. Application Makefile                |  |

| 4.3.1. Targets                           |  |

| 4.3.2. Configuration                     |  |

| 4.3.3. Default Compiler Flags            |  |

| 4.4. Executable Image Format.            |  |

| 4.4.1. Linker Script                     |  |

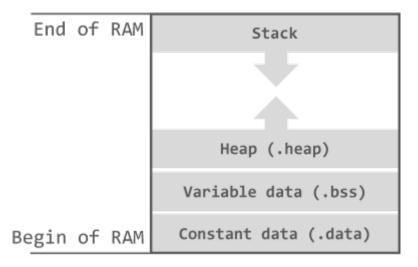

| 4.4.2. RAM Layout                        |  |

| 4.4.3. C Standard Library                |  |

| 4.4.4. Executable Image Generator        |  |

| 4.4.5. Start-Up Code (crt0)              |  |

| After-Main Handler                       |  |

| 4.5. Bootloader                          |  |

| 4.5.1. Auto Boot Sequence                |  |

| 4.5.2. Bootloader Error Codes            |  |

| 4.6. NEORV32 Runtime Environment         |  |

| 4.6.1. RTE Operation                     |  |

| 4.6.2. Using the RTE                     |  |

| 4.6.3. Default RTE Trap Handlers.        |  |

| Bus Access Faults.                       |  |

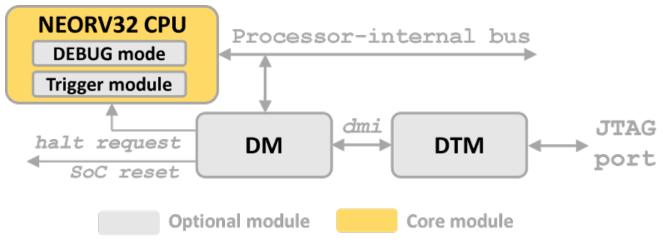

| 5. On-Chip Debugger (OCD)                |  |

| 5.1. Debug Transport Module (DTM)        |  |

|                                          |  |

| 5.2. Debug Module (DM)                     |     |

|--------------------------------------------|-----|

| 5.2.1. DM Registers                        |     |

| data                                       |     |

| dmcontrol                                  |     |

| dmstatus                                   |     |

| hartinfo                                   |     |

| abstracts                                  |     |

| command                                    |     |

| abstractauto                               |     |

| progbuf                                    |     |

| haltsum0                                   |     |

| 5.2.2. DM CPU Access                       |     |

| 5.3. CPU Debug Mode                        |     |

| 5.3.1. CPU Debug Mode CSRs                 |     |

| dcsr                                       |     |

| dpc                                        | 223 |

| dscratch0                                  |     |

| 5.4. Trigger Module                        |     |

| 5.4.1. Trigger Module CSRs                 |     |

| tselect                                    |     |

| tdata1                                     |     |

| tdata2                                     |     |

| tdata3                                     |     |

| tinfo                                      |     |

| tcontrol                                   |     |

| <pre>mcontext</pre>                        |     |

| scontext                                   |     |

| 6. Legal                                   |     |

| License                                    |     |

| Proprietary Notice                         |     |

| Disclaimer                                 |     |

| Limitation of Liability for External Links |     |

| Citing                                     |     |

| Acknowledgments                            |     |

# **Chapter 1. Overview**

The NEORV32<sup>[1]</sup> is an open-source RISC-V compatible processor system that is intended as **ready-togo** auxiliary processor within a larger SoC designs or as stand-alone custom / customizable microcontroller.

The system is highly configurable and provides optional common peripherals like embedded memories, timers, serial interfaces, general purpose IO ports and an external bus interface to connect custom IP like memories, NoCs and other peripherals. On-line and in-system debugging is supported by an OpenOCD/gdb compatible on-chip debugger accessible via JTAG.

Special focus is paid on **execution safety** to provide defined and predictable behavior at any time. Therefore, the CPU ensures that all memory access are acknowledged and no invalid/malformed instructions are executed. Whenever an unexpected situation occurs, the application code is informed via hardware exceptions.

The software framework of the processor comes with application makefiles, software libraries for all CPU and processor features, a bootloader, a runtime environment and several example programs - including a port of the CoreMark MCU benchmark and the official RISC-V architecture test suite. RISC-V GCC is used as default toolchain (prebuilt toolchains are also provided).

Check out the processor's online User Guide that provides hands-on tutorials to get you started.

#### Structure

- 2. NEORV32 Processor (SoC)

- 3. NEORV32 Central Processing Unit (CPU)

- 4. Software Framework

- 5. On-Chip Debugger (OCD)

- 6. Legal

#### Annotations

# 1.1. Rationale

#### Why did you make this?

Processor and CPU architecture designs are fascinating things: they are the magic frontier where software meets hardware. This project started as something like a *journey* into this magic realm to understand how things actually work down on this very low level and evolved over time to a capable system on chip.

But there is more: when I started to dive into the emerging RISC-V ecosystem I felt overwhelmed by the complexity. As a beginner it is hard to get an overview - especially when you want to setup a minimal platform to tinker with... Which core to use? How to get the right toolchain? What features do I need? How does booting work? How do I create an actual executable? How to get that into the hardware? How to customize things? *Where to start?*??

This project aims to provide a *simple to understand* and *easy to use* yet *powerful* and *flexible* platform that targets FPGA and RISC-V beginners as well as advanced users.

#### Why a *soft-core* processor?

As a matter of fact soft-core processors *cannot* compete with discrete (like FPGA hard-macro) processors in terms of performance, energy efficiency and size. But they do fill a niche in FPGA design space: for example, soft-core processors allow to implement the *control flow part* of certain applications (e.g. communication protocol handling) using software like plain C. This provides high flexibility as software can be easily changed, re-compiled and re-uploaded again.

Furthermore, the concept of flexibility applies to all aspects of a soft-core processor. The user can add *exactly* the features that are required by the application: additional memories, custom interfaces, specialized co-processors and even user-defined instructions.

Why RISC-V?

RISC-V is a free and open ISA enabling a new era of processor innovation through open standard collaboration.

— RISC-V International, https://riscv.org/about/

Open-source is a great thing! While open-source has already become quite popular in *software*, hardware-focused projects still need to catch up. Admittedly, there has been quite a development, but mainly in terms of *platforms* and *applications* (so schematics, PCBs, etc.). Although processors and CPUs are the heart of almost every digital system, having a true open-source silicon is still a rarity. RISC-V aims to change that - and even it is *just one approach*, it helps paving the road for future development.

Furthermore, I highly appreciate the community aspect of RISC-V. The ISA and everything beyond is

developed in direct contact with the community: this includes businesses and professionals but also hobbyist, amateurs and people that are just curious. Everyone can join discussions and contribute to RISC-V in their very own way.

Finally, I really like the RISC-V ISA itself. It aims to be a clean, orthogonal and "intuitive" ISA that resembles with the basic concepts of *RISC*: simple yet effective.

#### Yet another RISC-V core? What makes it special?

The NEORV32 is not based on another RISC-V core. It was build entirely from ground up (just following the official ISA specs). The project does not intend to replace certain RISC-V cores or just beat existing ones like VexRISC in terms of performance or SERV in terms of size. It was build having a different design goal in mind.

The project aims to provide *another option* in the RISC-V / soft-core design space with a different performance vs. size trade-off and a different focus: *embrace* concepts like documentation, platform-independence / portability, RISC-V compatibility, \_ extensibility & customization\_ and *ease of use* (see the Project Key Features below).

Furthermore, the NEORV32 pays special focus on *execution safety* using Full Virtualization. The CPU aims to provide fall-backs for *everything that could go wrong*. This includes malformed instruction words, privilege escalations and even memory accesses that are checked for address space holes and deterministic response times of memory-mapped devices. Precise exceptions allow a defined and fully-synchronized state of the CPU at every time an in every situation.

## **1.2. Project Key Features**

- open-source and documented; including user guides to get started

- completely described in behavioral, platform-independent VHDL (yet platform-optimized modules are provided)

- fully synchronous design, no latches, no gated clocks

- small hardware footprint and high operating frequency for easy integration

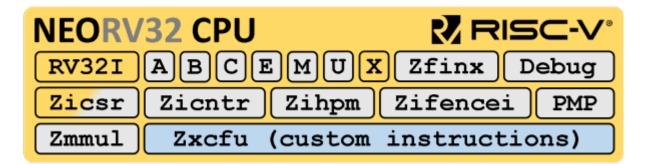

- NEORV32 CPU: 32-bit rv32i RISC-V CPU

- RISC-V compatibility: passes the official architecture tests

- base architecture + privileged architecture (optional) + ISA extensions (optional)

- option to add custom RISC-V instructions (as custom ISA extension)

- rich set of customization options (ISA extensions, design goal: performance / area (/ energy),

...)

- aims to support Full Virtualization capabilities (CPU and SoC) to increase execution safety

- official RISC-V open source architecture ID

- NEORV32 Processor (SoC): highly-configurable full-scale microcontroller-like processor system

- based on the NEORV32 CPU

- optional serial interfaces (UARTs, TWI, SPI)

- optional timers and counters (WDT, MTIME)

- $\circ$  optional general purpose IO and PWM and native NeoPixel (c) compatible smart LED interface

- optional embedded memories / caches for data, instructions and bootloader

- optional external memory interface (Wishbone / AXI4-Lite) and stream link interface (AXI4-Stream) for custom connectivity

- optional execute in place (XIP) module

- on-chip debugger compatible with OpenOCD and gdb including hardware trigger module

- Software framework

- GCC-based toolchain prebuilt toolchains available; application compilation based on GNU makefiles

- $\,\circ\,$  internal bootloader with serial user interface

- $\circ\,$  core libraries for high-level usage of the provided functions and peripherals

- runtime environment and several example programs

- doxygen-based documentation of the software framework; a deployed version is available at https://stnolting.github.io/neorv32/sw/files.html

- FreeRTOS port + demos available

For more in-depth details regarding the feature provided by he hardware see the according sections: NEORV32 Central Processing Unit (CPU) and NEORV32 Processor (SoC).

#### **Extensibility and Customization**

The NEORV32 processor was designed to ease customization and extensibility and provides several options for adding application-specific custom hardware modules and accelerators. The three most common options for adding custom on-chip modules are listed below.

- Processor-External Memory Interface (WISHBONE) (AXI4-Lite) for processor-external modules

- Custom Functions Subsystem (CFS) for tightly-coupled processor-internal co-processors

- Custom Functions Unit (CFU) for custom RISC-V instructions

A more detailed comparison of the extension/customization options can be found in section Adding Custom Hardware Modules of the user guide.

# **1.3. Project Folder Structure**

| neorv32                                                                                               | - Project home folder                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <br> -docs<br>   -datasheet<br>   -figures<br>   -icons<br>   -references<br>   -userguide            | <ul> <li>Project documentation</li> <li>AsciiDoc sources for the NEORV32 data sheet</li> <li>Figures and logos</li> <li>Misc. symbols</li> <li>Data sheets and RISC-V specs.</li> <li>AsciiDoc sources for the NEORV32 user guide</li> </ul>                                                                                          |

| <br> -rtl<br>  ⊢core<br>    └mem<br>  ⊢processor_templates<br>  ⊢system_integration<br>  └test_setups | <ul> <li>VHDL sources</li> <li>Core sources of the CPU &amp; SoC</li> <li>SoC-internal memories (default architectures)</li> <li>Pre-configured SoC wrappers</li> <li>System wrappers for advanced connectivity</li> <li>Minimal test setup "SoCs" used in the User Guide</li> </ul>                                                  |

| ⊢sim                                                                                                  | - Simulation files (see User Guide)                                                                                                                                                                                                                                                                                                   |

| └─sw<br>├─bootloader<br>├─common<br>├─example                                                         | - Software framework<br>- Sources of the processor-internal bootloader<br>- Linker script, crt0.S start-up code and central makefile<br>- Various example programs                                                                                                                                                                    |

| lib<br>  ⊢include<br>  └source<br>  image_gen<br>  ocd_firmware<br>  openocd<br>└svd                  | <ul> <li>Processor core library</li> <li>Header files (*.h)</li> <li>Source files (*.c)</li> <li>Helper program to generate NEORV32 executables^</li> <li>Source code for on-chip debugger's "park loop"</li> <li>OpenOCD on-chip debugger configuration files</li> <li>Processor system view description file (CMSIS-SVD)</li> </ul> |

# **1.4. VHDL File Hierarchy**

All necessary VHDL hardware description files are located in the project's rtl/core folder. The top entity of the entire processor including all the required configuration generics is neorv32\_top.vhd.

All core VHDL files from the list below have to be assigned to a new design library named neorv32. Additional files, like alternative top entities, can be assigned to any library.

| neorv32_top.vhd                                                                                                                                                                                              | - NEORV32 Processor top entity                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ∣<br> -neorv32_fifo.vhd<br> -neorv32_package.vhd                                                                                                                                                             | - General purpose FIFO component<br>- Processor/CPU main VHDL package file                                                                                                                                                                                                                |

| <br> -neorv32_cpu.vhd<br>   -neorv32_cpu_alu.vhd<br>     -neorv32_cpu_cp_bitmanip.vhd<br>     -neorv32_cpu_cp_cfu.vhd<br>(Zxcfu ext.)                                                                        | <ul> <li>NEORV32 CPU top entity</li> <li>Arithmetic/logic unit</li> <li>Bit-manipulation co-processor (B ext.)</li> <li>Custom functions (instruction) co-processor</li> </ul>                                                                                                            |

| <pre>    ⊢neorv32_cpu_cp_fpu.vhd<br/>    ⊢neorv32_cpu_cp_muldiv.vhd<br/>    └neorv32_cpu_cp_shifter.vhd<br/>  ⊢neorv32_cpu_bus.vhd<br/>  ⊢neorv32_cpu_control.vhd<br/>    └neorv32_cpu_decompressor.vh</pre> | <ul> <li>Floating-point co-processor (Zfinx ext.)</li> <li>Mul/Div co-processor (M extension)</li> <li>Bit-shift co-processor</li> <li>Bus interface + physical memory protection</li> <li>CPU control, exception/IRQ system and CSRs</li> <li>Compressed instructions decoder</li> </ul> |

| └neorv32_cpu_regfile.vhd                                                                                                                                                                                     | - Data register file                                                                                                                                                                                                                                                                      |

| <br> -neorv32_boot_rom.vhd                                                                                                                                                                                   | - Bootloader ROM                                                                                                                                                                                                                                                                          |

| │ └neorv32_bootloader_image.vhd<br>├neorv32_busswitch.vhd                                                                                                                                                    | - Bootloader boot ROM memory image<br>- Processor bus switch for CPU buses (I&D)                                                                                                                                                                                                          |

| heorv32_bus_keeper.vhd                                                                                                                                                                                       | - Processor-internal bus monitor                                                                                                                                                                                                                                                          |

| <pre>-neorv32_cfs.vhd</pre>                                                                                                                                                                                  | - Custom functions subsystem                                                                                                                                                                                                                                                              |

| -neorv32_debug_dm.vhd                                                                                                                                                                                        | - on-chip debugger: debug module                                                                                                                                                                                                                                                          |

| heorv32_debug_dtm.vhd                                                                                                                                                                                        | - on-chip debugger: debug transfer module                                                                                                                                                                                                                                                 |

| heorv32_dmem.entity.vhd                                                                                                                                                                                      | - Processor-internal data memory (entity-only!)                                                                                                                                                                                                                                           |

| heorv32_gpio.vhd                                                                                                                                                                                             | - General purpose input/output port unit                                                                                                                                                                                                                                                  |

| heorv32_gptmr.vhd                                                                                                                                                                                            | - General purpose 32-bit timer                                                                                                                                                                                                                                                            |

| -neorv32_icache.vhd                                                                                                                                                                                          | - Processor-internal instruction cache                                                                                                                                                                                                                                                    |

| -neorv32_imem.entity.vhd                                                                                                                                                                                     | - Processor-internal instruction memory (entity-                                                                                                                                                                                                                                          |

| only!)                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                           |

| <pre></pre>                                                                                                                                                                                                  | - IMEM application initialization image                                                                                                                                                                                                                                                   |

| heorv32_mtime.vhd                                                                                                                                                                                            | - Machine system timer                                                                                                                                                                                                                                                                    |

| -neorv32_neoled.vhd                                                                                                                                                                                          | - NeoPixel (TM) compatible smart LED interface                                                                                                                                                                                                                                            |

| -neorv32_pwm.vhd                                                                                                                                                                                             | - Pulse-width modulation controller                                                                                                                                                                                                                                                       |

| -neorv32_slink.vhd                                                                                                                                                                                           | - Stream link controller                                                                                                                                                                                                                                                                  |

| —neorv32_spi.vhd                                                                                                                                                                                             | - Serial peripheral interface controller                                                                                                                                                                                                                                                  |

| heorv32_sysinfo.vhd                                                                                                                                                                                          | - System configuration information memory                                                                                                                                                                                                                                                 |

| heorv32_trng.vhd                                                                                                                                                                                             | - True random number generator                                                                                                                                                                                                                                                            |

| ⊢neorv32_twi.vhd                                                                                                                                                                                             | - Two wire serial interface controller                                                                                                                                                                                                                                                    |

| heorv32_uart.vhd                                                                                                                                                                                             | - Universal async. receiver/transmitter                                                                                                                                                                                                                                                   |

| <pre>_neorv32_wdt.vhd</pre>                                                                                                                                                                                  | - Watchdog timer                                                                                                                                                                                                                                                                          |

| <pre>-neorv32_wishbone.vhd</pre>                                                                                                                                                                             | - External (Wishbone) bus interface                                                                                                                                                                                                                                                       |

| ⊣neorv32_xip.vhd                                                                                                                                                                                             | - Execute in place module                                                                                                                                                                                                                                                                 |

| heorv32_xirq.vhd                                                                                                                                                                                             | - External interrupt controller                                                                                                                                                                                                                                                           |

| <br> -mem/neorv32_dmem.default.vhd                                                                                                                                                                           | Default_ data memory (architecture-only)                                                                                                                                                                                                                                                  |

| └mem/neorv32_imem.default.vhd                                                                                                                                                                                | <ul> <li>_Default_ instruction memory (architecture-only)</li> </ul>                                                                                                                                                                                                                      |

The processor-internal instruction and data memories (IMEM and DMEM) are split into two design files each: a plain entity definition (neorv32\_\*mem.entity.vhd) and the actual architecture definition (mem/neorv32\_\*mem.default.vhd). The \*.default.vhd architecture definitions from rtl/core/mem provide a *generic* and *platform independent* memory design that (should) infers embedded memory blocks. You can replace/modify the architecture source file in order to use platform-specific features (like advanced memory resources) or to improve technology mapping and/or timing.

# **1.5. FPGA Implementation Results**

This section shows *exemplary* FPGA implementation results for the NEORV32 CPU and NEORV32 Processor modules. Note that certain configuration options might also have an impact on other configuration options. Furthermore, this report cannot cover all possible option combinations. Hence, the presented implementation results are just *exemplary*. If not otherwise mentioned all implementations use the default generic configurations.

## 1.5.1. CPU

| HW version:  | 1.6.9.8                                                                                   |

|--------------|-------------------------------------------------------------------------------------------|

| Top entity:  | rtl/core/neorv32_cpu.vhd                                                                  |

| FPGA:        | Intel Cyclone IV E EP4CE22F17C6                                                           |

| Toolchain:   | Quartus Prime Lite 21.1                                                                   |

| Constraints: | no timing constraints, "balanced optimization", $f_{\rm max}$ from "Slow 1200mV 0C Model" |

| CPU ISA Configuration            | LEs  | FFs  | MEM<br>bits | DSPs | f <sub>max</sub> |

|----------------------------------|------|------|-------------|------|------------------|

| rv32e                            | 830  | 400  | 512         | 0    | 129<br>MHz       |

| rv32i                            | 834  | 400  | 1024        | 0    | 129<br>MHz       |

| rv32i_Zicsr                      | 1328 | 678  | 1024        | 0    | 128<br>MHz       |

| rv32i_Zicsr_Zicntr               | 1614 | 808  | 1024        | 0    | 128<br>MHz       |

| rv32im_Zicsr_Zicntr              | 2087 | 983  | 1024        | 0    | 128<br>MHz       |

| rv32ima_Zicsr_Zicntr             | 2129 | 987  | 1024        | 0    | 128<br>MHz       |

| rv32imac_Zicsr_Zicntr            | 2338 | 992  | 1024        | 0    | 128<br>MHz       |

| rv32imacb_Zicsr_Zicntr           | 3175 | 1247 | 1024        | 0    | 128<br>MHz       |

| rv32imacbu_Zicsr_Zicntr          | 3186 | 1254 | 1024        | 0    | 128<br>MHz       |

| rv32imacbu_Zicsr_Zicntr_Zifencei | 3187 | 1254 | 1024        | 0    | 128<br>MHz       |

| CPU ISA Configuration                                       | LEs  | FFs  | MEM<br>bits | DSPs | $f_{max}$  |

|-------------------------------------------------------------|------|------|-------------|------|------------|

| <pre>rv32imacbu_Zicsr_Zicntr_Zifencei_Zfinx</pre>           | 4450 | 1906 | 1024        | 7    | 123<br>MHz |

| <pre>rv32imacbu_Zicsr_Zicntr_Zifencei_Zfinx_DebugMode</pre> | 4825 | 2018 | 1024        | 7    | 123<br>MHz |

#### **RISC-V** Compliance

The Zicsr ISA extension implements the privileged machine architecture (see Zicsr Control and Status Register Access / Privileged Architecture). The Zicntr ISA extension implements the basic counters and timers (see Zicntr CPU Base Counters). Both extensions are *mandatory* in order to comply with the RISC-V architecture specifications.

The table above does not show *all* CPU ISA extensions. More sophisticated and application-specific options like PMP and HMP are not included in this overview.

#### Goal-Driven Optimization

The CPU provides further options to reduce the area footprint (for example by constraining the CPU-internal counter sizes) or to increase performance (for example by using a barrel-shifter; at cost of extra hardware). See section Processor Top Entity - Generics for more information. Also, take a look at the User Guide section Application-Specific Processor Configuration.

## **1.5.2. Processor - Modules**

| HW version:  | 1.6.8.3                                        |

|--------------|------------------------------------------------|

| Top entity:  | rtl/core/neorv32_top.vhd                       |

| FPGA:        | Intel Cyclone IV E EP4CE22F17C6                |

| Toolchain:   | Quartus Prime Lite 21.1                        |

| Constraints: | no timing constraints, "balanced optimization" |

Table 1. Hardware utilization by processor module (mandatory modules highlighted in **bold**)

| Module        | Description                                       | LEs | FFs | MEM bits | DSPs |

|---------------|---------------------------------------------------|-----|-----|----------|------|

| Boot ROM      | Bootloader ROM (4kB)                              | 3   | 2   | 32768    | 0    |

| BUSKEEPE<br>R | Processor-internal bus monitor                    | 28  | 15  | 0        | 0    |

| BUSSWITC<br>H | Bus multiplexer for CPU instr. and data interface | 69  | 8   | 0        | 0    |

| CFS           | Custom functions subsystem <sup>[2]</sup>         | -   | -   | -        | -    |

#### The NEORV32 RISC-V Processor

| Module          | Description                                                       | LEs | FFs | MEM bits | DSPs |

|-----------------|-------------------------------------------------------------------|-----|-----|----------|------|

| DM              | On-chip debugger - debug module                                   | 473 | 240 | 0        | 0    |

| DTM             | On-chip debugger - debug transfer module (JTAG)                   | 259 | 221 | 0        | 0    |

| DMEM            | Processor-internal data memory (8kB)                              | 18  | 2   | 65536    | 0    |

| GPIO            | General purpose input/output ports                                | 102 | 98  | 0        | 0    |

| GPTMR           | General Purpose Timer                                             | 153 | 105 | 0        | 0    |

| iCACHE          | Instruction cache (2x4 blocks, 64 bytes per block)                | 417 | 297 | 4096     | 0    |

| IMEM            | Processor-internal instruction memory (16kB)                      | 12  | 2   | 131072   | 0    |

| MTIME           | Machine system timer                                              | 345 | 166 | 0        | 0    |

| NEOLED          | Smart LED Interface (NeoPixel/WS28128)<br>(FIFO_depth=1)          | 227 | 184 | 0        | 0    |

| PWM             | Pulse_width modulation controller (8 channels)                    | 128 | qq7 | 0        | 0    |

| SLINK           | Stream link interface (2xRX, 2xTX, FIFO_depth=1)                  | 136 | 116 | 0        | 0    |

| SPI             | Serial peripheral interface                                       | 114 | 94  | 0        | 0    |

| SYSINFO         | System configuration information memory                           | 13  | 11  | 0        | 0    |

| TRNG            | True random number generator                                      | 89  | 79  | 0        | 0    |

| TWI             | Two-wire interface                                                | 77  | 43  | 0        | 0    |

| UART0,<br>UART1 | Universal asynchronous receiver/transmitter 0/1<br>(FIFO_depth=1) | 195 | 143 | 0        | 0    |

| WDT             | Watchdog timer                                                    | 61  | 46  | 0        | 0    |

| WISHBONE        | External memory interface                                         | 120 | 112 | 0        | 0    |

| XIP             | Execute in place module                                           | 318 | 244 | 0        | 0    |

| XIRQ            | External interrupt controller (32 channels)                       | 245 | 200 | 0        | 0    |

Note that not all IOs were actually connected to FPGA pins (for example some GPIO inputs and outputs) when generating these reports.

## 1.5.3. Exemplary Setups

Check out the neorv32-setups repository (@GitHub: https://github.com/stnolting/neorv32-setups), which provides several demo setups for various FPGA boards and toolchains.

# **1.6. CPU Performance**

The performance of the NEORV32 was tested and evaluated using the Core Mark CPU benchmark. This benchmark focuses on testing the capabilities of the CPU core itself rather than the performance of the whole system. The according sources can be found in the sw/example/coremark folder.

#### Dhrystone

A *simple* port of the Dhrystone benchmark is also available in sw/example/dhrystone.

The resulting CoreMark score is defined as CoreMark iterations per second. The execution time is determined via the RISC-V [m]cycle[h] CSRs. The relative CoreMark score is defined as CoreMark score divided by the CPU's clock frequency in MHz.

|                 | Table 2. Configuration                                  |

|-----------------|---------------------------------------------------------|

| HW version:     | 1.5.7.10                                                |

| Hardware:       | 32kB int. IMEM, 16kB int. DMEM, no caches, 100MHz clock |

| CoreMark:       | 2000 iterations, MEM_METHOD is MEM_STACK                |

| Compiler:       | RISCV32-GCC 10.2.0                                      |

| Compiler flags: | default, see makefile                                   |

#### Table 3. CoreMark results

| СРИ                                                    | CoreMark<br>Score | CoreMarks/<br>MHz | Average CPI |

|--------------------------------------------------------|-------------------|-------------------|-------------|

| small (rv32i_Zicsr)                                    | 33.89             | 0.3389            | 4.04        |

| medium (rv32imc_Zicsr)                                 | 62.50             | 0.6250            | 5.34        |

| <pre>performance (rv32imc_Zicsr + perf. options)</pre> | 95.23             | 0.9523            | 3.54        |

The CoreMark results were generated using a rv32i toolchain. This toolchain supports standard extensions like M and C but the built-in libraries only use the base I ISA.

The "*performance*" CPU configuration uses the *FAST\_MUL\_EN* and *FAST\_SHIFT\_EN* options.

The NEORV32 CPU is based on a multi-cycle architecture. Each instruction is executed in a sequence of several consecutive micro operations. The average CPI (cycles per instruction) depends on the instruction mix of a specific applications and also on the available CPU extensions. The average CPI is computed by dividing the total number of required clock cycles (only the timed core to avoid distortion due to IO wait cycles) by the number of executed instructions ([m]instret[h] CSRs). More information regarding the execution time of each implemented instruction can be found in chapter

Instruction Timing.

Pronounced "neo-R-V-thirty-two" or "neo-risc-five-thirty-two" in its long form.

Resource utilization depends on custom design logic.

# **Chapter 2. NEORV32 Processor (SoC)**

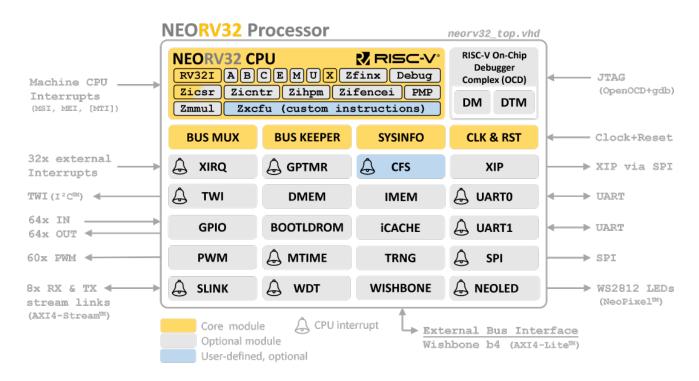

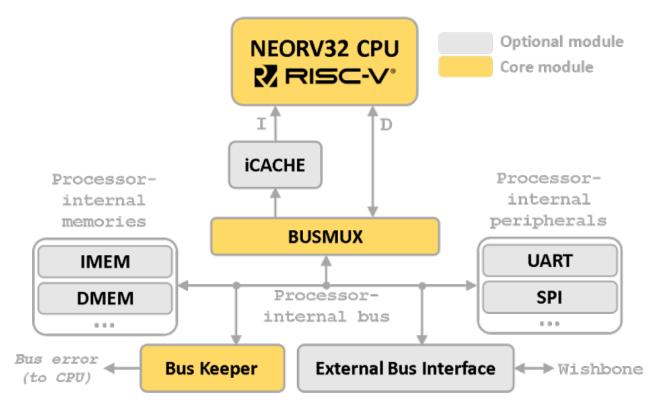

The NEORV32 Processor is based on the NEORV32 CPU. Together with common peripheral interfaces and embedded memories it provides a RISC-V-based full-scale microcontroller-like SoC platform.

#### **Key Features**

- optional processor-internal data and instruction memories (DMEM/IMEM) + cache (iCACHE)

- optional internal bootloader (BOOTROM) with UART console & SPI flash boot option

- optional machine system timer (MTIME), RISC-V-compatible

- *optional* two independent universal asynchronous receivers and transmitters (UART0, UART1) with optional hardware flow control (RTS/CTS) and optional RX/TX FIFOs

- optional 8/16/24/32-bit serial peripheral interface controller (SPI) with 8 dedicated CS lines

- optional two wire serial interface controller (TWI), compatible to the I<sup>2</sup>C standard

- optional general purpose parallel IO port (GPIO), 64xOut, 64xIn

- optional 32-bit external bus interface, Wishbone b4 / AXI4-Lite compatible (WISHBONE)

- optional 32-bit stream link interface with up to 8 independent links, AXI4-Stream compatible (SLINK)

- optional watchdog timer (WDT)

- optional PWM controller with up to 60 channels & 8-bit duty cycle resolution (PWM)

- *optional* ring-oscillator-based true random number generator (TRNG)

- optional custom functions subsystem for custom co-processor extensions (CFS)

- optional NeoPixel<sup>™</sup>/WS2812-compatible smart LED interface (NEOLED)

- optional external interrupt controller with up to 32 channels (XIRQ)

- optional general purpose 32-bit timer (GPTMR)

- *optional* execute in place module (XIP)

- *optional* on-chip debugger with JTAG TAP (**OCD**)

- bus keeper to monitor processor-internal bus transactions (BUSKEEPER)

- system configuration information memory to check HW configuration via software (SYSINFO)

# 2.1. Processor Top Entity - Signals

The following table shows signals of the processor top entity (rtl/core/neorv32\_top.vhd). The type of all signals is std\_ulogic or std\_ulogic\_vector, respectively.

#### Default Values of Ports

All *input signals* provide default values in case they are not explicitly assigned during instantiation. For control signals the value L (weak pull-down) is used. For serial and parallel data signals the value U (unknown) is used. Pulled-down signals will not cause "accidental" system crashes since all control signals have defined level.

#### Configurable Amount of Channels

Some peripherals allow to configure the number of channels to-be-implemented by a generic (for example the number of PWM or SLINK channels). The according input/output signals have a fixed sized regardless of the actually configured amount of channels. If less than the maximum number of channels is configured, only the LSB-aligned channels are used: in case of an *input port* the remaining bits/channels are left unconnected; in case of an *output port* the remaining bits/channels are hardwired to zero.

| Width                                                             | Dir.                                                                                       | Function                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Global Control                                                    |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1                                                                 | in                                                                                         | global clock line, all registers triggering on rising edge                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 1                                                                 | in                                                                                         | global reset, asynchronous, <b>low-active</b>                                                                                                                                                                                                                                                                                                                              |  |  |  |

| JTAG Access Port for On-Chip Debugger (OCD)                       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| jtag_trst_i 1 in TAP reset, low-active (optional <sup>[3]</sup> ) |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 1                                                                 | in                                                                                         | serial clock                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 1                                                                 | in                                                                                         | serial data input                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                                                                 | out                                                                                        | serial data output <sup>[4]</sup>                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                                                                 | in                                                                                         | mode select                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                   | Extern                                                                                     | nal Bus Interface (WISHBONE)                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 3                                                                 | out                                                                                        | tag (access type identifier)                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 32                                                                | out                                                                                        | destination address                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 32                                                                | in                                                                                         | write data                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 32                                                                | out                                                                                        | read data                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 1                                                                 | out                                                                                        | write enable ('0' = read transfer)                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 4                                                                 | out                                                                                        | byte enable                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                   | 1<br>1<br>J<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>3<br>3<br>2<br>32<br>32<br>32<br>32<br>1 | 1       in         1       out         1       out         1       in         1       out         3       out         32       out         32       out         1       out         1       out |  |  |  |

| Signal                    | Width     | Dir.       | Function                                        |

|---------------------------|-----------|------------|-------------------------------------------------|

| wb_stb_o                  | 1         | out        | strobe                                          |

| wb_cyc_o                  | 1         | out        | valid cycle                                     |

| wb_lock_o                 | 1         | out        | exclusive access request                        |

| wb_ack_i                  | 1         | in         | transfer acknowledge                            |

| wb_err_i                  | 1         | in         | transfer error                                  |

|                           |           | Advar      | nced Memory Control Signals                     |

| fence_o                   | 1         | out        | indicates an executed <i>fence</i> instruction  |

| fencei_o                  | 1         | out        | indicates an executed <i>fencei</i> instruction |

|                           |           | Exec       | cute In Place Interface (XIP)                   |

| xip_csn_o                 | 1         | out        | chi select, low-active                          |

| <pre>xip_clk_o</pre>      | 1         | out        | serial clock                                    |

| xip_sdi_i                 | 1         | in         | serial data input                               |

| xip_sdo_o                 | 1         | out        | serial data output                              |

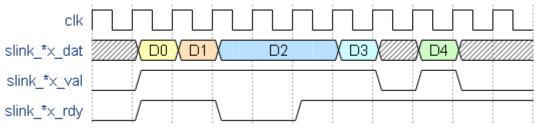

|                           |           | Stre       | eam Link Interface ( <mark>SLINK</mark> )       |

| <pre>slink_tx_dat_o</pre> | 8x32      | out        | TX link <i>n</i> data                           |

| <pre>slink_tx_val_o</pre> | 8         | out        | TX link <i>n</i> data valid                     |

| <pre>slink_tx_rdy_i</pre> | 8         | in         | TX link <i>n</i> allowed to send                |

| <pre>slink_rx_dat_i</pre> | 8x32      | in         | RX link <i>n</i> data                           |

| slink_rx_val_i            | 8         | in         | RX link <i>n</i> data valid                     |

| <pre>slink_rx_rdy_o</pre> | 8         | out        | RX link <i>n</i> ready to receive               |

|                           |           | General I  | Purpose Inputs & Outputs (GPIO)                 |

| gpio_o                    | 64        | out        | general purpose parallel output                 |

| gpio_i                    | 64        | in         | general purpose parallel input                  |

| Р                         | rimary Ur | niversal A | synchronous Receiver/Transmitter (UART0)        |

| uart0_txd_o               | 1         | out        | UART0 serial transmitter                        |

| uart0_rxd_i               | 1         | in         | UART0 serial receiver                           |

| uart0_rts_o               | 1         | out        | UART0 RX ready to receive new char              |

| uart0_cts_i               | 1         | in         | UART0 TX allowed to start sending               |

| Р                         | rimary Ur | niversal A | synchronous Receiver/Transmitter (UART1)        |

| uart1_txd_o               | 1         | out        | UART1 serial transmitter                        |

| uart1_rxd_i               | 1         | in         | UART1 serial receiver                           |

| uart1_rts_o               | 1         | out        | UART1 RX ready to receive new char              |

|                           |           |            |                                                 |

| Signal      | Width                                        | Dir.      | Function                                                                                                                                  |  |  |  |

|-------------|----------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| uart1_cts_i | 1                                            | in        | UART1 TX allowed to start sending                                                                                                         |  |  |  |

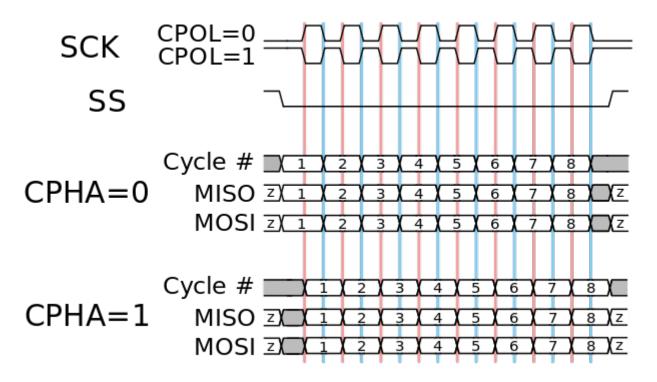

|             | Serial Peripheral Interface Controller (SPI) |           |                                                                                                                                           |  |  |  |

| spi_sck_o   | 1                                            | out       | SPI controller clock line                                                                                                                 |  |  |  |

| spi_sdo_o   | 1                                            | out       | SPI serial data output                                                                                                                    |  |  |  |

| spi_sdi_i   | 1                                            | in        | SPI serial data input                                                                                                                     |  |  |  |

| spi_csn_o   | 8                                            | out       | SPI dedicated chip select (low-active)                                                                                                    |  |  |  |

|             |                                              | Two-W     | 'ire Interface Controller (TWI)                                                                                                           |  |  |  |

| twi_sda_io  | 1                                            | inout     | TWI serial data line                                                                                                                      |  |  |  |

| twi_scl_io  | 1                                            | inout     | TWI serial clock line                                                                                                                     |  |  |  |

|             |                                              | Pulse-Wi  | dth Modulation Channels (PWM)                                                                                                             |  |  |  |