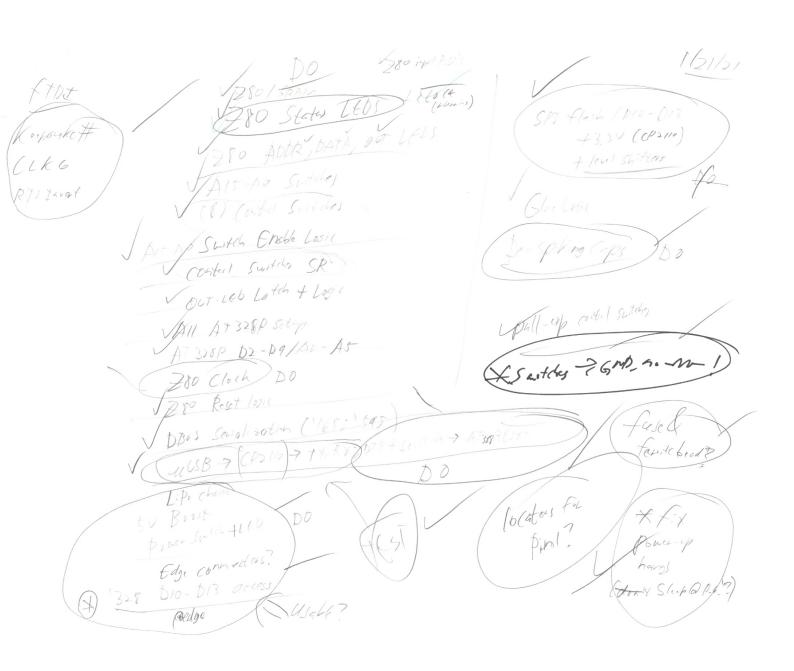

Cathent To-Do

- Try Usis & F230 for Clk 6, DTRH (and ktop). ALAN HE H) (3.3 × out

(gited at 744 Hotelson + Klot obligation 5 15)

Rest Promotion for the Show Horse power south States LEOS fary from to brook

Flore Committees for 200

Poster Committees for address south, 7 600

And power address south, 7 600

Show components mound to sepan restored

ACT CLASSES (entre (GND)?

CACIORC

PROBLEM TANK TOWN TOWN TOWN TOWN TOWN TOWN TOWN THE TOWN THE TOWN TOWN THE TOWN THE

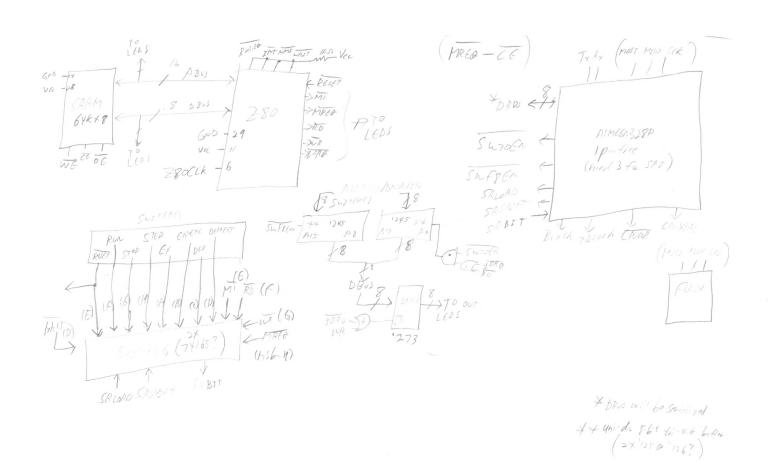

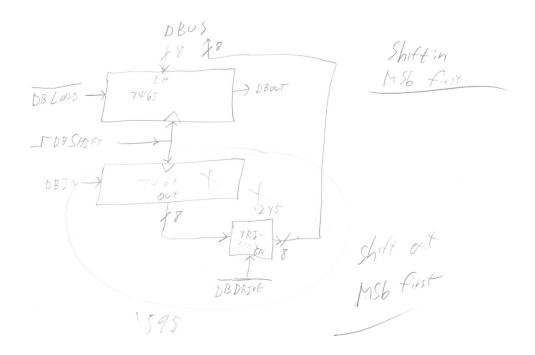

# DATABOS SERTALIZATION

|                      | 308/ |

|----------------------|------|

| DO RX                | 30   |

| DITX                 | 3 /  |

| D2 PBLOAD            | 32   |

| D3 DBSATFT           | 1    |

| D4 DBOUT             | 2    |

| DIS DEIN             | 9    |

| DEDRIK               | 10   |

| D7 SPLOAD            |      |

| D8 SRSHIFT           | 12   |

| pg Skout             | / 3  |

| 10 Sel               | 14   |

| DIN HOST             | 15   |

| DB Sch               | 16   |

| A                    | 17   |

| AU Block             | 23   |

| A CPUMP<br>AZ YBIOCE | 24   |

| A3 CAUNTAL           | 25   |

| A4 STATION           |      |

| AS SW70EN            | 28   |

CHOTES (PONER)

|                                                             | (6 LPLEXETY                  | RELLABILLTY                 | OTHER                                                                |  |  |  |  |

|-------------------------------------------------------------|------------------------------|-----------------------------|----------------------------------------------------------------------|--|--|--|--|

| Lipo 7 System Bus                                           | 7384                         | 3.70 2 280???               | If disdage > chase USB  ponce will endulle be insufficient           |  |  |  |  |

| LiPo+Boust > Sister Bus                                     | 72831/Booder/Big<br>Industra | PERFECT                     | Higher dit chase Late; USB } for power mass not scattice } for ship; |  |  |  |  |

| LiPs + Loodshare<br>\( \rightarrow \text{Be that starty} \) | 7387/                        | 3.7v ( 2 to? But can playin | USB ponce always an option                                           |  |  |  |  |

| Lipo-1 Bort + Lond Stake Ly Beller States                   | 7377/Bowles/<br>Big Inductor | PERFEET                     | USB Points alongs } free an option of shiften?                       |  |  |  |  |

|                                                             | (40 +10 )                    | ^/^ ^ \                     | Shiffer?                                                             |  |  |  |  |

|     |      | (017 | CH    | 10160 | SERLAL) |               |  |

|-----|------|------|-------|-------|---------|---------------|--|

| 0.1 |      | COST | AUAJI | 700   | DONE    | EXTERNAL XYAL |  |

| CP. | 2102 | 883  | X     | OFN   | 40      | NO            |  |

| CH  | 349  | \$   | **    | 501(  | YES     | ¥ E5          |  |

| FT  | 23   | \$\$ | ***   | Sote  | NO      | No            |  |

|     | 17   | 1    |       |       |         |               |  |

|     | 3.71 | h    |       | 1     |         |               |  |

232 (to 16)

Version 1.2

Document No.: FT\_000565 Clearance No.: FTDI# 261

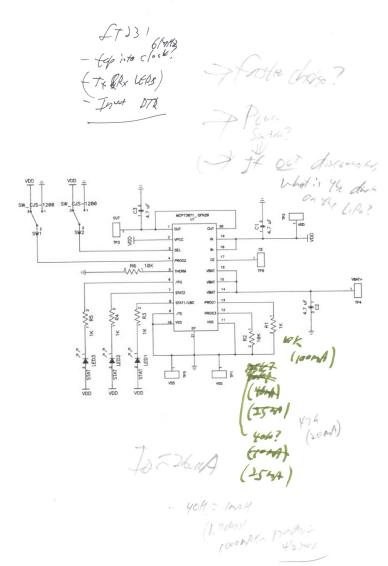

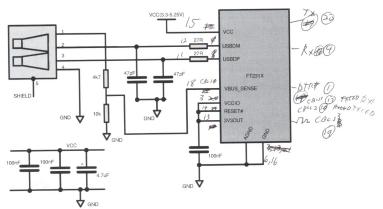

## 6.2 Self Powered Configuration

Figure 6.2 Self Powered Configuration

Figure 6.2 illustrates the FT231X in a typical USB self powered configuration. A USB self powered device gets its power from its own power supply, VCC, and does not draw current from the USB bus. The basic rules for USB self powered devices are as follows –

- i)

- A self powered device should not force current down the USB bus when the USB host or hub controller is powered down.

A self powered device can use as much current as it needs during normal operation and USB suspend as it has its own power supply.

A self powered device can be used with any USB host, a bus powered USB hub or a self powered USB hub. ii)

- iii)

The power descriptor in the internal MTP memory of the FT231X should be programmed to a value of zero (self powered).

In order to comply with the first requirement above, the USB bus power (pin 1) is used to control the VBUS\_Sense pin of the FT220X device. When the USB host or hub is powered up an internal  $1.5 \mathrm{k}\Omega$  resistor on USBDP is pulled up to  $+3.3 \mathrm{V}$ , thus identifying the device as a full speed device to the USB host or hub. When the USB host or hub is powered off, VBUS\_Sense pin will be low and the FT220X is held in a suspend state. In this state the internal  $1.5 \mathrm{k}\Omega$  resistor is not pulled up to any power supply (hub or host is powered down), so no current flows down USBDP via the  $1.5 \mathrm{k}\Omega$  pull-up resistor. Failure to do this may cause some USB host or hub controllers to power up erratically.

Figure 6.2 illustrates a self powered design which has a +3.3V to +5.25V supply.

### Note:

1. When the FT231X is in reset, the UART interface I/O pins are tri-stated. Input pins have internal  $200k\Omega$  pull-up resistors to VCCIO, so they will gently pull high unless driven by some external logic.

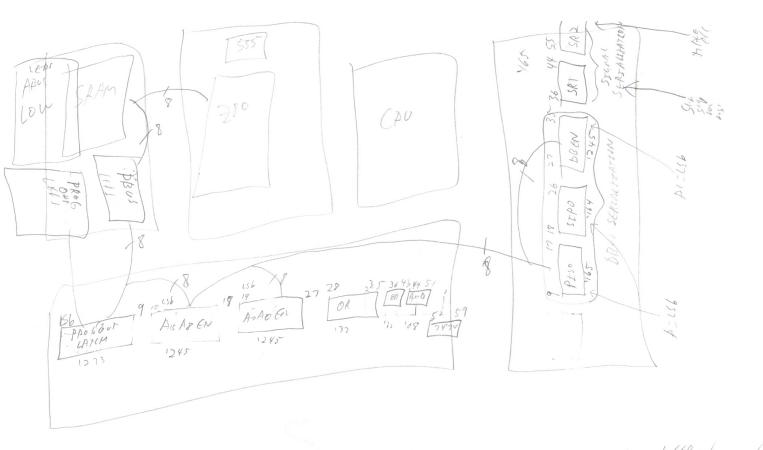

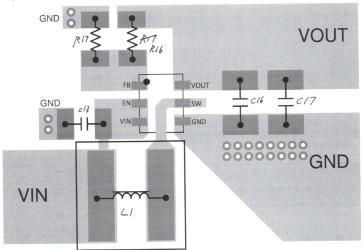

#### 10 Layout

#### 10.1 Layout Guidelines

As for all switching power supplies, especially those running at high switching frequency and high currents, layout is an important design step. If the layout is not carefully done, the regulator could suffer from instability and noise problems. To maximize efficiency, switch rise and fall time are very fast. To prevent radiation of high frequency noise (for example, EMI), proper layout of the high-frequency switching path is essential. Minimize the length and area of all traces connected to the SW pin, and always use a ground plane under the switching regulator to minimize interplane coupling. The input capacitor needs not only to be close to the VIN pin, but also to the SND pin in order to reduce inout supply ripole. to the GND pin in order to reduce input supply ripple.

The most critical current path for all boost converters is from the switching FET, through the rectifier FET, then the output capacitors, and back to ground of the switching FET. This high current path contains nanosecond rise and fall time and must be kept as short as possible. Therefore, the output capacitor not only must be close to the VOUT pin, but also to the GND pin to reduce the overshoot at the SW pin and VOUT pin.

For better thermal performance, TI suggest to make copper polygon connected with each pin bigger.

#### 10.2 Layout Example

Figure 10-1. Layout Example

Submit Document Feedback

Copyright @ 2020 Texas Instruments Incorporated

2044