## Computer systems: from numbers to processor

Kris Demuynck

19th January 2021

#### Abstract

In this book the principles of the inner workings of a computer are discussed. Knowledge of these principles is crucial to be able to install computers and networks. But also in order to develop correct working software.

This document consists of two parts. In the first part representations of different kinds of information are explained. First, numeral systems are described with an emphasis on the binary and hexadecimal system. Next, this document explains how computers can calculate with natural numbers, integers, and decimal numbers. Also, an introduction is given how computers represent characters.

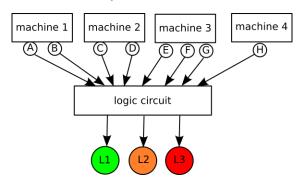

In the second part a simple but complete working processor is constructed. It starts by explaining the basic components that make up a computer (logic gates) and shows how to combine them to create more complicated logic circuits. At the end all this is combined to construct the processor and to introduce the reader to assembly language. This allows for a greater understanding of higher level programming languages and how they map to operations executed on the processor.

## Copyright

Kris Demuynck

Computer systems: from numbers to processor

© 2011-2020, Kris Demuynck (kris.demuynck@gmail.com)

This work is licensed under the Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-sa/4.0/ or send a letter to Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

# Contents

| 1 | Nur | neral s | systems                                                                                                                                      | 9  |

|---|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1 | Repres  | sentation of numbers                                                                                                                         | 9  |

|   |     | 1.1.1   | The decimal numeral system                                                                                                                   | 9  |

|   |     | 1.1.2   | The binary numeral system                                                                                                                    | 10 |

|   |     | 1.1.3   | The hexadecimal numeral system                                                                                                               | 11 |

|   |     | 1.1.4   | The octal numeral system                                                                                                                     | 11 |

|   |     | 1.1.5   | Other numeral systems                                                                                                                        | 12 |

|   | 1.2 | Conve   | rsion                                                                                                                                        | 12 |

|   |     | 1.2.1   | From any numeral system to decimal                                                                                                           | 12 |

|   |     | 1.2.2   | From decimal to any other numeral system                                                                                                     | 12 |

|   |     | 1.2.3   | Binary and hexadecimal                                                                                                                       | 13 |

|   | 1.3 | Negat   | ive numbers                                                                                                                                  | 14 |

|   |     | 1.3.1   | Sign bit                                                                                                                                     | 15 |

|   |     | 1.3.2   | 1-complement                                                                                                                                 | 16 |

|   |     | 1.3.3   | 2-complement                                                                                                                                 | 17 |

|   |     | 1.3.4   | Offset                                                                                                                                       | 18 |

|   | 1.4 | The b   | inary system in IT                                                                                                                           | 19 |

|   |     | 1.4.1   | Data types in java                                                                                                                           | 19 |

|   |     | 1.4.2   | Converting numbers using java                                                                                                                | 19 |

|   |     | 1.4.3   | Literals in Java                                                                                                                             | 20 |

|   |     | 1.4.4   | $Units \ldots \ldots$ | 20 |

|   |     | 1.4.5   | MSB en LSB                                                                                                                                   | 21 |

|   |     | 1.4.6   | Little endian and big endian                                                                                                                 | 21 |

|   | 1.5 | Chara   | cters                                                                                                                                        | 21 |

|   |     | 1.5.1   | Legacy systems                                                                                                                               | 22 |

|   |     | 1.5.2   | ASCII                                                                                                                                        | 22 |

|   |     | 1.5.3   | ISO 8859                                                                                                                                     | 23 |

|   |     | 1.5.4   | Unicode: code points                                                                                                                         | 23 |

|   |     | 1.5.5          | Unicode: encodings                                                                                                                                                                     |  |

|---|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   |     |                | 1.5.5.1 UCS $\ldots$ 24                                                                                                                                                                |  |

|   |     |                | 1.5.5.2 UTF 24                                                                                                                                                                         |  |

|   | 1.6 | Binary         | arithmetic                                                                                                                                                                             |  |

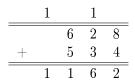

|   |     | 1.6.1          | Additions and subtractions                                                                                                                                                             |  |

|   |     | 1.6.2          | Multiplication                                                                                                                                                                         |  |

|   |     |                | 1.6.2.1 The long multiplication method $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 27$                                                                                    |  |

|   |     |                | 1.6.2.2 The long multiplication algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 28$                                                                                        |  |

|   |     |                | 1.6.2.3 Booth's algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 30$                                                                                   |  |

|   |     | 1.6.3          | Division                                                                                                                                                                               |  |

|   | 1.7 | Exercis        | ses                                                                                                                                                                                    |  |

|   |     | 1.7.1          | Converting between numeral systems                                                                                                                                                     |  |

|   |     | 1.7.2          | Negative numbers                                                                                                                                                                       |  |

|   |     |                | 1.7.2.1 Representations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                                                                                   |  |

|   |     |                | 1.7.2.2 From decimal to binary $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 33$                                                                                                   |  |

|   |     |                | 1.7.2.3 From binary to decimal $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 33$                                                                                            |  |

|   |     |                | 1.7.2.4 Range                                                                                                                                                                          |  |

|   |     | 1.7.3          | Unicode and UTF-8 encoding $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 33$                                                                                                |  |

|   |     | 1.7.4          | Unicode and UTF-8 decoding $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 34$                                                                                                |  |

|   |     | 1.7.5          | Adding and subtracting $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 34$                                                                                             |  |

|   |     | 1.7.6          | Multiplying                                                                                                                                                                            |  |

|   |     | 1.7.7          | Calculations in java                                                                                                                                                                   |  |

|   |     | 1.7.8          | Divisions in java                                                                                                                                                                      |  |

|   |     | 1.7.9          | Dataypes in java                                                                                                                                                                       |  |

| 2 | Boo | l numt         | bers 36                                                                                                                                                                                |  |

| 4 | 2.1 |                |                                                                                                                                                                                        |  |

|   | 2.1 |                | lecimal to binary                                                                                                                                                                      |  |

|   | 4.4 | 2.2.1          | Iterative method                                                                                                                                                                       |  |

|   |     | 2.2.1          | Direct method                                                                                                                                                                          |  |

|   | 2.3 |                | point representation                                                                                                                                                                   |  |

|   | 2.0 |                | ng point                                                                                                                                                                               |  |

|   | 2.5 |                | $754 \ldots \ldots$                                             |  |

|   | 2.0 | 2.5.1          | The value of a IEEE 754 number                                                                                                                                                         |  |

|   |     | 2.5.2          | From decimal to IEEE 754                                                                                                                                                               |  |

|   |     | 2.5.2<br>2.5.3 | Denormalisation                                                                                                                                                                        |  |

|   | 2.6 |                | $\begin{array}{c} \text{g point in java} \\ \end{array} \qquad \qquad$ |  |

|   |     |                |                                                                                                                                                                                        |  |

|   | 2.7               | Exercises                                         | 43        |

|---|-------------------|---------------------------------------------------|-----------|

|   |                   | 2.7.1 Decimal - Binary                            | 43        |

|   |                   | 2.7.2 Binary - Decimal                            | 43        |

|   |                   | 2.7.3 Convert to fixed point                      | 44        |

|   |                   | 2.7.4 Calculations with fixed point               | 44        |

|   |                   | 2.7.5 Convert to floating point                   | 44        |

|   |                   | 2.7.6 Convert from fixed point and floating point | 45        |

|   |                   | 2.7.7 Floating point in java                      | 45        |

|   |                   | 2.7.8 Errors in java code                         | 45        |

| 9 | Lam               |                                                   | 17        |

| 3 | <b>год</b><br>3.1 |                                                   | εί<br>47  |

|   | 3.1               |                                                   |           |

|   | 3.2               |                                                   | 48<br>48  |

|   |                   | 5                                                 |           |

|   |                   | 5                                                 | 49<br>40  |

|   |                   | 5                                                 | 49<br>40  |

|   |                   | 5                                                 | 49<br>- 0 |

|   |                   |                                                   | 50        |

|   |                   | 5                                                 | 50        |

|   | 0.0               |                                                   | 51        |

|   | 3.3               |                                                   | 51        |

|   |                   |                                                   | 51        |

|   |                   |                                                   | 52        |

|   | <u> </u>          | 0                                                 | 53        |

|   | 3.4               |                                                   | 53        |

|   |                   |                                                   | 53        |

|   |                   | 3.4.2 All possible gates                          | 54        |

| 4 | Boo               | blean algebra                                     | 55        |

|   | 4.1               | Definition                                        | 55        |

|   | 4.2               | De Morgan's laws                                  | 56        |

|   | 4.3               | Simplifying Boolean expressions                   | 57        |

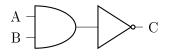

|   | 4.4               | Convert to NAND gates                             | 58        |

|   | 4.5               | Converting truth tables                           | 59        |

|   |                   | 4.5.1 The conjunctive normal form                 | 59        |

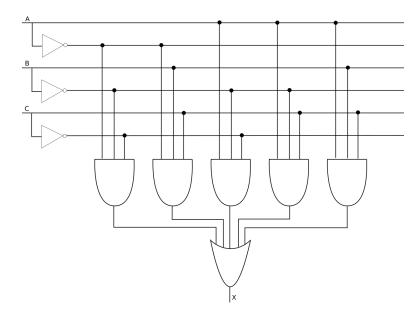

|   |                   | 4.5.2 Programmable logic arrays (PLA)             | 30        |

|   |                   |                                                   | 31        |

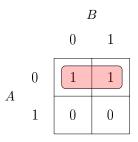

|   |     |         | 4.5.3.1   | Two inputs .     |         |                        |                        |      | • • | <br>• • | • • | • • | • • | • • | • • | 61               |

|---|-----|---------|-----------|------------------|---------|------------------------|------------------------|------|-----|---------|-----|-----|-----|-----|-----|------------------|

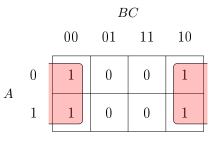

|   |     |         | 4.5.3.2   | Three inputs     |         |                        |                        |      |     | <br>    |     |     |     |     |     | 62               |

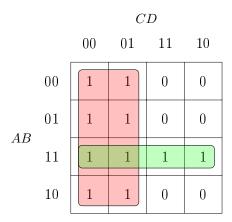

|   |     |         | 4.5.3.3   | Four inputs .    |         |                        |                        |      |     | <br>    |     |     |     |     |     | 63               |

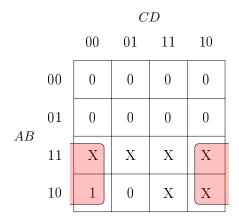

|   |     | 4.5.4   | Don't ca  | re states        |         |                        |                        |      |     | <br>    |     |     |     |     |     | 64               |

|   | 4.6 | Exercis | es        |                  |         |                        |                        |      |     | <br>    |     |     |     |     |     | 65               |

|   |     | 4.6.1   | Converti  | ng formulas, c   | ircuits | , and                  | $\operatorname{truth}$ | tabl | es  | <br>    |     |     |     |     |     | 65               |

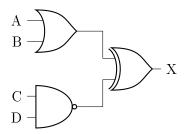

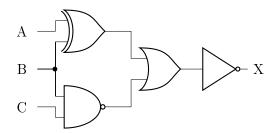

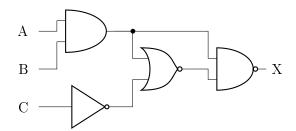

|   |     | 4.6.2   | From cir  | cuit to formula  | a and 1 | $\operatorname{truth}$ | table                  |      |     | <br>    |     |     |     |     |     | 65               |

|   |     | 4.6.3   | Simplifyi | ing Boolean ex   | pressio | ons .                  |                        |      |     | <br>    |     |     |     |     |     | 66               |

|   |     | 4.6.4   | Convert   | to NAND and      | NOR     | gates                  |                        |      |     | <br>    |     |     |     |     |     | 66               |

|   |     | 4.6.5   | Convert   | to NAND and      | NOR     | gates                  |                        |      |     | <br>    |     |     |     |     |     | 67               |

|   |     | 4.6.6   | The norr  | nal form         |         |                        |                        |      |     | <br>    |     |     |     |     |     | 67               |

|   |     | 4.6.7   | PLA       |                  |         |                        |                        |      |     | <br>    |     |     |     |     |     | 68               |

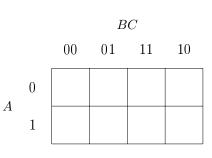

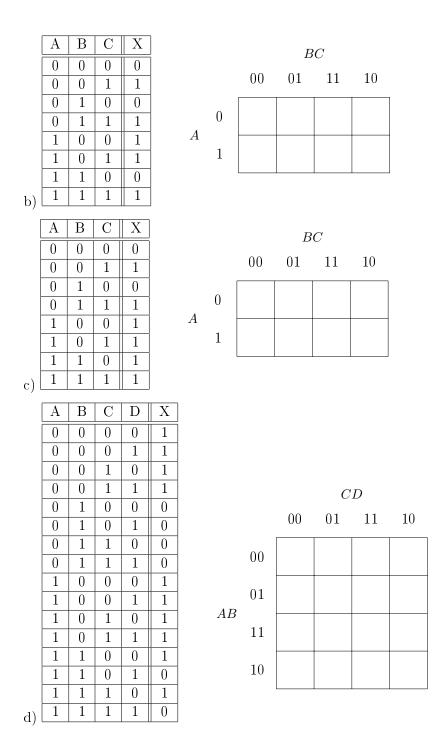

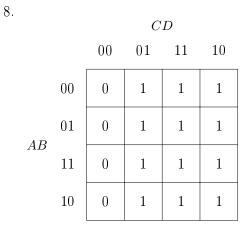

|   |     | 4.6.8   | Karnaug   | h maps           |         |                        |                        |      |     | <br>    |     |     |     |     |     | 68               |

|   |     | 4.6.9   | Karnaug   | h maps           |         |                        |                        |      |     | <br>    |     |     |     |     |     | 69               |

|   |     | 4.6.10  | Don't ca  | re states        |         |                        |                        |      |     | <br>    |     |     |     |     |     | 72               |

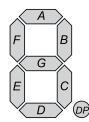

|   |     | 4.6.11  | Display o | driver           |         |                        |                        |      |     | <br>    |     |     |     |     |     | 73               |

| 5 | Con | umon l  | ogic circ | mits             |         |                        |                        |      |     |         |     |     |     |     |     | 74               |

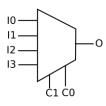

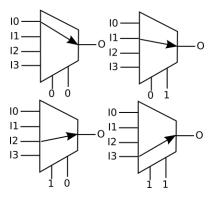

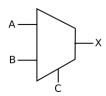

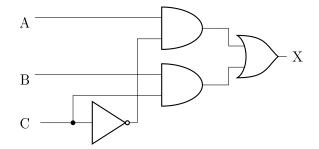

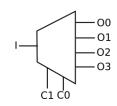

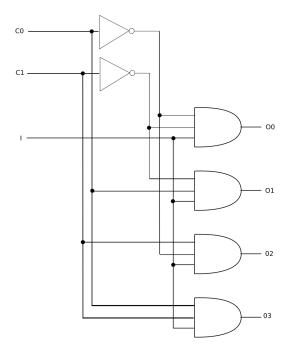

| 0 | 5.1 |         | -         | JX)              |         |                        |                        |      |     |         |     |     |     |     |     | • <b>•</b><br>74 |

|   | 5.2 | -       |           | DEMUX)           |         |                        |                        |      |     |         |     |     |     |     |     | 76               |

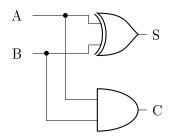

|   | 5.3 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 77               |

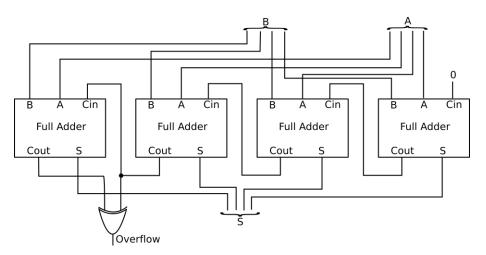

|   | 5.4 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 77               |

|   | 5.5 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 79               |

|   | 5.6 | -       |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 80               |

|   | 0.0 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 80               |

|   |     |         | DEMUX     |                  |         |                        |                        |      |     |         |     |     |     |     |     | 81               |

|   |     |         |           | er               |         |                        |                        |      |     |         |     |     |     |     |     | 81               |

|   |     | 5.6.4   |           | ator             |         |                        |                        |      |     |         |     |     |     |     |     | 81               |

|   |     |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 81               |

|   |     |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     |                  |

| 6 | -   |         | circuits  |                  |         |                        |                        |      |     |         |     |     |     |     |     | 82               |

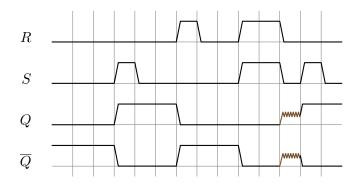

|   | 6.1 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 82               |

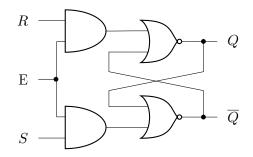

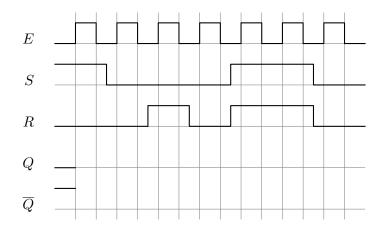

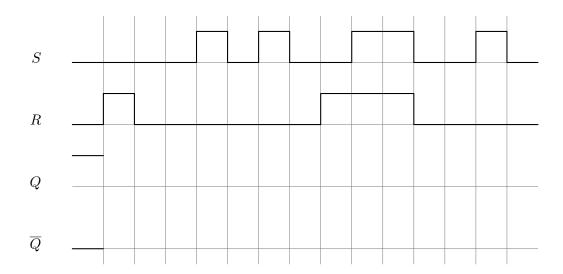

|   | 6.2 | -       |           | s RS-latch       |         |                        |                        |      |     |         |     |     |     |     |     | 84               |

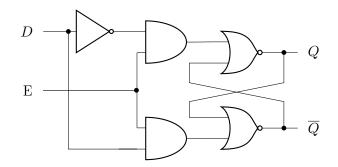

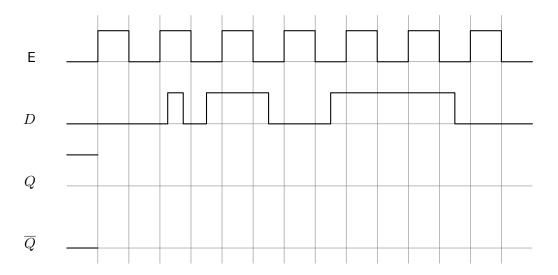

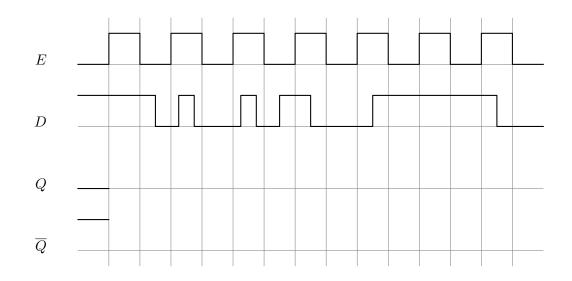

|   | 6.3 |         |           | s D-latch        |         |                        |                        |      |     |         |     |     |     |     |     | 85               |

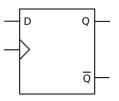

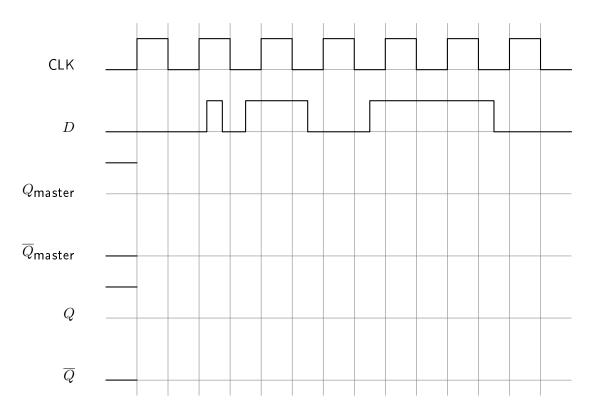

|   | 6.4 |         |           | e D flip-flop .  |         |                        |                        |      |     |         |     |     |     |     |     | 85               |

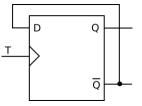

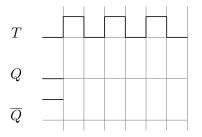

|   | 6.5 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 87               |

|   | 6.6 |         |           |                  |         |                        |                        |      |     |         |     |     |     |     |     | 88               |

|   |     | 6.6.1   |           | latch            |         |                        |                        |      |     |         |     |     |     |     |     | 88               |

|   |     | 6.6.2   |           | nous D-latch .   |         |                        |                        |      |     |         |     |     |     |     |     | 88               |

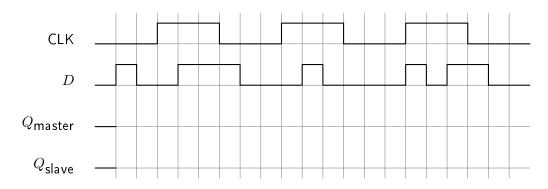

|   |     | 6.6.3   | Master-s  | lave D flip-flop | )       |                        |                        |      |     | <br>    |     | ••• |     |     |     | 89               |

| 7 | Con            | nmon    | sequential circuits                   | 90  |

|---|----------------|---------|---------------------------------------|-----|

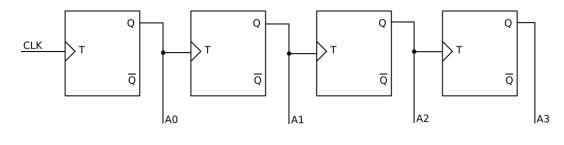

|   | 7.1            | Count   | er                                    | 90  |

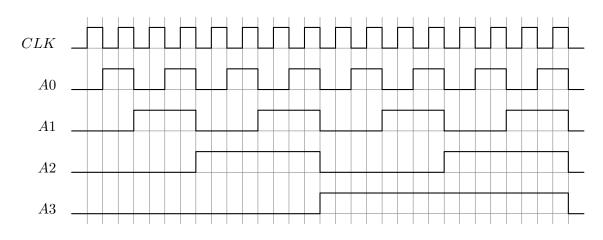

|   | 7.2            | Regist  | ers                                   | 91  |

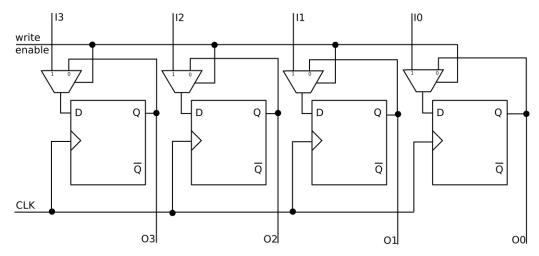

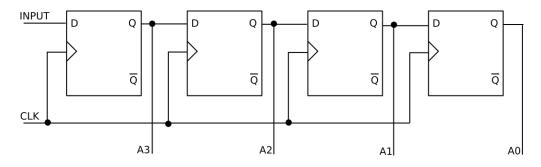

|   | 7.3            | Shift r | egisters                              | 91  |

|   | 7.4            | Exerci  | ses                                   | 92  |

|   |                | 7.4.1   | Simulation                            | 92  |

|   |                | 7.4.2   | Shift register                        | 92  |

|   |                | 7.4.3   | Serial transmitter and receiver       | 92  |

|   |                | 7.4.4   | Bidirectional shift register          | 92  |

|   |                | 7.4.5   | Counter                               | 92  |

| 8 | $\mathbf{Bus}$ | struct  | tures                                 | 93  |

|   | 8.1            | The p   | roblem                                | 93  |

|   | 8.2            | The so  | plution                               | 93  |

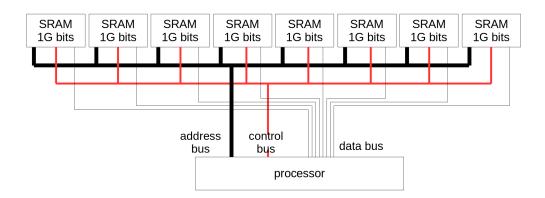

|   | 8.3            | (Statio | c) RAM memory                         | 94  |

|   | 8.4            | Exerci  | ses                                   | 96  |

|   |                | 8.4.1   | Bus architecture                      | 96  |

|   |                | 8.4.2   | Alarm                                 | 96  |

|   |                | 8.4.3   | SRAM                                  | 97  |

| 9 | The            | proce   | essor                                 | 98  |

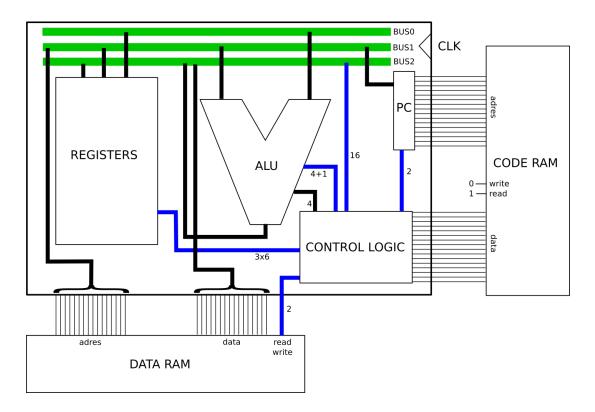

|   | 9.1            | Archit  | ecture                                | 98  |

|   | 9.2            | The in  | nstruction set                        | 100 |

|   | 9.3            | The C   | ompiler                               | 102 |

|   |                | 9.3.1   | Variables and calculations            | 102 |

|   |                | 9.3.2   | Selections                            | 104 |

|   |                | 9.3.3   | Iterations                            | 106 |

|   |                | 9.3.4   | Special constructions                 | 107 |

|   |                |         | 9.3.4.1 Loading big numbers           | 107 |

|   |                |         | 9.3.4.2 Loading negative numbers      | 108 |

|   |                |         | 9.3.4.3 Clearing a register           | 108 |

|   |                |         | 9.3.4.4 Copying a register to another | 109 |

|   |                |         | 9.3.4.5 Manipulating bits             | 109 |

|   |                |         | 9.3.4.6 Multiplication and division   | 110 |

|   | 9.4            | The in  | ternal components                     | 111 |

|   |                | 9.4.1   | The busses                            | 111 |

|   |                | 9.4.2   | The registers                         | 111 |

|        | 9.4.3    | The ALU                                                                                                                                       | 2  |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | 9.4.4    | The control logic                                                                                                                             | 2  |

|        |          | 9.4.4.1 Load instruction $(ld)$                                                                                                               | 3  |

|        |          | 9.4.4.2 A calculation (add) $\ldots \ldots 11$     | 3  |

|        |          | 9.4.4.3 A conditional jump (jpz)                                                                                                              | 4  |

| 9.5    | Exerci   | ses                                                                                                                                           | .4 |

|        | 9.5.1    | Machine language                                                                                                                              | .4 |

|        | 9.5.2    | Executing assembly language 11                                                                                                                | 4  |

|        | 9.5.3    | Write assembly language                                                                                                                       | 6  |

|        | 9.5.4    | Booth's algorithm                                                                                                                             | 7  |

|        | 9.5.5    | Arrays in assembly                                                                                                                            | 8  |

|        | 9.5.6    | Multiplication                                                                                                                                | 8  |

|        | 9.5.7    | Video output                                                                                                                                  | .8 |

|        | 9.5.8    | Subroutines                                                                                                                                   | 9  |

|        | 9.5.9    | Inner workings of the Moncky-1                                                                                                                | 9  |

|        | 9.5.10   | Add an instruction                                                                                                                            | 9  |

| 10 Pro | ctical r | processors 12                                                                                                                                 | 'n |

|        | -        | on Neumann architecture                                                                                                                       |    |

|        |          | Iodified Harvard architecture       12                                                                                                        |    |

|        |          | ers                                                                                                                                           |    |

|        | 0        | 12                                                                                                                                            |    |

|        |          | and Big endian $\ldots$                                      |    |

|        |          | and Digendian $\ldots$                                       |    |

|        |          | 10 pointer $1.12$ $12$                                                                                                                        |    |

|        |          | and RISC processors                                                                                                                           |    |

|        |          | $ \begin{array}{c} \text{ction length} & \dots & $                            |    |

|        |          | cessors                                                                                                                                       |    |

|        |          | processing $\ldots$ $\ldots$ $\ldots$ $12$                                                                                                    |    |

|        |          | $1 \text{ Different modes} \dots \dots$ |    |

|        |          | 2 Hyperthreading                                                                                                                              | 9  |

|        |          | 3 Virtualisation                                                                                                                              | 0  |

| 10.1   |          | instructions                                                                                                                                  | 0  |

|        |          | n hardware                                                                                                                                    | 0  |

|        |          | ng                                                                                                                                            |    |

|        |          | management                                                                                                                                    | 1  |

|        |          | ning $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $13$                                                                                        | 2  |

|        |          |                                                                                                                                               |    |

| 10.17Multi-core processors                                                                                            | 134 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| 10.18Evolution                                                                                                        | 134 |

| $10.19 \operatorname{Exercises}$                                                                                      | 135 |

| 10.19.1 Practical processors                                                                                          | 135 |

| 10.19.2 Moore's law                                                                                                   | 135 |

| $10.19.3 \mathrm{De}80\mathrm{x}86$                                                                                   | 135 |

| 10.19.4 Calculating with 8 bits                                                                                       | 135 |

| $10.19.5$ Assembly language $\ldots$ | 136 |

## Chapter 1

## Numeral systems

In this chapter we will explore how numbers are represented in the computer. In general the binary numeral system is used, but frequently the octal and hexadecimal numeral systems will also be used to enhance human readability.

Further we will explain how to do calculations with binary numbers. It is important to realise that computers can suffer from overflow and rounding errors. This can have an big impact of the accuracy of the calculations.

## **1.1** Representation of numbers

We are so used to read and write numbers that it is hard to imagine that there are other ways to do that. Nevertheless, our way of writing down numbers is not the only possible way. In other times and other cultures different systems are used. However, numbers are always drawn as a sequence of symbols.

The easiest way of representing numbers is by drawing lines. The number 7 would then be written as ||||||||. Since this notation becomes a burden for bigger numbers, other symbols are used to group a number of lines. The Egyptians already had symbols for groups of 5, 10, and 100. This was used by more modern societies. The Romans used V for 5, X for 10, and so on. An important disadvantage of this system is that there is no symbol for zero.

Originally, the order of these symbols did not matter. VII was the same as IVI of IIV. Later, the Romans started to write 4 as IV and since then, the order of the symbols mattered.

#### 1.1.1 The decimal numeral system

In Western culture, the decimal numeral system is used. It consists of 10 symbols (which we call 'digits'): 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. A number is a sequence of those digits. The position of a digit in a number is important. If we write the number 44, the first 4 has a different value than the second 4. The first 4 will count 10 times more than the second one.

If one wants to know the value of a decimal number, the easiest way is to look at the digits from right to left. The most right one is called 'units', the one to the left is called 'tens', then the 'hundreds' are written, and so on. For example, the value of the number '123' is given by  $3 \cdot 1 + 2 \cdot 10 + 1 \cdot 100$ .

The factors we use to multiply each digit are all powers of 10 which is exactly the number of digits in this number system. That is very important.

A more abstract way of looking at the decimal system is as follows. Given a number that consists of digits  $a_4a_3a_2a_1a_0$ , its value is given by:  $a_4 \cdot 10000 + a_3 \cdot 1000 + a_2 \cdot 100 + a_1 \cdot 10 + a_0$ . This can be written shorter:

$$\sum_{i=0}^{4} a_i \cdot 10^i$$

So more in general, the value of a number with n + 1 digits is given by:

$$\sum_{i=0}^{n} a_i \cdot 10^i$$

Another way to look at the decimal numeral system is from the perspective of a counter. When one wants to count in decimal, one starts with all zeros. Imagine, there are 3 digits, then the counter will start with 000. Every time we want to add 1 to this counter, the right-most digit is increased, until there are no more digits left. Thus, the counter will go to 001, 002, 003, all the way till 009. If one wants to add another 1 to this counter, the right-most digit will be set to 0 again and the digit left to it will be increased. This renders 010 and we can count like this until 099 like this. Then, the reasoning is repeated: both 9's are set to 0 and the third digit (from the right) is increased. And so on.

#### 1.1.2 The binary numeral system

Computers work with electrical signals. In order to create a computer that can calculate in the decimal numeral system, one would need 10 different electrical signals. This is not impossible, but very hard to do. Furthermore, such a computer would easily make mistakes as it could misunderstand a signal for another. That is why the binary numeral system was chosen. In this system, only 2 digits are used: 0 and 1. In practice they respond to 2 different voltages.

If there are only 2 digits, a number consists solely of 0's and 1's. In order to know the value of a binary number, one can use powers of 2 in stead of powers of 10. For example, the number 1011 corresponds to (from right to left):  $1 \cdot 1 + 1 \cdot 2 + 0 \cdot 2^2 + 1 \cdot 2^3 = 1 + 2 + 8 = 11$ .

More generally the value of a binary number with digits  $a_i$  is now given by:

$$\sum_{i=0}^{n} a_i \cdot 2^i$$

In order to indicate that the number 1011 is binary, we shall note this as:  $[1001]_2$ . The decimal value can then be written as  $[11]_{10}$ .

As you can see, knowing the powers of 2 can be a great help converting binary numbers into decimal. Complete the following table:

| i | $2^i$ | i  | $2^i$  |

|---|-------|----|--------|

| 0 | 1     | 9  |        |

| 1 | 2     | 10 | 1024   |

| 2 | 4     | 11 |        |

| 3 |       | 12 |        |

| 4 |       | 13 |        |

| 5 |       | 14 |        |

| 6 |       | 15 |        |

| 7 |       | 16 |        |

| 8 | 256   | 17 | 131072 |

Counting in binary is similar to counting in decimal, but now there are only 2 digits. If a counter starts at 000, the next value is still 001. But then, the rightmost digit will go back to 0 and increase the digit next to it. This renders 010 (which is the number 2 in decimal). In the following table, all possible values for this counter are shown:

| binary | decimal |

|--------|---------|

| 000    | 0       |

| 001    | 1       |

| 010    | 2       |

| 011    | 3       |

| 100    | 4       |

| 101    | 5       |

| 110    | 6       |

| 111    | 7       |

As you can see, one needs more digits in binary then in decimal. These digits are also called 'bits'.

#### 1.1.3 The hexadecimal numeral system

Binary numbers can become very lengthy. For instance, the decimal number 1000 needs 10 bits in binary. For humans this can become a problem as it is easy to miss a digit while reading or writing a number it. For this reason the hexadecimal numeral system is used.

In the hexadecimal numeral system there are 16 digits. These are: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. The characters A till F get values 10 till 15 respectively.

In order to find the value of a hexadecimal number, we shall now use powers of 16. For example, the number  $[AF4]_{16}$  is equal to  $4 \cdot 1 + 15 \cdot 16^1 + 10 \cdot 16^2 = 4 + 240 + 2560$  which is  $[2804]_{10}$ .

In general the value of a hexadecimal number with digits  $a_i$  is equal to:

$$\sum_{i=0}^{n} a_i \cdot 16^i$$

The value [AF4]16 will also be written as '0xAF4'. In many programming languages, this notation is used.

It might seem a bit awkward to use 16 digits to write down a number. But in 1.2.3 at page 13 we will explain why this is so useful.

#### 1.1.4 The octal numeral system

In the octal numeral system 8 digits are used. The reasoning is the same as before, which means that the value of an octal number is given by:

$$\sum_{i=0}^{n} a_i \cdot 8^i$$

This system is not used very often, but you will encounter it from time to time. One example is file permissions in Unix. They can also be expressed in the octal numeral system.

#### 1.1.5 Other numeral systems

On could make a numeral system with any number of digits. You just need a finite set of symbols. If there are G symbols, each symbol gets a value 0, 1, ..., G - 1 respectively.

The value of a number with n + 1 digits is now given by:

$$\sum_{i=0}^{n} a_i \cdot G^i$$

For example, take the number 8DH30 in the 18 numeral system. It's value (in decimal) can be determined as follows:

$0 \cdot 1 + 3 \cdot 18 + 17 \cdot 18^2 + 13 \cdot 18^3 + 8 \cdot 18^4 = 54 + 17 \cdot 324 + 13 \cdot 5832 + 8 \cdot 104976 = 921186$

The decimal value of number  $[124]_5$  is given by:

$4 \cdot 1 + 2 \cdot 5^1 + 1 \cdot 5^2 = 4 + 2 \cdot 5 + 1 \cdot 25 = 39$

## 1.2 Conversion

Since we will work with many different numeral systems, it is important to be able to convert numbers to another system.

#### 1.2.1 From any numeral system to decimal

This is very simple and was already discussed before (1.1.5) so we will not repeat that.

#### 1.2.2 From decimal to any other numeral system

What if you start with a decimal number and you want to know it's value in another numeral system (say, binary or hexadecimal)?

In order to do this, we will use an 'algorithm'. This is a step-by-step plan or procedure that one can execute and it will render the right result.

In this case, the algorithm works as follows (we convert a number N to a G-numeral system):

- 1. Divide the number N by G. This results in a quotient (Q), but also a remainder (R). The remainder is what is left if you subtract  $Q \cdot G$  from the N.

- 2. Write down the value of R. This is a digit of the number we are looking for.

- 3. If Q is greater than 0, go back to step 1, but use the value of Q (in stead of N).

- 4. If you reverse all the digits found, that will result in the value we are looking for.

An example is given to clarify this. Imagine you want to convert the number  $[1234]_{10}$  to hexadecimal notation (N=1234 and G=16).

Starting in step 1, we divide 1234 by 16. This gives 77 and the remainder is  $2 (= 1234 - 16 \cdot 77)$ . Since 77 is greater than 16, we divide it again by 16. Now the result is 4 and the remainder is 13. If we divide the last result by 16, we get 0 and a remainder of 4. Now the algorithm stops because the quotient was 0. We found the remainders 2, 13, and 4 consecutively. If we reverse this, we get 4, 13, and 2. The number 13 is written by the digit 'D' in hexadecimal. So the result is: [4D2]16.

We can verify if this is correct by converting this number back to decimal:  $2+13\cdot16+4\cdot16^2 = 1234$ . In order to make this conversion a bit more easy on paper, one can use the following scheme:

We start on the top left. The quotient is always written under the previous result. And the remainder is written on the right. The digits are all on the right from bottom to top.

This technique can be used to convert from decimal to any other numeral system. We could also convert the number 1234 to the 5 numeral system. This gives:

| 1234 | 4 |

|------|---|

| 246  | 1 |

| 49   | 4 |

| 9    | 4 |

| 1    | 1 |

| 0    |   |

Hence, the result is: [14414]5.

And if the number is converted to binary, we get:

| 1234 | 0 |

|------|---|

| 617  | 1 |

| 308  | 0 |

| 154  | 0 |

| 77   | 1 |

| 38   | 0 |

| 19   | 1 |

| 9    | 1 |

| 4    | 0 |

| 2    | 0 |

| 1    | 1 |

| 0    |   |

|      |   |

And the result is:  $[100 \ 1101 \ 0010]_2$ .

Notice that all digits are always smaller than G. There can never be digits higher or equal to G.

#### 1.2.3 Binary and hexadecimal

The hexadecimal numeral system has a very interesting property. It allows easy conversion to binary and vice versa. Let's explore this with an example.

In this example we start from the decimal number [40102]10. If we convert this to hexadecimal and to binary, we get [9CA6]16 and [1001 1100 1010 0110]2 respectively.

Notice that we grouped the bits in groups of 4. Each group of 4 bits can be converted to hexadecimal separately and it will give the same result:

- $[1001]_2 = [9]_{10} = [9]_{16}$

- $[1100]_2 = [12]_{10} = [C]_{16}$

- $[1010]_2 = [10]_{10} = [A]_{16}$

- $[0110]_2 = [6]_{10} = [6]_{16}$

This means it is very simple to convert between binary and hexadecimal numeral systems. Just group the bits per four and convert them separately. There is no need to go through the decimal system if you know all 16 possibilities of 4 bits by heart. Complete the next table which gives all possible combinations of 4 bits:

| 0 | 0000 | 4 |      | 8 | 1000 | С |      |

|---|------|---|------|---|------|---|------|

| 1 | 0001 | 5 | 0101 | 9 |      | D | 1101 |

| 2 |      | 6 |      | Α |      | Е |      |

| 3 |      | 7 |      | В |      | F | 1111 |

Hexadecimal numbers are used a lot. In fact they are a short, more readable version of binary numbers. You will see them being used for memory addresses, characters, mac addresses, machine code, ...

In the same way, it is also easy to convert between the octal and the binary system. In this case, you group the bits by 3 (because  $2^3 = 8$ ).

## 1.3 Negative numbers

The memory of a computer consists of a very long sequence of bits. A memory of 16GB consists of 137 438 953 472 bits! Each of those bits can be 0 or 1. These bits are grouped per 'byte' (8 bits) of per multiple of bytes (1, 2, 4 or 8 bytes). Each group can then be used to store a number. For instance, if you write the following code in java:

#### int a = 100;

the computer will use 4 bytes (32 bits) in memory to store the value of a. The contents of those bits will be 0000 0000 0000 0000 0000 0110 0100. Notice that by using a fixed number of bytes, some numbers will not fit into this space. That is why every type in java has a certain 'range'. More information can be found in 1.4.1.

A positive number is thus easily stored in a group of bytes. But what if we want to store negative numbers? On paper we can just write a '-' sign in front, but in the memory of the computer there is only 0 and 1. That means we have to use some system to indicate that the number is negative. There are different ways to do this and they will be discussed in this section.

It is important to see that, given a certain amount of bits, one cannot know if this represents a positive or a negative value if you don't know which system was used. We will demonstrate this below, but it is already important to notice this. In programming languages, one defines the used system by specifying the 'type' of a variable (int, char, byte, ...). More information can also be found in 1.4 on page 19.

There are different ways to encode a negative number into bits. For every possibility, the following has to be taken into account:

• How many numbers can we represent with the given number of bits?

- How many negative and how many positive numbers can we represent?

- Are there multiple ways to represent the same number (preferably not)?

- Does the order of the numbers change when we regard the numbers as natural numbers?

- Is it easy to calculate when the numbers are represented a certain way?

We discuss four ways to represent negative numbers:

- sign bit: this will be used in chapter 2 on page 36

- 1-complement: this is not used a lot, but a great introduction to 2-complement

- 2-complement: this is the most used format to represent integers

- offset: this will be used in chapter 2 on page 36

#### 1.3.1 Sign bit

Sign bit is the simplest way to format integers. It just uses 1 bit for the sign. For instance, if a value needs to be stored in 4 bytes, the first bit is reserved to hold the sign. A zero means that the number is positive, a 1 means it is negative. The remainder 31 bits can then be used for the value.

So in order to be able to store negative numbers, one bit is sacrificed. One can still store positive numbers, but the range is smaller (it is halved). In exchange negative numbers can also be stored.

The advantage of this system is that it comes very close to how humans write numbers. But there are also a number of disadvantages. For instance, one can write 0 in 2 ways: +0 and -0. Also, doing calculations is more difficult because one always has to check the sign. If you want to add 2 numbers, but one is negative, you should subtract them.

A simple example will clarify this system a bit further. Imagine one wants to store the number [-100]10 to sign bit notation with 8 bits. In order to do this, we convert [100]10 to binary, yielding [110 0100]2. After this, the first bit is set to 1. The final result is then: 1110 0100.

Remark that one could also interpret this number as a positive value (when you don't know it was constructed with sign bit). In this case the value can be read as [228]10. It is therefore very important to make sure you know the format that was used! In some programming languages this is achieved by specifying the type of a variable (like 'int' and 'unsigned' in the C programming language).

By the way, remark that the positive value [100]10 is also representable with sign bit. The sign bit is in this case equal to 0. This results in: 0110 0100.

As a last example, all possible values of 3 bits are shown, together with their 'unsigned' value and the value using sign bit:

| bit pattern | unsigned | sign bit |

|-------------|----------|----------|

| 000         | 0        | +0       |

| 001         | 1        | 1        |

| 010         | 2        | 2        |

| 011         | 3        | 3        |

| 100         | 4        | -0       |

| 101         | 5        | -1       |

| 110         | 6        | -2       |

| 111         | 7        | -3       |

As you can see, there are 2 possible ways to represent 0. Also, the order of the numbers interrupts between 3 and -0 and then reverses after that. There are, in fact, 2 jumps in the numbers. The first one is when the value goes from 3 to -0 and the second one happens when you add 1 to the last number. Since there are only 3 bits, all bits will flip back to 0. But the sign bit value jumps more than one (it goes from -3 to +0). We call these jumps also 'discontinuities'. Discontinuities make it difficult to do calculations with the numbers (more information will follow).

Generally, we get the following results using sign bit with n bits:

- there are  $2^n 1$  different values possible

- the range goes from  $-2^{n-1} + 1$  (all ones) till  $2^{n-1} 1$  (a zero followed by all ones)

- the number zero has two representations: all zeros or a one followed by all zeros

- the order of the numbers changes when you look at the numbers as being unsigned (all negative numbers are in reverse order).

- in order to do arithmetic operations on the numbers, one needs to take into account the sign

## 1.3.2 1-complement

Another system to encode negative numbers is 1-complement. In this representation a negative number is stored as the inverted version of its positive value. The inverted is found by flipping all bits (all ones become zero and vice versa). The first bit is not used to store the number. As a consequence one can still use this bit to determine if the value is negative or positive.

For example, the number [-100]10 will be represented with 8-bits 1-complement as follows. First, 100 is converted to binary (8 bits), resulting in: [0110 0100]2. Then all bits are inverted. This yields: 1001 1011 which is stored in memory.

With this technique one can still determine the sign of the number looking at the first bit. For example, if 1111 0101 is stored in memory, the first bit indicates that this is a negative number. In order to find its positive value, all bits need to be inverted. This results in 0000 1010 which is the binary representation of the number decimal number 10. Therefore, the stored number is equal to [-10]10.

Positive numbers are still stored as before, but the first bit cannot be used. For example the stored value  $0110\ 1000$  is just  $[104]_{10}$ .

If we put all possible values of 3 bits in a table, the following result is found:

| bit pattern | unsigned | 1-complement |

|-------------|----------|--------------|

| 000         | 0        | +0           |

| 001         | 1        | 1            |

| 010         | 2        | 2            |

| 011         | 3        | 3            |

| 100         | 4        | -3           |

| 101         | 5        | -2           |

| 110         | 6        | -1           |

| 111         | 7        | -0           |

There are still 2 discontinuities (between 3 and -3, and between -0 and +0). The following properties hold:

- there are  $2^n 1$  different values possible

- the range goes from  $-2^{n-1} + 1$  (a one followed by all zeros) till  $2^{n-1} 1$  (a zero followed by all ones)

- the number zero still has two representations: all zeros or all ones

- the order of the numbers is better than with sign bit (all negative numbers are now in the right order)

- in order to do arithmetic operations on the numbers, one still needs to take into account the sign

#### 1.3.3 2-complement

One of the problems with the previous formats is the presence of two representations for 0. If you look closely at the 3-bit example in 1-complement, these two 0's are next to each other (if you add 1 to all ones, you end up with all zeros). Therefore, it would be interesting to shift all negative numbers one row down (111 will become -3 in this case). This has two advantages: the value of -0 disappears and it creates room for another number. The bit-pattern 100 can now be 4 or -4. Although one might be tempted to assign the number 4 to that pattern, in reality it is regarded as -4. In this way negative numbers can still be recognised by the first bit.

The resulting table with 3-bit patterns now becomes:

| bit pattern | unsigned | 2-complement |

|-------------|----------|--------------|

| 000         | 0        | 0            |

| 001         | 1        | 1            |

| 010         | 2        | 2            |

| 011         | 3        | 3            |

| 100         | 4        | -4           |

| 101         | 5        | -3           |

| 110         | 6        | -2           |

| 111         | 7        | -1           |

This is the 2-complement notation. So in order to represent a negative number, the positive value is still inverted, but also increased with 1. Positive numbers are still stored as before. For example, the number [-100]10 will be constructed as follows (again 8 bits as in the previous sections). The binary value of [100]10 was [0110 0100]2. In order to change this into -100, all bits are inverted and 1 is added to it. This results in: 1001 1100.

This technique (taking the inverted and adding one) is also called calculating 'the 2-complement of a value'. It has an interesting property: if you apply it twice, you end up with the original number. For example, if you start with 1001 1100 ([-100]10) and take its 2-complement, one finds 0110 0100 which is [100]10 again.

Another interesting property of 2-complement notation is that one can do calculations with it without taking into account negative numbers. This is discussed more in detail in section 1.6 on page 26. A small example will already give some insight. Imagine one wants to calculate  $[-1 + 2]_{10}$  using the 3 bits representation as in the table. In memory these numbers are stored as  $[111]_2$  and  $[010]_2$ . If we regard these numbers as positive integers, they have values 7 and 2. Adding those to yields 9, which is  $[1001]_2$  in binary. Since there are only 3 bits allowed, we delete the first bit and end up with  $[001]_2$ . This result is correct! This means we can do calculations with

negative numbers without having to take that into account at all (more information in 1.6). This is why 2-complement is the most used representation in computer science.

In short we find the following properties for 2-complement:

- there are  $2^n$  different values possible

- the range goes from  $-2^{n-1}$  (a one followed by all zeros) till  $2^{n-1} 1$  (a zero followed by all ones)

- the number zero only has one representation: all zeros

- the order of the numbers is always preserved, except when the value goes from the highest value to the lowest

- in order to do arithmetic operations on the numbers, one can do those as if they were just positive integers

## 1.3.4 Offset

A fourth way to represent negative numbers is completely different. In order to be able to store negative numbers, a constant value (called the 'offset') is added to each number (also the positive ones). In other words, all numbers are shifted to a higher value. That value is stored in binary. In order to decode a stored value, one has to subtract the offset to obtain the original value.

The value of the offset is fixed and must be given. Otherwise it is impossible to know how to store values or to know which value was stored in memory.

Let's take the example we used before. We want to store the value [-100]10 with 8 bits and an offset of 127. In this case, we add -100 and 127, resulting in 27. This is converted to binary with eight bits, yielding: 0001 1011. So the idea is to make all numbers positive so they can be stored like that. Remark that the first bit does not give any information about the sign any more!

If you want to represent +5 in the same format (8 bits, offset=127), then these two values are also added. This gives 132 and yields 1000 0100 when converted to binary.

When decoding the offset needs to be subtracted. For instance if the pattern 0011 1111 was encoded with an offset of 127, one converts the number first to decimal: [63]10. Then the offset is subtracted to obtain the value: 63 - 127 = -64.

The advantage of this technique is that one can choose how many negative and positive numbers are representable. The disadvantage is that the number 0 is not encoded as all zeros.

With 3 bits and an offset of 3, one gets the following table:

| bit pattern | unsigned | offset |

|-------------|----------|--------|

| 000         | 0        | -3     |

| 001         | 1        | -2     |

| 010         | 2        | -1     |

| 011         | 3        | 0      |

| 100         | 4        | 1      |

| 101         | 5        | 2      |

| 110         | 6        | 3      |

| 111         | 7        | 4      |

The offset method has the following properties:

- there are  $2^n$  different values possible

- the range goes from -offset (all zeros) till  $2^n 1 \text{offset}$  (all ones)

- the number zero only has one representation: the binary representation of the offset

- the order of the numbers is preserved

- in order to do arithmetic operations on the numbers, one has to take into account the offset

## 1.4 The binary system in IT

As discussed before binary numbers are extremely important in the world of IT. All information is stored in memory using the binary numeral system. Every digit is called a 'bit' which is an abbreviation of 'binary digit'.

The memory of a computer (internal RAM, disk space, USB drives, ...) consists of billions of bits. Those bits are grouped per 8. Each group is called a 'byte'. One can also make groups of 16, 32 or 64 bits. In this case, the word 'word' is used to indicate such a group.

Since groups of 4 bits also make sense (because there is a link with hexadecimal), they also received a name. A group of 4 bits is called a 'nibble'.

When storing numbers in memory, the computer will always reserve a number of bytes for it. This means that the range of the number is always limited.

## 1.4.1 Data types in java

Java defines different types for variables. Depending on the type, a different amount of bytes is reserved in memory. For integer types java always uses 2-complement notation. The following table shows these types:

| name  | number of bytes | range                                                     |

|-------|-----------------|-----------------------------------------------------------|

| byte  | 1               | -128 till 127                                             |

| short | 2               | -32 768 till 32 767                                       |

| int   | 4               | -2 147 483 648 till 2 147 483 647                         |

| long  | 8               | -9 223 372 036 854 775 808 till 9 223 372 036 854 775 807 |

If one wants to store a number that is outside the range of a given type, the number is truncated. This situation is called 'overflow'. The programmer will not always get an error!

In java there is no 'unsigned' version of the data types. Programming languages such as C do have that.

## 1.4.2 Converting numbers using java

In java one can easily convert numbers to another numeral system using the static method Integer.toString(i, r). The number that needs to be converted is i and r is the number of digits in the other numeral system.

The following static methods can also be useful: Integer.toBinaryString(i), Integer.toHexString(i), Integer.toUctalString(i). The class Long also contains these methods.

#### 1.4.3 Literals in Java

In java one can define constant values in different ways. Normally the numbers are always in the decimal numeral system. However, it is also possible to give a value (also called a 'literal') in binary, hexadecimal or octal. This is done as follows:

Note that octal number start with a 0. So never use decimal values with leading zeros in java. They will be interpreted as octal values!

#### 1.4.4 Units

Because computers use the binary system, powers of 2 are also important.

This was already clear because bits are grouped in groups of 4, 8, 16, 32 or 64 bits. For larger amount of bits (or bytes), powers of two are also used.

For instance, 1024 bytes  $(2^{10})$  is called a 'kilobyte'. The word 'kilo' does not mean 1000 in this case! In the following table you can see how many bytes are in each case:

| name  | abbreviation | amount                            |

|-------|--------------|-----------------------------------|

| kilo  | K            | 1 024                             |

| mega  | М            | $1 \ 048 \ 576$                   |

| giga  | G            | $1\ 073\ 741\ 824$                |

| terra | Т            | $1 \ 099 \ 511 \ 627 \ 776$       |

| peta  | Р            | $1 \ 125 \ 899 \ 906 \ 842 \ 624$ |

Due to commercial reasons, one kilo will sometimes be used to indicate 1000, which is even more confusing. A hard disk with a capacity of 1 TB should normally contain 1,099,511,627,776 bytes, but in practice there are only 1,000,000,000. A difference of almost 100 GB!

Network speeds are also given in powers of 10. A network with 1 Mbps will send 1 000 000 bits per second.

In order to overcome the confusion between powers of 2 and powers of 10, new names were introduced. They are used more and more frequently. For example, 1024 bytes is called a 'kibibyte'. If you see these names, you know it is expressed in powers of 2.

The following names are used for powers of 2:

| name | abbreviation | amount                            |

|------|--------------|-----------------------------------|

| kibi | Ki           | 1 024                             |

| mebi | Mi           | $1 \ 048 \ 576$                   |

| gibi | Gi           | $1\ 073\ 741\ 824$                |

| tebi | Ti           | $1 \ 099 \ 511 \ 627 \ 776$       |

| pebi | Pi           | $1 \ 125 \ 899 \ 906 \ 842 \ 624$ |

## 1.4.5 MSB en LSB

The abbreviations MSB and LSB are very important if you want to name certain parts of a binary number. MSB stands for 'Most Significant Bits' or 'Most Significant Bytes' (depending on the context). LSB stands for 'Least Significant Bits' or 'Least Significant Bytes'.

When sign bit was discussed, we talked about the 'first' bit of the number. But this is very ambiguous. We look at these numbers frequently from right to left, so what is then the first bit? We could also call it the 'left most' bit, but then bits are stored on 2 dimensional chips. There is no left and right there. In order to be clear, this bit is called the MSB because the weight (significance) of that bit in the number is the highest.

So if one considers the number [1110 0100 1001 1011]2, the MSB is equal to one. The 4 MSB are equal to 1110. You can also say that the MSB is equal to 1110 0100. In the latter case the 'B' stands for 'byte'.

The LSB of the previous number is equal to 1, the 4 LSB are equal to 1011 and the LSB is equal to 1001 1011.

In the remainder of this course text MSB and LSB will always be used.

## 1.4.6 Little endian and big endian

As explained before numbers are stored in a number of consecutive bytes in memory. Every byte has an 'address' in memory. This means every byte has a location, which can also be expressed as a number.

For example a 32 bit integer will be stored in 4 bytes. The first byte is e.g. stored at location 0xC000, the second at location 0xC001, the third at location 0xC002 and the last at location 0xC003 (remark that we use hexadecimal numbers which is custom for memory locations).

But this can still be done in 2 ways: one can start with the MSB and then go to the LSB. Or one could start with the LSB. The latter is probably counter intuitive, but it is the most used way to store (and also send) numbers.

If a number is stored starting with the MSB, this is called 'big endian'. If one starts with the LSB, this is called 'little endian'.

This means that the 32-bit integer with value 0x12345678 is stored as follows:

- big endian: 0x12, 0x34, 0x56, 0x78

- little endian: 0x78, 0x56, 0x34, 0x12

Every processor has his own way to store numbers in memory. So it becomes very important to know this when computers are connected through a network. If they send a number with little endian of big endian can make a big difference.

Most computers these days use little endian to store numbers in memory. But to send them over a network, big endian is used more frequently.

## 1.5 Characters

Computers not only work with numbers. They also have to store texts which consist of characters. Characters must be converted to bits somehow. This is usually done with a table. The table maps all characters to a number. That number can then be stored in memory.

Through history many different tables have been used to associate characters with numbers. Therefore, one needs to make sure which table was used in order to interpret a text that was stored in memory. For example, the character 'A' can be represented by the number 65 in one table. But in another table it might get the number 193.

Notice that, next to having a table, one also needs to determine how to 'encode' the number into bits. If the numbers are always between certain borders, a fixed number of bits can be used. But numbers of characters can also be encoded in a variable amount of bits. This is discussed more in detail in 1.5.5.

## 1.5.1 Legacy systems

In the early days, the most used character set was called EBCDIC (Extended Binary Coded Decimal Interchange Code). This system is not used a lot any more. But it can still be encountered on some mainframes that are programmed in COBOL.

In this system, every character gets a value between 0 en 255. Therefore, each character can be encoded into 1 byte of memory.

The big disadvantage of this system is that characters are not put alphabetically in the table. This makes it difficult to sort words for instance.

## 1.5.2 ASCII

In the sixties a new character set emerged: the ASCII set (American Standard Code for Information Interchange). This character set contains 128 characters, so 7 bits are needed to represent a character. The table only contains characters that are used in the English language. Therefore, it was unsuitable for other languages.

The ASCII table is shown here:

|   | 0 | 1 | 2 | 3 | 4  | 5 | 6 | 7 | 8                      | 9             | Α             | В | С | D                       | Е | F |

|---|---|---|---|---|----|---|---|---|------------------------|---------------|---------------|---|---|-------------------------|---|---|

| 0 |   |   |   |   |    |   |   |   | $\setminus \mathbf{b}$ | $\setminus t$ | $\setminus n$ |   |   | $\backslash \mathbf{r}$ |   |   |

| 1 |   |   |   |   |    |   |   |   |                        |               |               |   |   |                         |   |   |

| 2 |   | ! | " | # | \$ | % | & | , | (                      | )             | *             | + | , | -                       |   |   |

| 3 | 0 | 1 | 2 | 3 | 4  | 5 | 6 | 7 | 8                      | 9             | :             | ; | < | =                       | > | ? |

| 4 | 0 | А | В | С | D  | Е | F | G | Η                      | Ι             | J             | K | L | M                       | Ν | 0 |

| 5 | Р | Q | R | S | Т  | U | V | W | Х                      | Y             | Z             | [ | \ | ]                       | ^ | _ |

| 6 | " | а | b | с | d  | е | f | g | h                      | i             | j             | k | 1 | m                       | n | 0 |

| 7 | р | q | r | s | t  | u | v | w | х                      | У             | z             | { |   | }                       | ~ |   |

The row number is octal and the column number is hexadecimal. The row specifies the 3 MSB of the number and the column specifies the 4 LSB of the number. Therefore, the character 'A' is associated with the binary number 100 0001 ([41]  $_{16}$ ).

The first 32 entries in the table are special characters like backspace, tab, newline, and carriage return. There are other characters that were used to indicate certain events when characters need to be sent over a network. We will not discuss these special characters here as they are barely used any more. Character 32 ( $[20]_{16}$ ) is a space.

There are a few interesting advantages about the ASCII set. First of all, the characters are alphabetically ordered. This means that the associated number can be used to determine if a character should come before of after another one (alphabetically). Capital characters are first

in the table. This is the reason why a lot of applications tend to always sort capital characters first.

A second advantage is that it is very easy to convert capital characters to lower case and vice versa. You just need to set one bit to 1 or 0 in order to do this. This can also be accomplished by adding or subtracting 32 from the number.

## 1.5.3 ISO 8859

ASCII characters are normally encoded in 8 bits. This means that the MSB is always 0. This bit is used to add other characters to the set. For instance, in order to write Latin languages such as French or Spanish, the set was extended with the following set:

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α        | В | С             | D             | Ε             | F  |

|---|---|---|---|---|---|---|---|---|---|---|----------|---|---------------|---------------|---------------|----|

| 8 |   |   |   |   |   |   |   |   |   |   |          |   |               |               |               |    |

| 9 |   |   |   |   |   |   |   |   |   |   |          |   |               |               |               |    |

| A |   | i | ¢ | £ | Ø | ¥ |   | § |   | C | <u>a</u> | « | -             |               | R             | -  |

| B | 0 | Ŧ | 2 | 3 | 1 | μ | P | • | د | 1 | Q        | > | $\frac{1}{4}$ | $\frac{1}{2}$ | $\frac{3}{4}$ | i  |

| C | À | Á | Â | Ã | Ä | Å | Æ | Ç | È | É | Ê        | Ë | Ì             | Í             | Î             | Ï  |

| D | Ð | Ñ | Ò | Ó | Ô | Õ | Ö | × | Ø | Ù | Ú        | Û | Ü             | Ý             | Þ             | ſŜ |

| Е | à | á | â | ã | ä | å | æ | Ç | è | é | ê        | ë | ì             | í             | î             | ï  |

| F | ð | ñ | ò | Ó | Ô | õ | ö | ÷ | ø | ù | ú        | û | ü             | ý             | þ             | ÿ  |

This extension enables to write in a lot of languages such as Afrikaans, Albanian, Icelandic, Indonesian, Italian, Norwegian, Portuguese, Scottish, Spanish, Swahili, Swedish, and others. This set is called 'Latin-1' or 'ISO 8859-1' and is widely adopted.

However, there are a lot of characters not present in this set. If one wants to write a Russian text, for instance, another extension is needed. The Cyrillic characters have been put in an extension called 'Latin/Cyrillic' or 'ISO 8859-5'.

This means that you need to know the language in which a text was written, so one can use the right table to decode the characters. Another disadvantage is that it is impossible to mix certain languages in one document. For these reasons, the ISO 8859 standard was slowly abandoned and replaced by Unicode. However, some operating systems like Windows still support the ISO 8859 standard and can create a lot of confusion in an international context.

## 1.5.4 Unicode: code points

Exchanging information in an international context is key in our modern society. The ASCII data set and its extensions are not adequate. This is why another standard emerged in the nineties: 'Unicode' or 'ISO 10646'.

Unicode is also a table of characters, but there is no limit on how far it may grow. Every number associated with a character is called a 'code point'. In 2018 the largest code point had a value of 0x1FA6D, but new characters have been added since then. Unicode has characters for almost any language.

The first 128 code points correspond to the ASCII set. Code points are always noted in the same way: a capital 'U' followed by a 'plus'-sign followed by the hexadecimal value of the code point with at least 4 digits. For example, the word 'Hello' has the following code points:

U+0048 U+0065 U+006C U+006C U+006F

Since code points don't have a maximum value, storing them in a fixed number of bytes will result in loss of range. Therefore, more complicated encodings are used (such as UTF-8). They are described below.

## 1.5.5 Unicode: encodings

Code points need to be stored in memory and in files, which consist of bytes. Code points are therefore 'encoded' in those bytes. The UTF-8 encoding is probably the most used, but there are other ways as well.

## 1.5.5.1 UCS

A simple method to encode code points is to use a fixed number of bytes. In the early days of Unicode, people still believed that code points would not easily exceed the range of a 16 bit number. That is why people started to store each character in exactly 2 bytes. Java uses this encoding internally for the 'char' type.

This encoding is also known as 'UCS-2' (Universal Character Set). For example, the word 'Hello' could be encoded as the following consecutive bytes in a file (in hexadecimal):

#### 00 48 00 65 00 6C 00 6C 00 6F