# X1000

# **IoT Application Processor**

**Programming Manual**

Release Date: Jan. 13, 2016

**X1000 IoT Application Processor**

**Programming Manual**

Copyright © 2005-2016 Ingenic Semiconductor Co. Ltd. All rights reserved.

**Disclaimer**

This documentation is provided for use with Ingenic products. No license to Ingenic property rights is granted. Ingenic assumes no liability, provides no warranty either expressed or implied relating to the usage, or intellectual property right infringement except as provided for by Ingenic Terms and

Conditions of Sale.

Ingenic products are not designed for and should not be used in any medical or life sustaining or

supporting equipment.

All information in this document should be treated as preliminary. Ingenic may make changes to this document without notice. Anyone relying on this documentation should contact Ingenic for the current

documentation and errata.

Ingenic Semiconductor Co., Ltd.

Ingenic Headquarters, East Bldg. 14, Courtyard #10, XIbeiwang East Road, Haidian District, Beijing 100193, China,

Tel: 86-10-56345000 Fax: 86-10-56345001

Http://www.ingenic.com

# **CONTENTS**

| CONTE  | NTS                            | i  |

|--------|--------------------------------|----|

| TABLES | S                              | i  |

| FIGURI | ES                             | i  |

|        | Section 1 Overview             |    |

| 1 Ove  | rview                          | 2  |

|        | Block Diagram                  |    |

|        | Features                       |    |

| 1.2.1  | CPU Core                       |    |

| 1.2.1  | Image Core                     |    |

| 1.2.3  | Display/Camera/Audio           |    |

| 1.2.4  | Memory Interface               |    |

| 1.2.5  | System Functions               |    |

| 1.2.6  | Peripherals                    |    |

| 1.2.7  | Bootrom                        | 9  |

| 2 CPU  | Section 2 Core Functions       | 11 |

| 2.1 E  | Block Diagram                  | 11 |

| 2.2 E  | Extra Features of the CPU core | 13 |

| 2.3 lı | nstruction Cycles              | 13 |

| 2.4 F  | PMON                           | 16 |

| 2.4.1  | Fundamental                    | 17 |

| 2.5 F  | Partial Kernel Mode            | 17 |

|        | Section 3 Image Core           |    |

| 3 JPE  | G                              | 19 |

| 3.1 C  | Overview                       | 19 |

| 3.2 F  | Register Definition            | 19 |

| 3.2.1  | Task trigger (TRIG)            |    |

| 3.2.2  | VDMA status (STAT)             | 20 |

| 3.2.3  | Global control information     | 20 |

| 3.2.4  | JPGC trigger                   | 21 |

| 3.2.5  | JPGC Status                    | 22 |

| 3.2.6  | Bitstream buffer address       | 22 |

| 3.2.         | .7 Component 0 plane buffer address        | 23                   |

|--------------|--------------------------------------------|----------------------|

| 3.2.         | 8 Component 1 plane buffer address         | 23                   |

| 3.2.         | 9 Component 2 plane buffer address         | 24                   |

| 3.2.         | 10 Component 3 plane buffer address        | 24                   |

| 3.2.         | 11 MCU number                              | 25                   |

| 3.2.         | 12 Re-Sync-Marker gap number               | 25                   |

| 3.2.         | 1 9                                        |                      |

| 3.2.         | 14 EFE control                             | 26                   |

| 3.2.         | 15 Encoder slice geometry information      | 26                   |

| 3.2.         | 16 RAW plane source buffer address         | 27                   |

| 3.2.         | 17 RAW destination buffer basement address | 27                   |

| 3.2.         | 18 RAW plane stride                        | 28                   |

| 3.3          | Table definition                           | 28                   |

| 3.3.         | 1 Huffman Base Table                       | 28                   |

| 3.3.         | 2 Huffman MIN Table                        | 28                   |

| 3.3.         | 3 Quantization Table                       | 28                   |

| 3.3.         | 4 Huffman Symbol Table                     | 29                   |

| 3.3.         | 5 Huffman ENC Table                        | 29                   |

|              | Section 4 Display/Camera/Audio             |                      |

|              | Godion i Biopiay/Gamera/Addio              |                      |

| 4 SL         | .CD Controller                             | 31                   |

| 4.1          | Overview                                   | 31                   |

| 4.2          | Pin Description                            |                      |

| 4.3          | Block Diagram                              |                      |

| 4.4          | Register Description                       |                      |

| 4.4.         | -                                          |                      |

| 4.4.         | ,                                          |                      |

| 4.4.         | ·                                          |                      |

| 4.4.         | ,                                          |                      |

| 4.4.         | ,                                          |                      |

| 4.4.         |                                            |                      |

| 4.4.         | · ·                                        |                      |

| 4.4.         | · · ·                                      |                      |

| 4.4.         |                                            |                      |

| 4.4.         |                                            |                      |

| 4.4.         | ,                                          |                      |

| 4.4.         | .11 Interrupt ID Register (LCDIID)         |                      |

| 4.4.         | ,                                          |                      |

|              | 12 Descriptor Address Registers (LCDDAx)   | 40                   |

| 4.4.         | 12 Descriptor Address Registers (LCDDAx)   | 40<br>41             |

| 4.4.<br>4.4. | 12 Descriptor Address Registers (LCDDAx)   | 40<br>41<br>42       |

|              | 12 Descriptor Address Registers (LCDDAx)   | 40<br>41<br>42       |

| 4.4.         | 12 Descriptor Address Registers (LCDDAx)   | 40<br>41<br>42<br>42 |

| 4.4.18  | DMA Commend Counter Registers (LCDCNUMx)              | 44 |

|---------|-------------------------------------------------------|----|

| 4.4.19  | DMA Commend Counter Registers (LCDCPOSx)              | 44 |

| 4.4.20  | Foreground x Size in Descriptor (LCDDESSIZEx)         | 45 |

| 4.4.21  | Priority level threshold configure Register (LCDPCFG) | 45 |

| 4.4.22  | LCD Arbiter Priority(LCD_PCFG_ARB)                    | 46 |

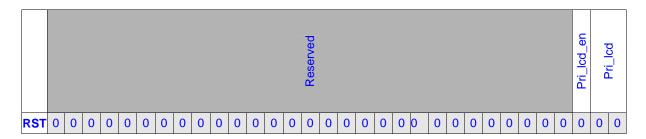

| 4.4.23  | SLCD Configure Register (MCFG)                        | 47 |

| 4.4.24  | SLCD Configure New Register (MCFG_NEW)                | 48 |

| 4.4.25  | SLCD Control Register (MCTRL)                         | 51 |

| 4.4.26  | SLCD Status Register (MSTATE)                         | 52 |

| 4.4.27  | SLCD Data Register (MDATA)                            | 52 |

| 4.4.28  | SLCD Wait Time Register (WTIME)                       | 53 |

| 4.4.29  | Address Setup and Hold Time Register (TASH)           | 53 |

| 4.4.30  | Slow Mode Wait Time Register(SMWT)                    | 53 |

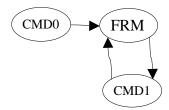

| 4.5 SL  | _CD Controller Operation                              | 54 |

| 4.5.1   | Set SLCD Controller AHB Clock and Pixel Clock         | 54 |

| 4.5.2   | Enabling the Controller                               | 54 |

| 4.5.3   | Disabling the Controller                              | 54 |

| 4.5.4   | Resetting the Controller                              | 55 |

| 4.5.5   | Frame Buffer                                          | 55 |

| 4.6 Sy  | stem Memory Format                                    | 55 |

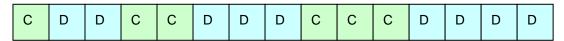

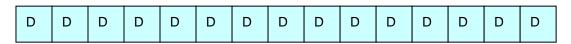

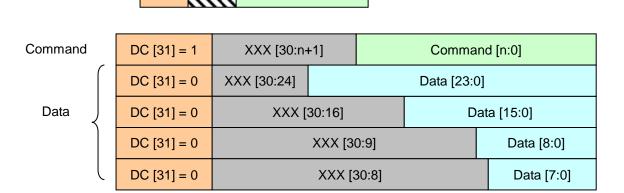

| 4.6.1   | Data format                                           | 55 |

| 4.6.2   | Command Format                                        | 57 |

| 4.7 Tr  | ansfer Mode                                           | 58 |

| 4.7.1   | DMA Transfer Mode                                     | 58 |

| 4.7.2   | Register Transfer Mode                                | 59 |

| 4.8 Tir | ming                                                  | 59 |

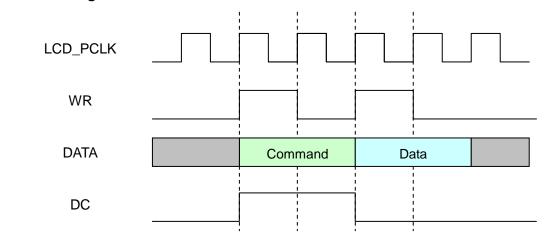

| 4.8.1   | Parallel Timing                                       | 59 |

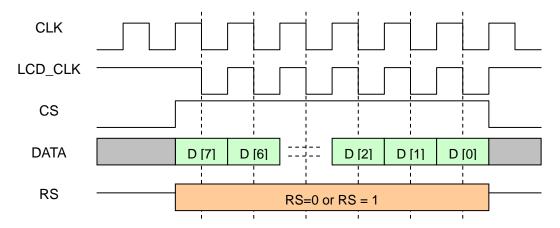

| 4.8.2   | Serial Timing                                         | 60 |

| 4.9 Op  | peration Guide                                        | 60 |

| 4.9.1   | DMA Operation                                         | 60 |

| 4.9.2   | Register Operation                                    | 61 |

| 5 Cam   | era Interface Module                                  | 62 |

| 5.1 Ov  | verview                                               | 62 |

| 5.1.1   | Features                                              | 62 |

| 5.1.2   | Pin Description                                       | 62 |

| 5.2 CI  | M Special Register                                    | 62 |

| 5.2.1   | CIM Configuration Register (CIMCFG)                   | 63 |

| 5.2.2   | CIM Control Register (CIMCR)                          | 66 |

| 5.2.3   | CIM Control Register 2 (CIMCR2)                       | 67 |

| 5.2.4   | CIM Status Register (CIMST)                           | 68 |

| 5.2.5   | CIM Interrupt Mask Register (CIMIMR)                  | 69 |

| 5.2.6   | CIM Interrupt ID Register (CIMIID)                    | 70 |

|   | 5.2.7    | CIM Descriptor Address (CIMDA)                        | 71  |

|---|----------|-------------------------------------------------------|-----|

|   | 5.2.8    | CIM Frame buffer Address Register (CIMFA)             | 71  |

|   | 5.2.9    | CIM Frame ID Register (CIMFID)                        | 71  |

|   | 5.2.10   | CIM DMA Command Register (CIMCMD)                     | 72  |

|   | 5.2.11   | CIM Window Size (CIMWSIZE)                            | 73  |

|   | 5.2.12   | CIM Window Offset (CIMWOFFSET)                        | 73  |

|   | 5.2.13   | CIM Frame Size Register (CIMFS)                       | 73  |

|   | 5.3 CIM  | 1 Data Sample Modes                                   | 74  |

|   | 5.3.1    | Gated Clock Mode                                      | 74  |

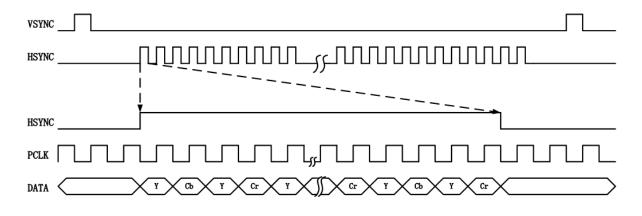

|   | 5.3.2    | ITU656 Interlace Mode                                 | 75  |

|   | 5.3.3    | ITU656 Progressive Mode                               | 76  |

|   | 5.4 DM   | A Descriptors                                         | 76  |

|   | 5.5 Soft | tware Operation                                       | 77  |

|   | 5.5.1    | Enable CIM with DMA                                   | 77  |

|   | 5.5.2    | Operations for RXFIFO Overflow                        | 77  |

|   | 5.5.3    | Operations for Frame Size Error                       | 77  |

| 6 | Audio    | Interface Controller                                  | 70  |

| U | Addio    | Therrace Controller                                   | 7 9 |

|   | 6.1 Ove  | erview                                                | 79  |

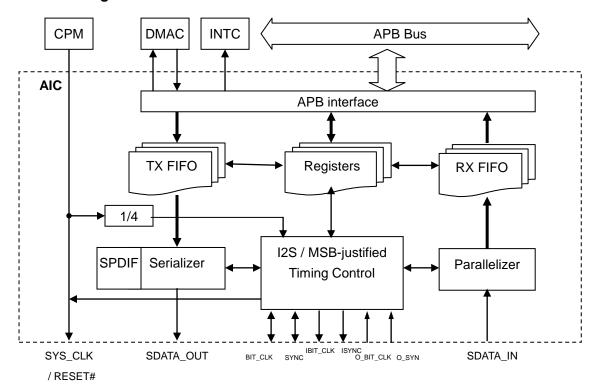

|   | 6.1.1    | Block Diagram                                         | 80  |

|   | 6.1.2    | Features                                              | 80  |

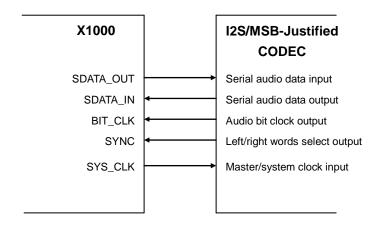

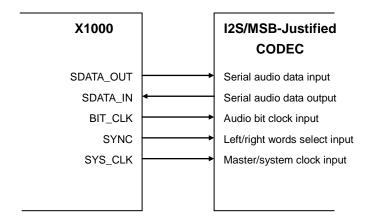

|   | 6.1.3    | Interface Diagram                                     | 81  |

|   | 6.1.4    | Signal Descriptions                                   | 82  |

|   | 6.2 Reg  | gister Descriptions                                   | 83  |

|   | 6.2.1    | AIC Configuration Register (AICFR)                    | 84  |

|   | 6.2.2    | AIC Common Control Register (AICCR)                   | 86  |

|   | 6.2.3    | AIC I2S/MSB-justified Control Register (I2SCR)        | 89  |

|   | 6.2.4    | AIC Controller FIFO Status Register (AICSR)           | 90  |

|   | 6.2.5    | AIC I2S/MSB-justified Status Register (I2SSR)         | 92  |

|   | 6.2.6    | AIC I2S/MSB-justified Clock Divider Register (I2SDIV) | 93  |

|   | 6.2.7    | AIC FIFO Data Port Register (AICDR)                   | 93  |

|   | 6.2.8    | SPDIF Enable Register (SPENA)                         | 94  |

|   | 6.2.9    | SPDIF Control Register (SPCTRL)                       | 94  |

|   | 6.2.10   | SPDIF State Register (SPSTATE)                        | 95  |

|   | 6.2.11   | SPDIF Configure 1 Register (SPCFG1)                   | 96  |

|   | 6.2.12   | SPDIF Configure 2 Register (SPCFG2)                   | 97  |

|   | 6.2.13   | SPDIF FIFO Register (SPFIFO)                          | 98  |

|   | 6.3 Seri | ial Interface Protocol                                | 99  |

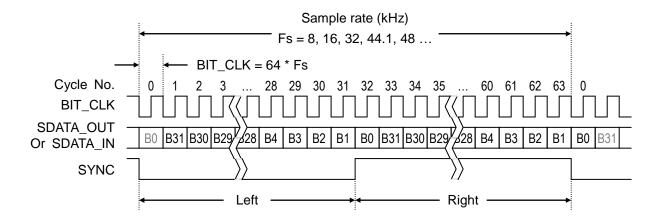

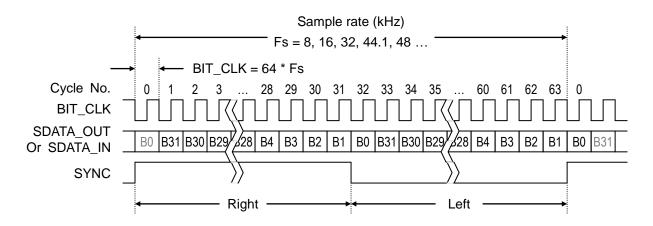

|   | 6.3.1    | I2S and MSB-justified serial audio format             | 99  |

|   | 6.3.2    | Audio sample data placement in SDATA_IN/SDATA_OUT     | 101 |

|   | 6.3.3    | SPDIF Protocol                                        |     |

|   | 6.4 I2S  | Operation                                             | 103 |

|   | 6.4.1    | Initialization                                        | 103 |

|   |          |                                                       |     |

|   | 0.40  | E total COREO Business Assess Counties         | 40. |

|---|-------|------------------------------------------------|-----|

|   | 6.4.2 | External CODEC Registers Access Operation      |     |

|   | 6.4.3 | Audio Replay                                   |     |

|   | 6.4.4 | Audio Record                                   |     |

|   | 6.4.5 | FIFOs operation                                |     |

|   | 6.4.6 | Data Flow Control                              |     |

|   | 6.4.7 | Audio Samples format                           |     |

|   | 6.4.8 | Serial Audio Clocks and Sampling Frequencies   |     |

|   | 6.4.9 | Interrupts                                     |     |

| ( |       | SPDIF Guide                                    |     |

|   | 6.5.1 | Set SPDIF clock frequency                      |     |

|   | 6.5.2 | PCM audio mode operation (Reference IEC60958)  |     |

|   | 6.5.3 | Non-PCM mode operation (Reference IEC61937)    |     |

|   | 6.5.4 | Disable operation                              | 116 |

| 7 | PCN   | / Interface                                    | 117 |

| - | 7.1   | Overview                                       | 117 |

| 7 | 7.2 F | Pin Description                                | 117 |

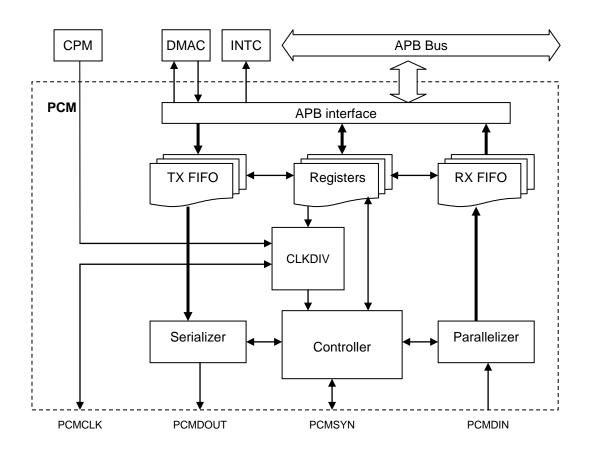

| 7 | 7.3 E | Block Diagram                                  | 118 |

| 7 | 7.4 F | Registers                                      | 118 |

|   | 7.4.1 | Registers Memory Map                           | 119 |

|   | 7.4.2 | Register Description                           | 119 |

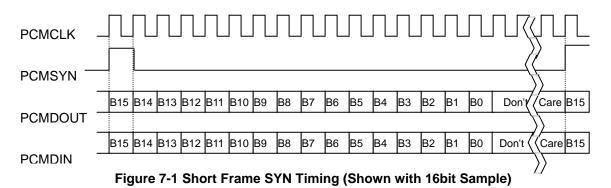

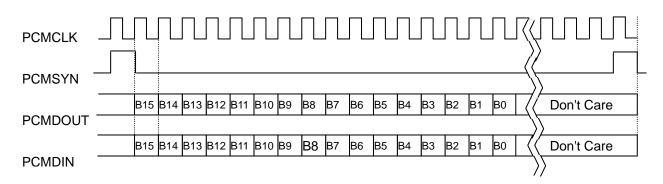

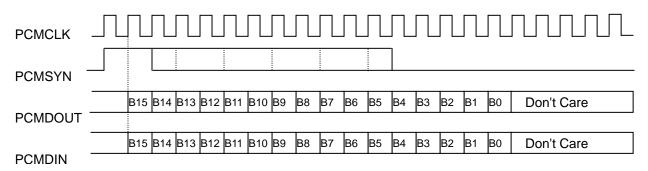

| 7 | 7.5 F | PCM Interface Timing                           | 125 |

|   | 7.5.1 | Short Frame SYN                                | 125 |

|   | 7.5.2 | Long Frame SYN                                 | 126 |

|   | 7.5.3 | Multi-Slot Operation                           | 126 |

| - | 7.6 F | PCM Operation                                  | 127 |

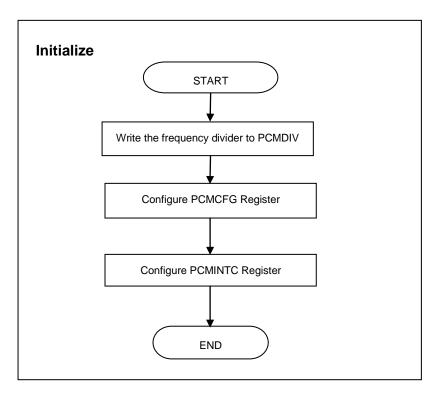

|   | 7.6.1 | PCM Initialization                             | 127 |

|   | 7.6.2 | Audio Replay                                   | 127 |

|   | 7.6.3 | Audio Record                                   | 128 |

|   | 7.6.4 | FIFOs operation                                | 128 |

|   | 7.6.5 | Data Flow Control                              | 129 |

|   | 7.6.6 | PCM Serial Clocks and Sampling Frequencies     | 130 |

|   | 7.6.7 | Interrupts                                     |     |

| 8 | Inte  | rnal CODEC                                     | 131 |

| 8 | 3.1 C | Overview                                       | 131 |

| 8 | 3.2 F | eatures                                        | 131 |

|   | 8.2.1 | Signal Descriptions                            | 132 |

|   | 8.2.2 | Block Diagram                                  | 133 |

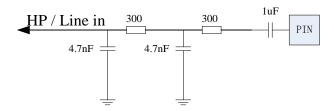

|   | 8.2.3 | Application schematic                          | 134 |

| 8 | 3.3 N | Mapped Register Descriptions                   | 134 |

|   | 8.3.1 | CODEC internal register access control (RGADW) |     |

|   | 8.3.2 | CODEC internal register data output (RGDATA)   | 136 |

|   |       |                                                |     |

| 8.4  | Оре    | eration                                                                      | . 136 |

|------|--------|------------------------------------------------------------------------------|-------|

| 8.4  | .1     | Access to internal registers of the embedded CODEC                           | . 137 |

| 8.4  | .2     | CODEC controlling and typical operations                                     | . 137 |

| 8.4  | .3     | Power saving                                                                 | . 138 |

| 8.4  | .4     | Pop noise and the reduction of it                                            | . 138 |

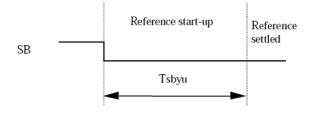

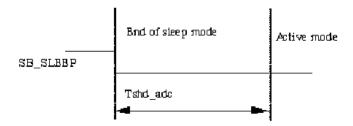

| 8.5  | Tim    | ing parameters                                                               | . 139 |

| 8.6  | Ср     | arameters                                                                    | .140  |

| 8.7  | CO     | DEC internal Registers                                                       | .140  |

| 8.7  | .1     | Registers Memory Map                                                         | . 141 |

| 8.7  | .2     | Register Description                                                         | . 143 |

| 8.8  | Pro    | grammable gains                                                              | . 174 |

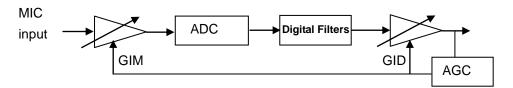

| 8.8  | .1     | Programmable boost gain: GIM                                                 | . 174 |

| 8.8  | .2     | Programmable input gain amplifier: GID                                       | .175  |

| 8.8  | .3     | Programmable digital attenuation: GOD                                        | . 175 |

| 8.8  | .4     | Programmable attenuation: GO                                                 | .176  |

| 8.8  | .5     | Programmable digital mixer gain: GIMIX and GOMIX                             | . 176 |

| 8.8  | .6     | Gain refresh strategy                                                        | . 177 |

| 8.9  | Cor    | figuration of the headphone output stage                                     | . 177 |

| 8.10 | Out    | -of-band noise filtering                                                     | . 178 |

| 8.1  | 0.1    | Reset of short circuit detection                                             | .178  |

| 8.11 | San    | npling frequency: FREQ                                                       | .178  |

| 8.12 | Pro    | grammable data word length                                                   | . 179 |

| 8.13 | Rar    | nping system note                                                            | . 179 |

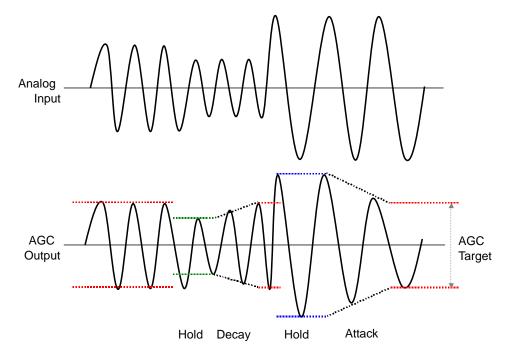

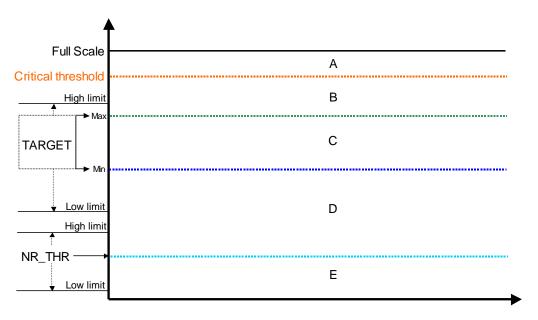

| 8.14 | AG     | C system guide                                                               | .180  |

| 8.1  | 4.1    | AGC operating mode                                                           | .180  |

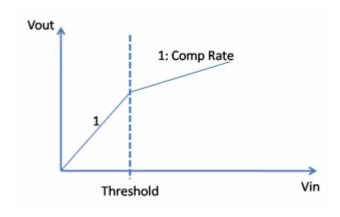

| 8.15 | DR     | C description                                                                | .182  |

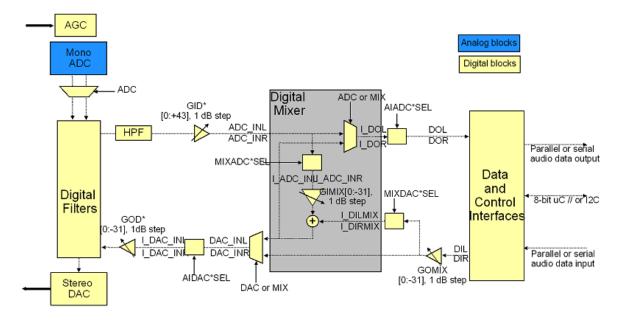

| 8.16 | Dig    | tal Mixer description                                                        | . 183 |

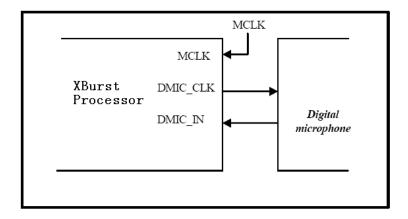

| 8.17 | Dig    | tal microphone interface                                                     | . 184 |

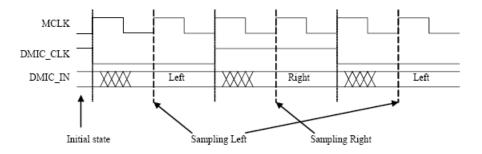

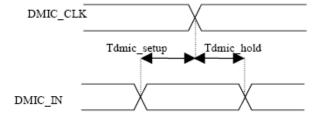

| 8.1  | 7.1    | Timing Diagram                                                               | 185   |

| 8.1  | 7.2    | Timings                                                                      | .185  |

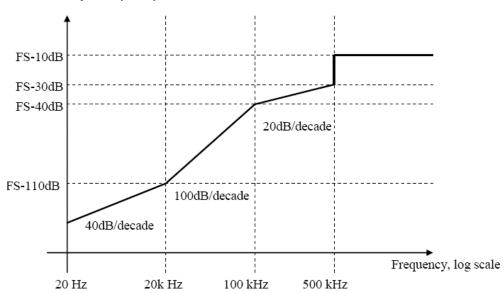

| 8.1  | 7.3    | Noise template (TBC)                                                         | .186  |

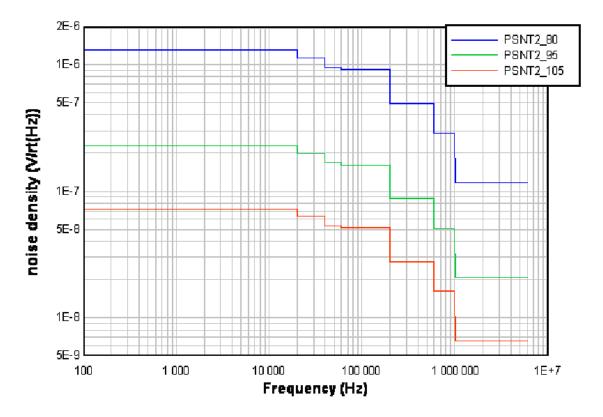

| 8.1  | 7.4    | Power Supply Noise Tolerance Template (PSNT2) on analog power supply for I/O |       |

| buf  | fers c | of DAC outputs (VDDIO_CODEC)                                                 | . 186 |

| 8.18 | CO     | DEC Operating modes                                                          | . 187 |

| 8.1  | 8.1    | Initial all the gain                                                         | . 188 |

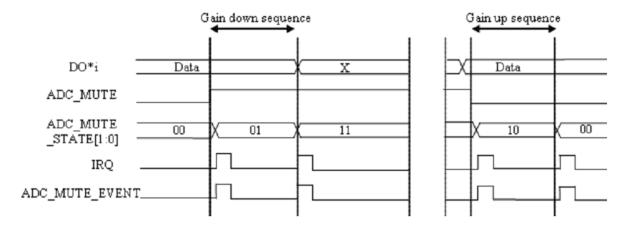

| 8.1  | 8.2    | Soft Mute mode                                                               | .189  |

| 8.1  | 8.3    | Power-down and sleep modes                                                   | . 190 |

| 8.1  | 8.4    | Working modes summary                                                        | . 191 |

| 8.19 | MC     | LK turn-off and turn-on                                                      | .192  |

| 8.20 | Red    | uirements on outputs and inputs selection and power-down modes               | .192  |

| 8.2  | 0.1    | Initialization and configuration                                             | .192  |

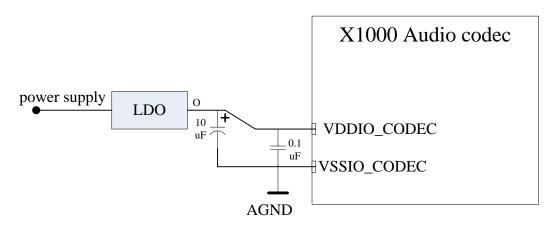

| 8.21 | Circ   | cuits design suggestions                                                     | . 193 |

| 8.2  | 1.1    | Avoid quiet ground common currents                                           | . 193 |

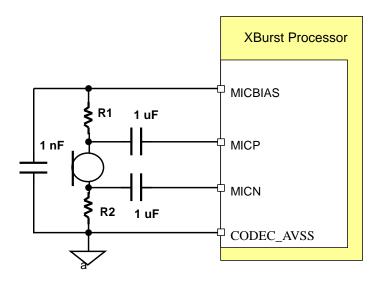

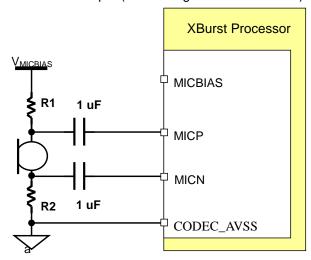

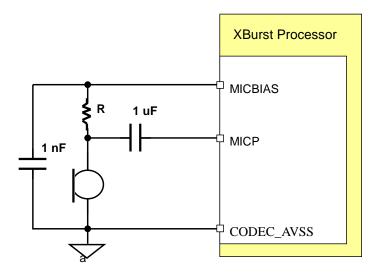

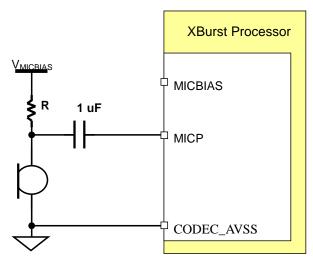

| 8.21.2           | Microphone connection                                      | 194 |

|------------------|------------------------------------------------------------|-----|

| 8.21.3           | PCB considerations                                         |     |

| 8.22 An          | alog characteristics                                       | 198 |

| 8.22.1           | Operating conditions                                       | 198 |

| 8.22.2           | With PWM output, used for analog amplifier application     | 198 |

| 8.22.3           | Microphone / Line input to ADC path                        | 199 |

| 8.22.4           | Micbias and reference                                      | 201 |

| 8.22.5           | I/O buffers                                                | 201 |

| 8.22.6           | Characteristics of the ADC High Pass Filter                | 202 |

| 8.22.7           | Characteristics of the ADC Wind Noise Filter               | 202 |

|                  | Section 5 Memory Interface                                 |     |

| 9 DDR            | Controller                                                 | 204 |

| 9.1 Ov           | rerview                                                    | 204 |

| 9.1.1            | Supported DDR SDRAM Types                                  | 204 |

| 9.1.2            | Block Diagram                                              |     |

|                  | gister Description                                         |     |

| 9.2.1            | DSTATUS                                                    |     |

| 9.2.2            | DCFG                                                       |     |

| 9.2.3            | DCTRL                                                      |     |

| 9.2.4            | DLMR                                                       |     |

| 9.2.5            | DTIMING1,2,3,4,5,6 (DDR Timing Configure Register)         |     |

| 9.2.6            | DREFCNT (DDR Auto-Refresh Counter)                         |     |

| 9.2.7            | DMMAP0,1 (DDR Memory Map Configure Register)               |     |

| 9.2.8            | DDLP (DDR DFI low power handshake control register)        |     |

| 9.2.9            | DREMAP1,2,3,4,5 (DDR Address Remapping Register 1,2,3,4,5) |     |

| 9.2.10           | WCMDCTRL1 (Performance wcmd reorder & grouping)            |     |

| 9.2.11           | RCMDCTRL0 (Performance rcmd request control)               |     |

| 9.2.12           | RCMDCTRL1 (Performance rcmd request control)               |     |

| 9.2.13           | BOUNDARYSEL (Channel boundary select)                      |     |

| 9.2.14<br>9.2.15 | WDATTHD0 (performance wcmd request control)                |     |

| 9.2.16           | IPORTPRI (performance priority control)                    |     |

| 9.2.17           | CHxQOS0,1,2,3,4,5 (performance QoS control)                |     |

| 9.2.18           | AUTOSR_CNT                                                 |     |

| 9.2.19           | AUTOSR_EN                                                  |     |

| 9.2.20           | CLKSTP_CFG                                                 |     |

| 9.2.21           | DDRC_STATUS                                                |     |

| 9.2.22           | PHYRET_CFG                                                 |     |

| 9.2.23           | PHYRST_CFG                                                 |     |

| 9.2.24           | CPM_DRCG                                                   |     |

| 9.3 Fu           | nctional Description                                       |     |

|                  |                                                            |     |

| 9.3   | 3.1  | DDRC and DDR2 Memory Initialization Sequence             | 235 |

|-------|------|----------------------------------------------------------|-----|

| 9.4   | Cha  | ange Clock Frequency                                     | 236 |

| 9.4   | .1   | Manually SELF-REFRESH Mode                               | 236 |

| 9.4   | .2   | CPM driven SELF-REFRESH Mode                             | 236 |

| 9.4   | .3   | DLL bypass mode                                          | 236 |

| 9.5   | Dat  | a Endian                                                 | 237 |

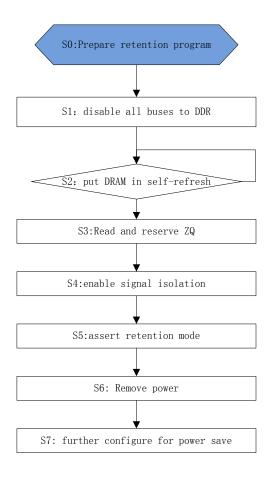

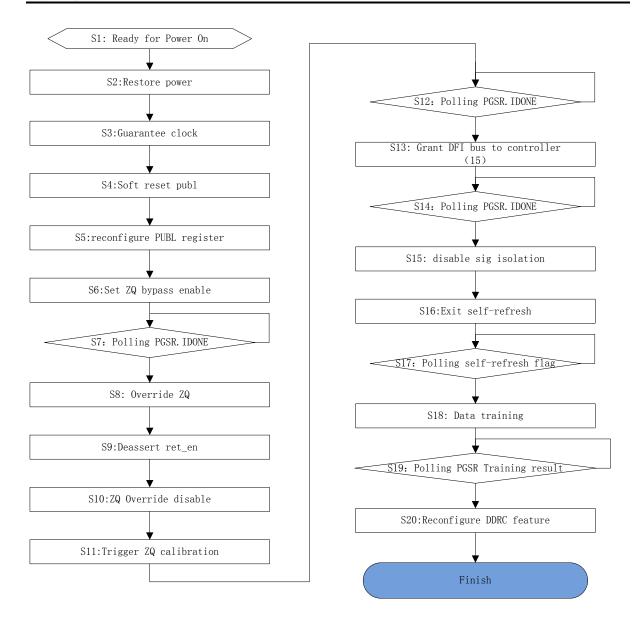

| 9.6   | Ret  | ention Flow                                              | 237 |

| 9.6   | 5.1  | Enter Retention mode                                     | 237 |

| 9.6   | 5.2  | Exit Retention mode                                      | 238 |

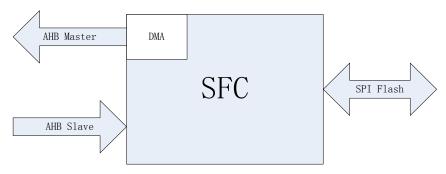

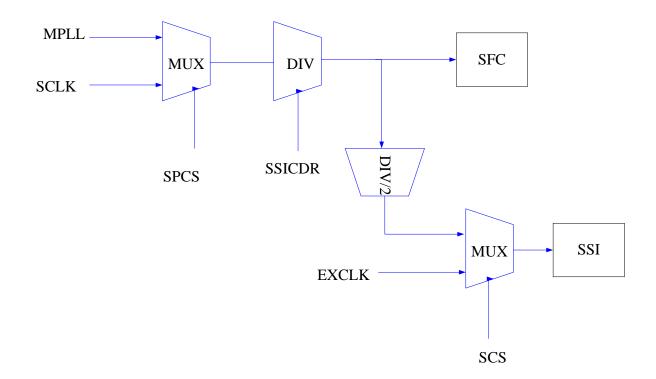

| 10 SF | PI F | lash Controller(SFC)                                     | 242 |

| 10.1  | Ove  | erview                                                   | 242 |

| 10.2  | Fea  | itures                                                   | 242 |

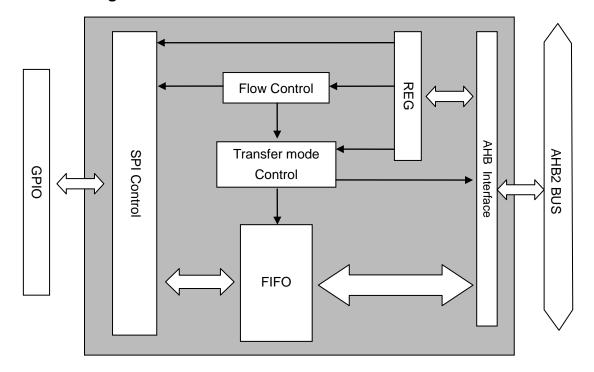

| 10.3  | Blo  | ck Diagram                                               | 243 |

| 10.4  | Fur  | nctional Description                                     | 243 |

| 10.   | .4.1 | Bus function                                             | 243 |

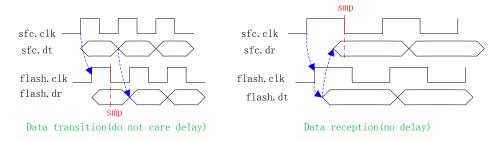

| 10.   | 4.2  | Configurable Timing parameter                            |     |

| 10.5  | Pin  | Description                                              | 245 |

| 10.6  |      | a Format Description                                     |     |

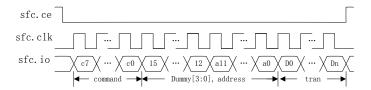

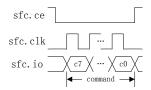

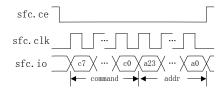

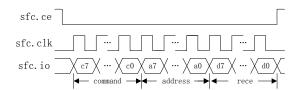

| 10.   | .6.1 | Transfer format                                          |     |

| 10.   | 6.2  | Endian Description                                       |     |

| 10.7  |      | gisters Description                                      |     |

|       | 7.1  | Instructions                                             |     |

|       | 7.2  | Map                                                      |     |

|       | 7.3  | Registers                                                |     |

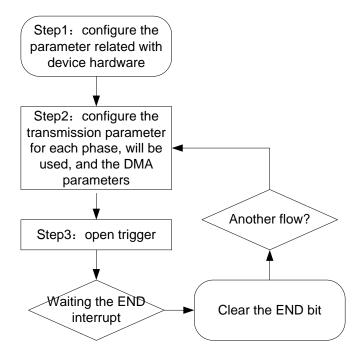

| 10.8  |      | tware Guideline                                          |     |

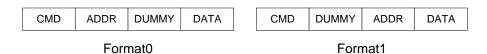

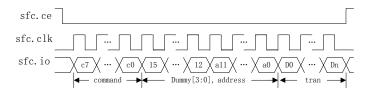

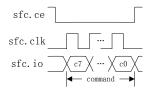

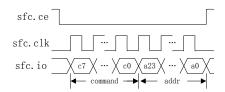

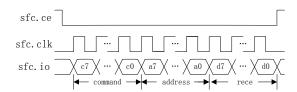

| _     | .8.1 | Phase Description                                        |     |

|       | 8.2  | Multi phases flow                                        |     |

|       | 8.3  | One phase flow                                           |     |

|       | 8.4  | Meters of DMA operation need attention                   |     |

|       | 8.5  | Meters of slave mode operation need attention            |     |

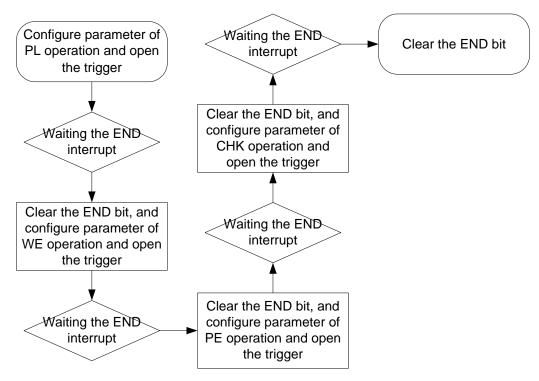

| 10.   |      | Example (NAND flash write with multi phases in DMA mode) |     |

| 10.   |      | Example (NAND flash write with single phase in REG mode) |     |

| 10.9  | Ind  | ЭX                                                       | 263 |

|       |      | Section 6 System Functions                               |     |

| 11 CI | ock  | Reset and Power Controller                               | 265 |

| 11.1  | Ove  | erview                                                   | 265 |

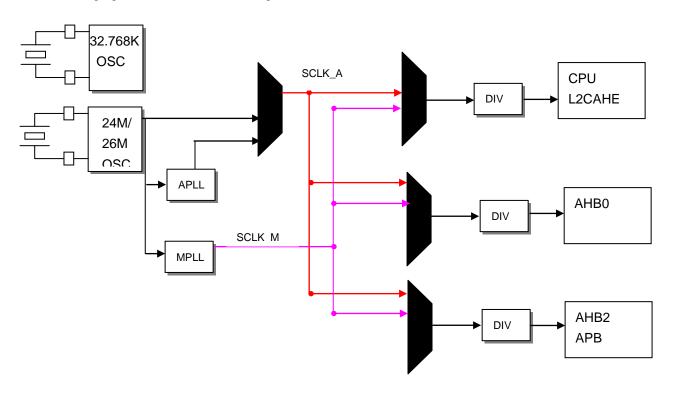

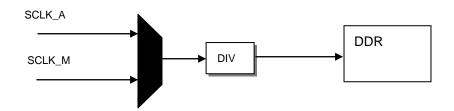

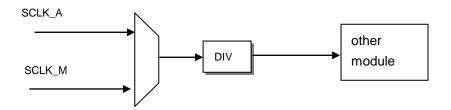

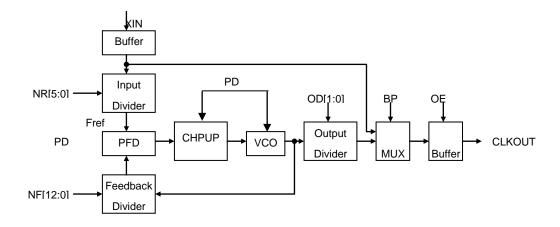

| 11.   | 1.1  | CGU Block Diagram                                        | 266 |

| 11.   | 1.2  | CGU Registers                                            | 267 |

| 11.   | 1.3  | PLL Operation                                            | 292 |

| 11.   | 1.4  | Main Clock Division Change Sequence                      | 294 |

| 11.2 Pov | ver Manager                                 | 294 |

|----------|---------------------------------------------|-----|

| 11.2.1   | Low-Power Modes and Function                | 294 |

| 11.2.2   | Register Description                        | 295 |

| 11.2.3   | IDLE Mode                                   | 303 |

| 11.2.4   | SLEEP Mode                                  | 304 |

| 11.3 Res | set Control Module                          | 304 |

| 11.3.1   | Register Description                        | 304 |

| 11.3.2   | Power On Reset                              | 305 |

| 11.3.3   | WDT Reset                                   | 305 |

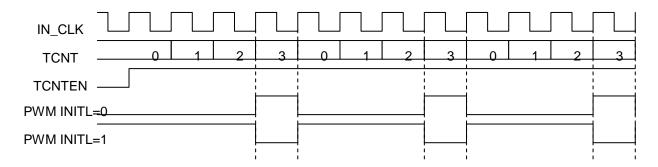

| 12 Timer | /Counter Unit                               | 306 |

| 12.1 Ove | erview                                      | 306 |

| 12.2 Pin | Description                                 | 306 |

| 12.3 Reg | gister Description                          | 307 |

| 12.3.1   | Timer Control Register (TCSR)               | 308 |

| 12.3.2   | Timer Data FULL Register (TDFR)             | 311 |

| 12.3.3   | Timer Data HALF Register (TDHR)             | 311 |

| 12.3.4   | Timer Counter (TCNT)                        | 311 |

| 12.3.5   | Timer Counter Enable Register (TER)         | 312 |

| 12.3.6   | Timer Counter Enable Set Register (TESR)    | 313 |

| 12.3.7   | Timer Counter Enable Clear Register (TECR)  | 314 |

| 12.3.8   | Timer Flag Register (TFR)                   | 315 |

| 12.3.9   | Timer Flag Set Register (TFSR)              | 315 |

| 12.3.10  | Timer Flag Clear Register (TFCR)            | 316 |

| 12.3.11  | Timer Mast Register (TMR)                   | 317 |

| 12.3.12  | Timer Mask Set Register (TMSR)              | 318 |

| 12.3.13  | Timer Mask Clear Register (TMCR)            | 318 |

| 12.3.14  | Timer Stop Register (TSR)                   | 319 |

| 12.3.15  | Timer Stop Set Register (TSSR)              | 320 |

| 12.3.16  | Timer Stop Clear Register (TSCR)            | 321 |

| 12.3.17  | Timer Status Register (TSTR)                | 322 |

| 12.3.18  | Timer Status Set Register (TSTSR)           | 323 |

| 12.3.19  | Timer Status Clear Register (TSTCR)         | 323 |

| 12.4 Ope | eration                                     | 324 |

| 12.4.1   | Basic Operation in TCU1 Mode                | 324 |

| 12.4.2   | Disable and Shutdown Operation in TCU1 Mode | 325 |

| 12.4.3   | Basic Operation in TCU2 Mode                | 325 |

| 12.4.4   | Disable and Shutdown Operation in TCU2 Mode |     |

| 12.4.5   | Read Counter in TCU2 Mode                   |     |

| 12.4.6   | Pulse Width Modulator (PWM)                 | 326 |

| 12.4.7   | Trackball Input Waveform Detect             |     |

| 13 Opera | ating System Timer                          | 328 |

| 13.1 ove  | rview                                                            | 328 |

|-----------|------------------------------------------------------------------|-----|

| 13.2 reg  | ster description                                                 | 328 |

| 13.2.1    | Timer Clock Control Register (OSTCCR)                            | 329 |

| 13.2.2    | Timer Counter Enable Register (OSTER, OSTESR, OSTECR)            | 330 |

| 13.2.3    | Timer Counter Clear Register (OSTCR)                             | 331 |

| 13.2.4    | Timer Data FULL Register (OST1DFR)                               | 332 |

| 13.2.5    | Timer Counter (OST1CNT)                                          | 332 |

| 13.2.6    | Timer Flag Register (OST1FR)                                     | 332 |

| 13.2.7    | Timer Mask Register (OST1MR)                                     | 333 |

| 13.2.8    | Operating System Timer Counter (OST2CNTH, OST2CNTL)              | 333 |

| 13.2.9    | Operating System Timer Counter high 32 bits buffer (OSTCNT2HBUF) | 333 |

| 13.3 Ope  | eration                                                          | 334 |

| 13.3.1    | Basic Operation in channel1                                      | 334 |

| 13.3.2    | Stop Operation in channel1                                       | 334 |

| 13.3.3    | modify the prsecale in channel1                                  | 334 |

| 11 Intorr | unt Controllor                                                   | 225 |

| 14 miem   | upt Controller                                                   | 333 |

| 14.1 Ove  | erview                                                           | 335 |

| 14.2 Re   | gister Description                                               | 335 |

| 14.2.1    | Interrupt Controller Source Register (ICSR0)                     | 336 |

| 14.2.2    | Interrupt Controller Source Register (ICSR1)                     | 337 |

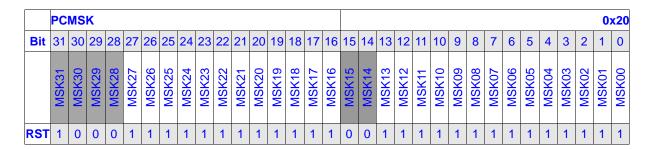

| 14.2.3    | Interrupt Controller Mask Register (ICMR0)                       | 337 |

| 14.2.4    | Interrupt Controller Mask Register (ICMR1)                       | 338 |

| 14.2.5    | Interrupt Controller Mask Set Register (ICMSR0)                  | 338 |

| 14.2.6    | Interrupt Controller Mask Set Register (ICMSR1)                  | 338 |

| 14.2.7    | Interrupt Controller Mask Clear Register (ICMCR0)                | 339 |

| 14.2.8    | Interrupt Controller Mask Clear Register (ICMCR1)                | 339 |

| 14.2.9    | Interrupt Controller Pending Register (ICPR0)                    | 339 |

| 14.2.10   | Interrupt Controller Pending Register (ICPR1)                    | 340 |

| 14.2.11   | Interrupt Source Register0 for PDMA (DSR0)                       | 340 |

| 14.2.12   | Interrupt Mask Register0 for PDMA (DMR0)                         | 341 |

| 14.2.13   | Interrupt Pending Register0 for PDMA (DPR0)                      | 341 |

| 14.2.14   | Interrupt Source Register1 to PDMA (DSR1)                        | 341 |

| 14.2.15   | Interrupt Mask Register1 for PDMA (DMR1)                         | 342 |

| 14.2.16   | Interrupt Pending Register1 for PDMA (DPR1)                      | 342 |

| 14.3 Sof  | tware Considerations                                             | 343 |

| 15 Watch  | ndog Timer                                                       | 344 |

| 15.1 Ove  | erview                                                           | 344 |

|           | gister Description                                               |     |

| 15.2.1    | Watchdog Control Register (TCSR)                                 |     |

| 15.2.2    | Watchdog Enable Register (TCER)                                  |     |

| 15.2.3    | Watchdog Timer Data Register (TDR)                               |     |

|           | ,                                                                |     |

| 15.2.4  | Watchdog Timer Counter (TCNT)                | 347 |

|---------|----------------------------------------------|-----|

| 15.3 W  | atchdog Timer Function                       | 347 |

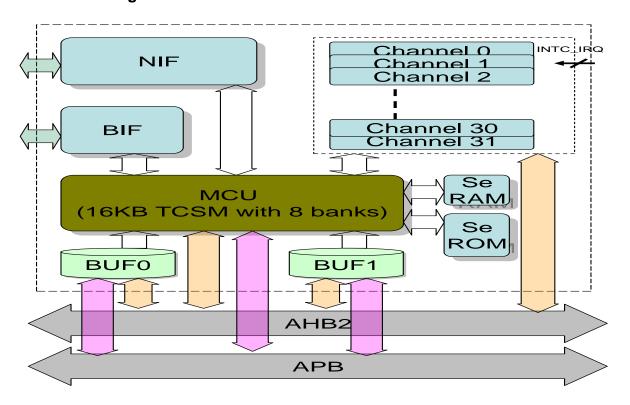

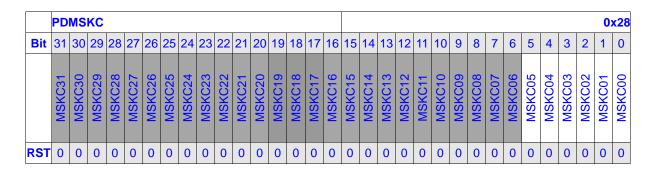

| 16 PDM  | A Controller                                 | 348 |

| 16.1 O  | verview                                      | 348 |

| 16.2 Fe | eatures                                      | 348 |

| 16.3 BI | ock Diagram                                  | 348 |

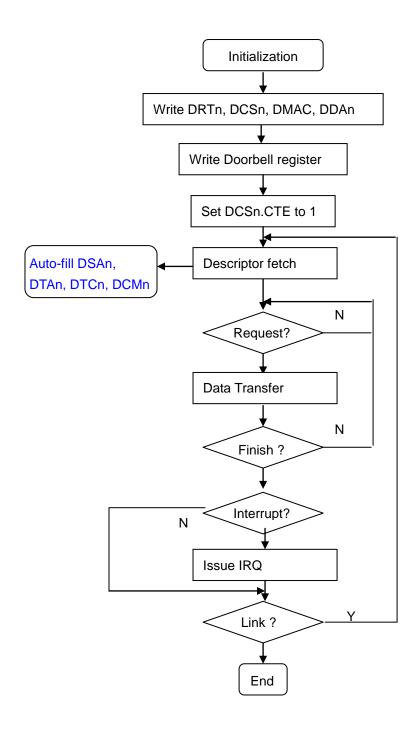

| 16.4 M  | emory Mapped Register Descriptions           | 349 |

| 16.4.1  | DMA Channel Registers                        | 349 |

| 16.4.2  | Global Control Registers                     | 349 |

| 16.5 DI | MA Channel Register Definition               | 350 |

| 16.5.1  | DMA Source Address (DSAn, n = 0 ~ 7)         | 350 |

| 16.5.2  | DMA Target Address (DTAn, n = 0 ~ 7)         | 351 |

| 16.5.3  | DMA Transfer Count (DTCn, n = 0 ~ 7)         | 351 |

| 16.5.4  | DMA Request Types (DRTn, n = 0 ~ 7)          | 351 |

| 16.5.5  | DMA Channel Control/Status (DCSn, n = 0 ~ 7) | 352 |

| 16.5.6  | DMA Channel Command (DCMn, n = 0 ~ 7)        | 353 |

| 16.5.7  | DMA Descriptor Address (DDAn, n = 0 ~ 7)     | 356 |

| 16.5.8  | DMA Stride Difference (DSDn, n = 0 ~ 7)      | 356 |

| 16.6 DI | MA Global Register Definition                | 357 |

| 16.6.1  | DMA Control                                  | 357 |

| 16.6.2  | DMA Interrupt Pending (DIRQP)                | 358 |

| 16.6.3  | DMA Doorbell (DDB)                           | 358 |

| 16.6.4  | DMA Doorbell Set (DDS)                       | 359 |

| 16.6.5  | Descriptor Interrupt Pending (DIP)           | 359 |

| 16.6.6  | Descriptor Interrupt Clear (DIC)             | 359 |

| 16.6.7  | DMA Channel Programmable (DMACP)             | 360 |

| 16.6.8  | DMA Soft IRQ Pending (DSIRQP)                | 360 |

| 16.6.9  | DMA Soft IRQ Mask (DSIRQM)                   | 361 |

| 16.6.10 | DMA Channel IRQ Pending to MCU (DCIRQP)      | 361 |

| 16.6.11 | DMA Channel IRQ to MCU Mask (DCIRQM)         | 362 |

| 16.7 M  | CU                                           | 362 |

| 16.7.1  | MCU Control & Status                         | 362 |

| 16.7.2  | MCU Normal MailBox                           | 363 |

| 16.7.3  | MCU Security MailBox                         | 363 |

| 16.7.4  | MCU Interrupt                                | 364 |

| 16.7.5  | Multiple Bank Tightly Coupled Sharing Memory | 364 |

| 16.7.6  | CP0 Registers of MCU                         | 364 |

| 16.7.7  | Normal Exceptions Accepted by MCU            | 365 |

| 16.7.8  | How to Boot MCU Up                           | 365 |

| 16.8 DI | MA manipulation                              |     |

| 16.8.1  | Descriptor Transfer Mode                     | 366 |

| 16.8.2  | No-Descriptor Transfer Mode                  | 369 |

| 16.8.3   | Descriptor Transfer Interrupt/Stop control            | 369 |

|----------|-------------------------------------------------------|-----|

| 16.9 DN  | //A Requests                                          | 371 |

| 16.9.1   | Auto Request                                          | 371 |

| 16.9.2   | On-Chip Peripheral Request                            | 371 |

| 16.10 Ho | w to Use Programmable DMA Channel                     | 371 |

| 17 Real  | Time Clock                                            | 372 |

| 17.1 Ov  | erview                                                | 372 |

| 17.2 Fe  | atures                                                | 372 |

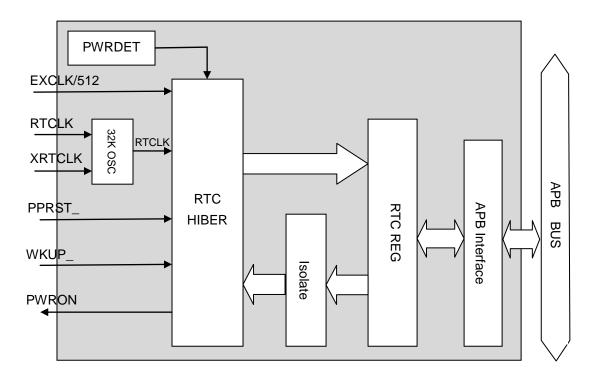

| 17.3 Blo | ock Diagram                                           | 372 |

| 17.4 Pir | ns Description                                        | 373 |

| 17.5 Re  | gisters Description                                   | 373 |

| 17.5.1   | RTC Control Register (RTCCR)                          | 375 |

| 17.5.2   | RTC Second Register (RTCSR)                           | 376 |

| 17.5.3   | RTC Second Alarm Register (RTCSAR)                    | 377 |

| 17.5.4   | RTC Regulator Register (RTCGR)                        | 377 |

| 17.5.5   | Hibernate Control Register (HCR)                      |     |

| 17.5.6   | HIBERNATE mode Wakeup Filter Counter Register (HWFCR) | 378 |

| 17.5.7   | Hibernate Reset Counter Register (HRCR)               | 379 |

| 17.5.8   | HIBERNATE Wakeup Control Register (HWCR)              | 379 |

| 17.5.9   | HIBERNATE Wakeup Status Register (HWRSR)              | 380 |

| 17.5.10  | Hibernate Scratch Pattern Register (HSPR)             | 381 |

| 17.5.11  | Write Enable Pattern Register (WENR)                  | 382 |

| 17.5.12  | WKUP_PIN_RST control register (WKUPPINCR)             | 382 |

| 17.6 Op  | eration Flow                                          | 383 |

| 17.6.1   | Registers Access                                      |     |

| 17.6.2   | Normal Mode                                           | 384 |

| 17.6.3   | HIBERNATE Mode                                        | 384 |

| 17.6.4   | Time Regulation                                       | 385 |

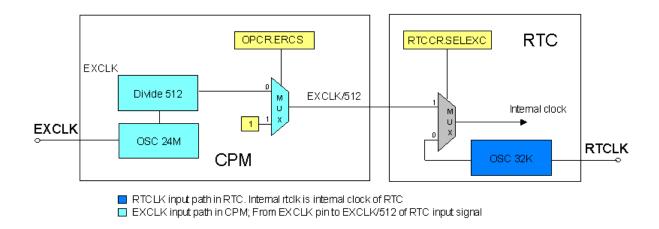

| 17.6.5   | Clock select                                          | 385 |

| 18 EFUS  | SE Slave Interface (EFUSE)                            | 387 |

| 18.1 Ov  | erview                                                | 387 |

| 18.2 Re  | gisters                                               | 387 |

| 18.2.1   | Registers Memory Map                                  | 388 |

| 18.2.2   | Registers and Fields Description                      | 388 |

| 18.3 Flo | ow                                                    | 392 |

| 18.3.1   | Program EFUSE Flow                                    | 392 |

| 18.3.2   | Program Security Key Flow                             | 393 |

| 18.3.3   | Read EFUSE Flow                                       | 393 |

| 18.3.4   | Read Security Key/Random Number Flow                  | 393 |

|          | Section 7 Peripherals                                 |     |

| 19 Gene  | ral-Purpose I/O Ports                                | 395 |

|----------|------------------------------------------------------|-----|

| 19.1 Ov  | erview                                               | 395 |

| 19.2 Fea | atures                                               | 395 |

| 19.3 Abo | out GPIO Port Summary Table                          | 395 |

| 19.3.1   | GPIO Port A Summary                                  | 396 |

| 19.3.2   | GPIO Port B Summary                                  | 397 |

| 19.3.3   | GPIO Port C Summary                                  | 398 |

| 19.3.4   | GPIO Port D Summary                                  | 398 |

| 19.3.5   | GPIO Port Z - Shadow Group                           | 398 |

| 19.4 Re  | gisters Description                                  | 399 |

| 19.4.1   | PORT A Register Group                                | 402 |

| 19.4.2   | PORT B Register Group                                | 410 |

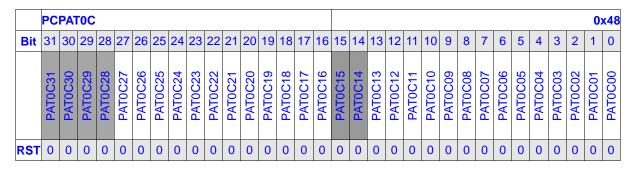

| 19.4.3   | PORT C Register Group                                | 417 |

| 19.4.4   | PORT D Register Group                                | 430 |

| 19.4.5   | PORT Z Shadow Register Group                         | 438 |

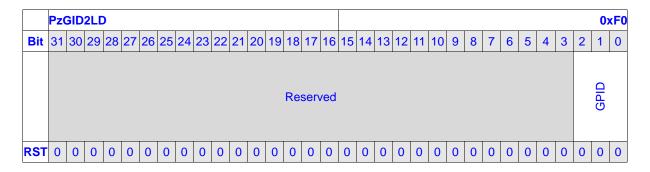

| 19.4.6   | GPIOZ Group ID to Load Register (PzGID2LD,0xF0)      | 440 |

| 19.5 Pro | ogram Guide                                          | 441 |

| 19.5.1   | Port Function Guide                                  | 441 |

| 19.5.2   | Configure without 3rd-unexpected state               | 441 |

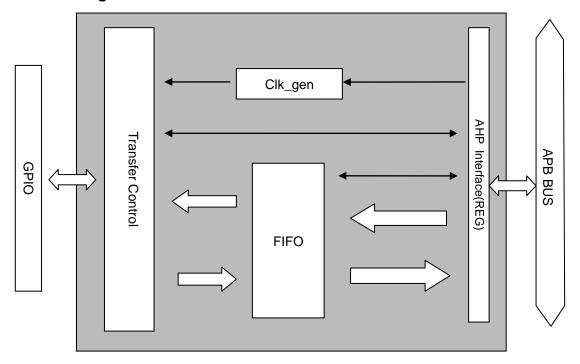

| 20 SMB   | Controller                                           | 443 |

| 20.1 Ov  | erview                                               | 443 |

| 20.1.1   | Features                                             | 443 |

| 20.1.2   | Pin Description                                      | 443 |

| 20.2 Re  | gisters                                              | 444 |

| 20.2.1   | Registers Memory Map                                 | 444 |

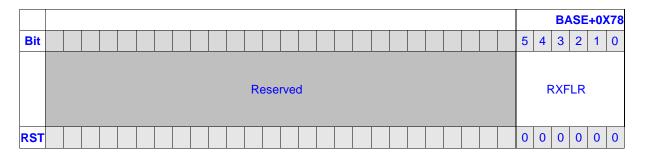

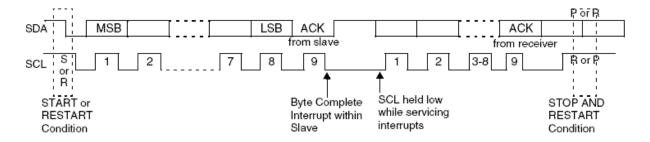

| 20.2.2   | Registers and Fields Description                     | 445 |

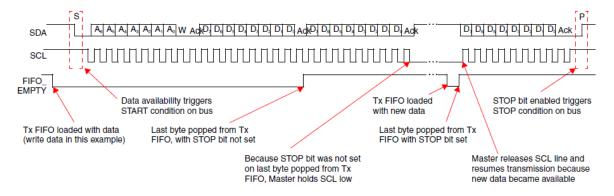

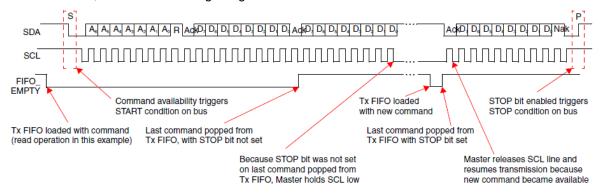

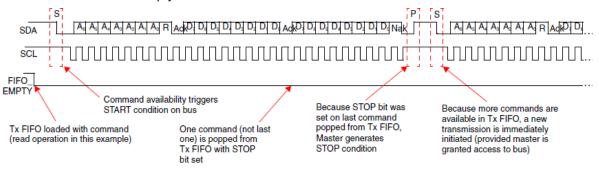

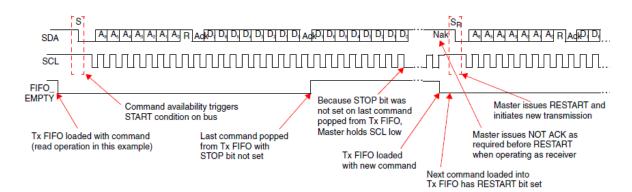

| 20.3 Op  | erating Flow                                         | 469 |

| 20.3.1   | SMB Behavior                                         | 470 |

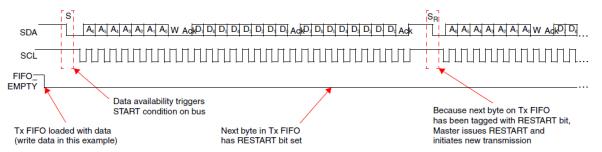

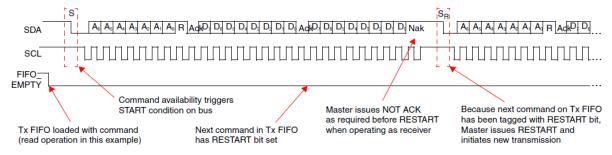

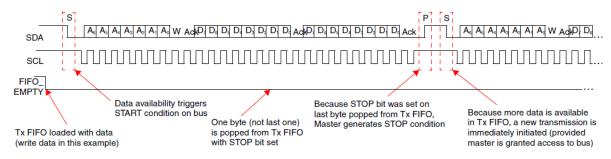

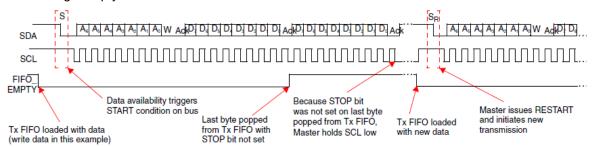

| 20.3.2   | Master Mode Operation                                | 470 |

| 20.3.3   | Slave Mode Operation                                 | 472 |

| 20.3.4   | Disabling SMB                                        | 475 |

| 20.3.5   | Summary the condition could flush TX FIFO            | 476 |

| 20.3.6   | The condition could generate START, STOP and RESTART | 476 |

| 21 Smar  | t Card Controller                                    | 480 |

| 21.1 Ov  | erview                                               | 480 |

| 21.2 Pin | Description                                          | 481 |

| 21.3 Re  | gister Descriptiongister Description                 | 481 |

| 21.3.1   | Transmit/Receive FIFO Data Register (SCCDR)          |     |

| 21.3.2   | FIFO Data Count Register (SCCFDR)                    |     |

| 21.3.3   | Control Register (SCCCR)                             |     |

| 21.   | 3.4  | Status Register (SCCSR)                                    | 484 |

|-------|------|------------------------------------------------------------|-----|

| 21.   | 3.5  | Transmission Factor Register (SCCTFR)                      | 484 |

| 21.   | 3.6  | Extra Guard Timer Register (SCCEGTR)                       | 485 |

| 21.   | 3.7  | ETU Counter Value Register (SCCECR)                        | 485 |

| 21.   | 3.8  | Reception Timeout Register (SCCRTOR)                       | 485 |

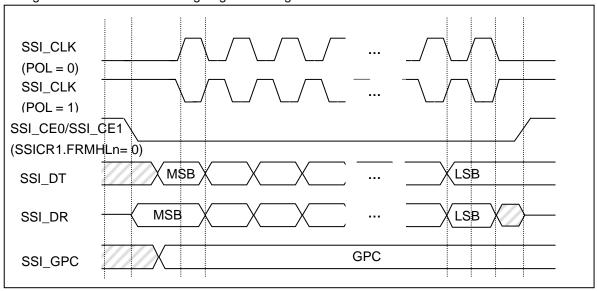

| 22 Sy | /nch | ronous Serial Interface(SSI)                               | 486 |

| 22.1  | Ove  | erview                                                     | 486 |

| 22.2  | Fea  | itures:                                                    | 486 |

| 22.3  | Blo  | ck Diagram                                                 | 487 |

| 22.4  | Fur  | nctional Description                                       | 487 |

| 22.5  | Pin  | Description                                                | 488 |

| 22.6  | Dat  | a Formats                                                  | 488 |

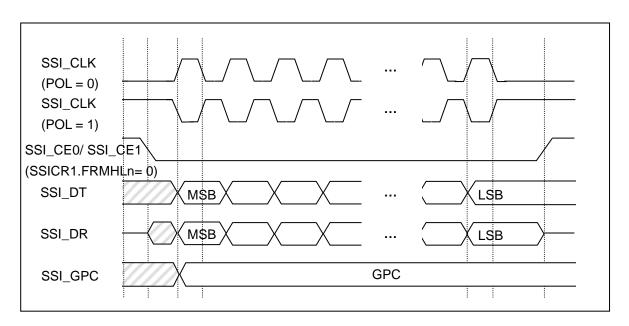

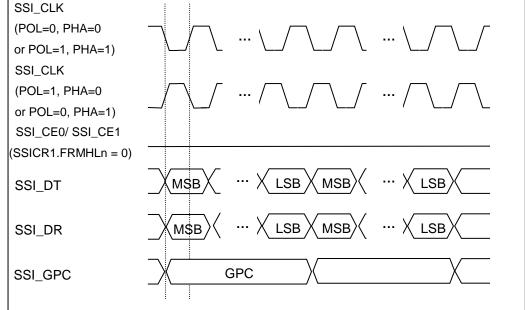

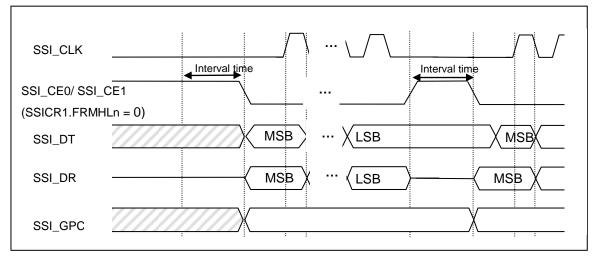

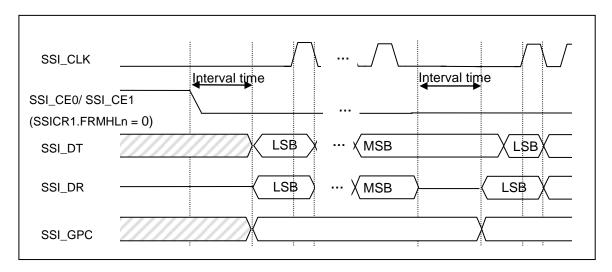

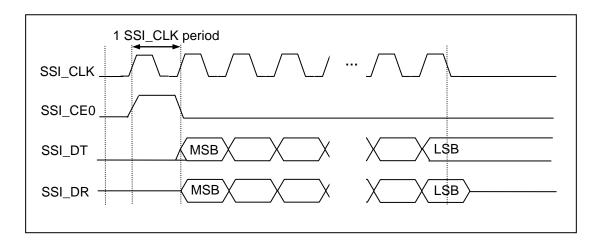

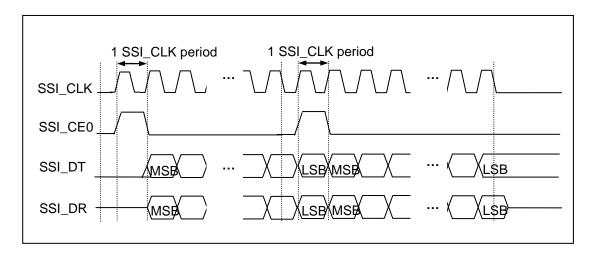

| 22.   | 6.1  | Motorola's SPI Format Details                              | 489 |

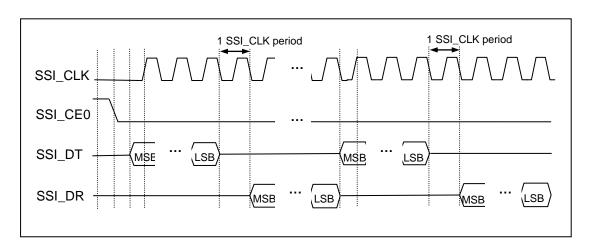

| 22.   | 6.2  | TI's SSP Format Details                                    | 492 |

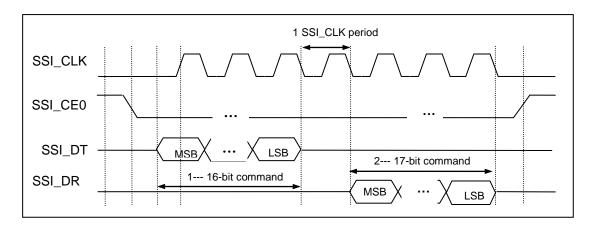

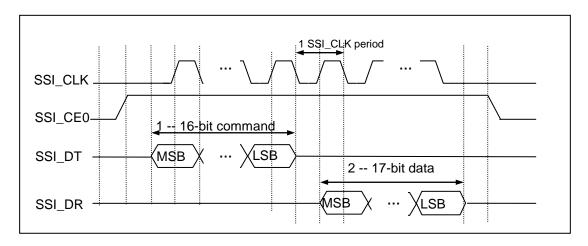

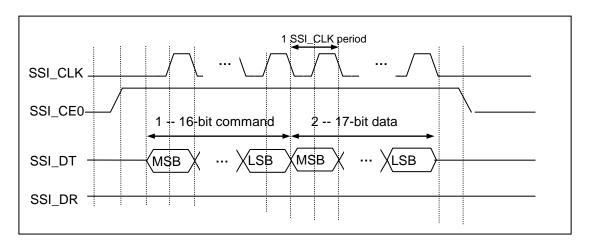

| 22.   | 6.3  | National Microwire Format Details                          | 493 |

| 22.7  | Reg  | gister Description                                         | 495 |

| 22.   | 7.1  | Register Mapping                                           | 495 |

| 22.   | 7.2  | SSI Data Register (SSIDR)                                  | 496 |

| 22.   | 7.3  | SSI Control Register0 (SSICR0)                             | 497 |

| 22.   | 7.4  | SSI Control Register1 (SSICR1)                             | 499 |

| 22.   | 7.5  | SSI Status Register (SSISR)                                | 501 |

| 22.   | 7.6  | SSI Interval Time Control Register (SSIITR)                | 502 |

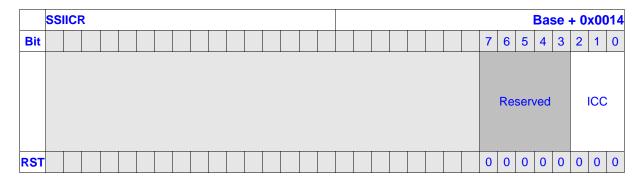

| 22.   | 7.7  | SSI Interval Character-per-frame Control Register (SSIICR) | 503 |

| 22.   | 7.8  | SSI Clock Generator Register (SSIGR)                       | 503 |

| 22.   | 7.9  | SSI Receive Counter Register (SSIRCNT)                     | 504 |

| 22.8  | Sof  | tware Guideline                                            | 504 |

| 22.   | 8.1  | Common flow                                                | 504 |

| 22.   | 8.2  | Interrupt Operation                                        | 505 |

| 22.9  | Inde | ex                                                         | 505 |

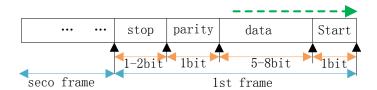

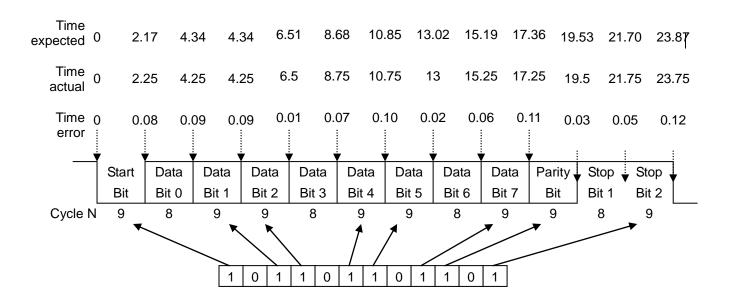

| 23 Ur | nive | rsal Asynchronous Receiver/Transmitter(uart)               | 507 |

| 23.1  | Ove  | erview                                                     | 507 |

| 23.2  | Fea  | itures                                                     | 507 |

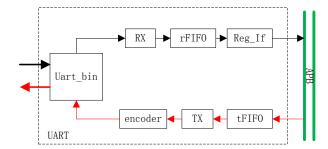

| 23.3  | Blo  | ck Diagram                                                 | 507 |

| 23.4  | Fur  | nctional Description                                       | 508 |

| 23.   | 4.1  | Full-duplex operation                                      | 508 |

| 23.   | 4.2  | The meaning of all bits                                    | 508 |

| 23.   | 4.3  | RFIFO and TFIFO                                            | 508 |

| 23.   | 4.4  | Transmission, reception and line status Independently      | 508 |

| 23.   | 4.5  | Slow infrared asynchronous interface                       |     |

| 23.5  |      | s Description                                              |     |

| 23.6  |      | a Format Description                                       |     |

|       |      |                                                            |     |

| 23.7 Reg    | ister Description                       | 509          |

|-------------|-----------------------------------------|--------------|

| 23.7.1      | Register Memory Map                     | 509          |

| 23.7.2      | Register and Fields Description         | 510          |

| 23.8 Ope    | ration Flow                             | 524          |

| 23.8.1      | UART Configuration                      | 524          |

| 23.8.2      | Data Transmission                       | 524          |

| 23.8.3      | Data Reception                          | 524          |

| 23.8.4      | Receive Error Handling                  | 525          |

| 23.8.5      | Modem Transfer                          | 525          |

| 23.8.6      | DMA Transfer                            | 525          |

| 23.8.7      | Slow IrDA Asynchronous Interface        | 525          |

| 23.8.8      | For any frequency clock to use the UART | 526          |

| 23.9 Inde   | ex                                      | 528          |

|             | CD CE ATA Combraller (MCC)              | -00          |

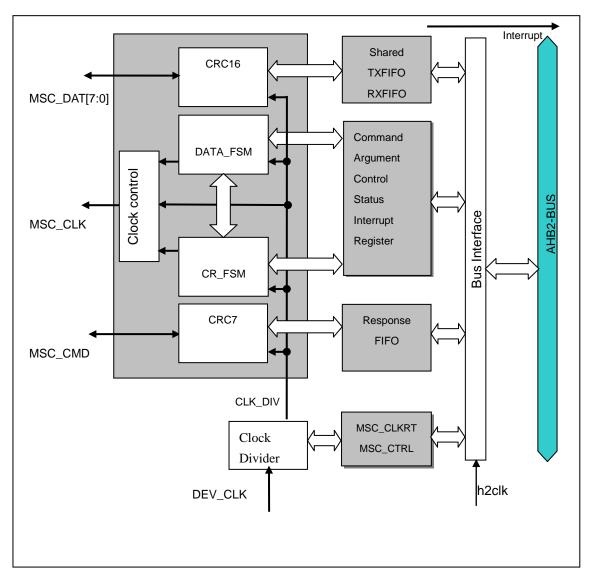

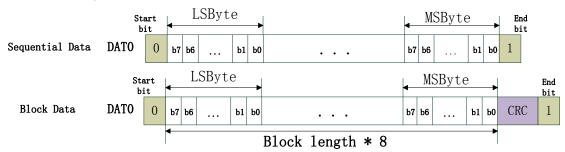

| 24 IVIIVIC/ | SD CE-ATA Controller(MSC)               | ) <b>2</b> 9 |

| 24.1 Ove    | rview                                   | 529          |

| 24.2 Fea    | tures                                   | 529          |

| 24.3 Bloc   | k Diagram                               | 530          |

| 24.4 Fun    | ctional Description                     | 530          |

| 24.4.1      | MSC Reset                               | 531          |

| 24.4.2      | Voltage Validation                      | 531          |

| 24.4.3      | Card Registry                           | 531          |

| 24.4.4      | Card Access                             | 532          |

| 24.4.5      | Protection Management                   | 534          |

| 24.4.6      | Card Status                             | 537          |

| 24.4.7      | SD Status                               | 541          |

| 24.4.8      | SDIO                                    | 541          |

| 24.4.9      | Clock Control                           | 543          |

| 24.4.10     | Application Specified Command Handling  | 543          |

| 24.5 Pins   | Description                             | 543          |

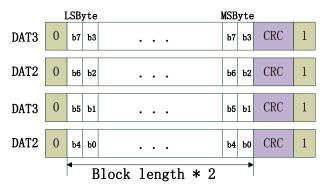

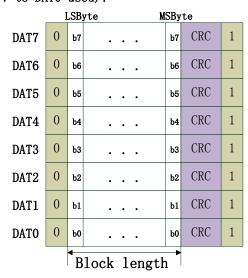

| 24.6 Data   | a Format Description                    | 544          |

| 24.7 Reg    | ister Description                       | 544          |

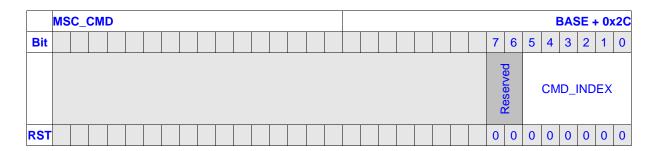

| 24.7.1      | Register Memory Map                     | 545          |

| 24.7.2      | Register and Fields Description         | 546          |

| 24.8 Ope    | ration Flow                             | 566          |

| 24.8.1      | Data FIFOs                              | 566          |

| 24.8.2      | DMA and Program I/O                     | 566          |

| 24.8.3      | Start and Stop clock                    | 568          |

| 24.8.4      | Software Reset                          | 569          |

| 24.8.5      | Voltage Validation and Card Registry    | 569          |

| 24.8.6      | Single Data Block Write                 | 571          |

| 24.8.7      | Single Block Read                       | 572          |

| 24.8.8      | Multiple Block Write                    | 572          |

| 24.8.9    | Multiple Block Read                     | 573 |

|-----------|-----------------------------------------|-----|

| 24.8.10   | Stream Write (MMC)                      | 574 |

| 24.8.11   | Stream Read (MMC)                       | 575 |

| 24.8.12   | Erase, Select/Deselect and Stop         | 575 |

| 24.8.13   | SDIO Suspend/Resume                     | 576 |

| 24.8.14   | SDIO Read Wait                          | 576 |

| 24.8.15   | Operation and Interrupt                 | 576 |

| 24.9 Inde | ex                                      | 577 |

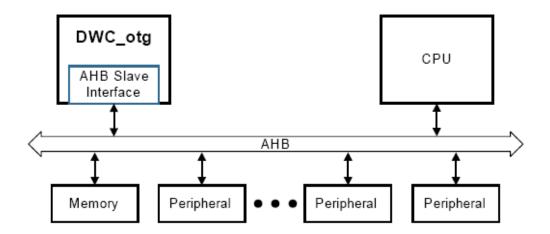

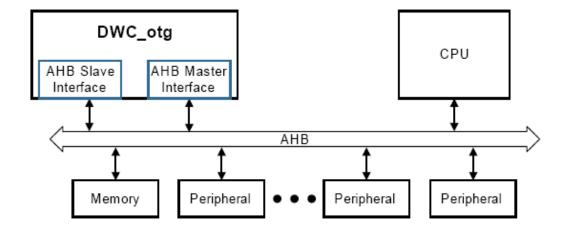

| 25 OTG (  | Controller                              | 579 |

| 25.1 Ove  | erview                                  | 579 |

|           | ck Diagram                              |     |

| 25.2.1    | Slave-Only mode                         | 580 |

| 25.2.2    | Internal DMA mode                       | 580 |

| 25.3 Pin  | Description                             | 580 |

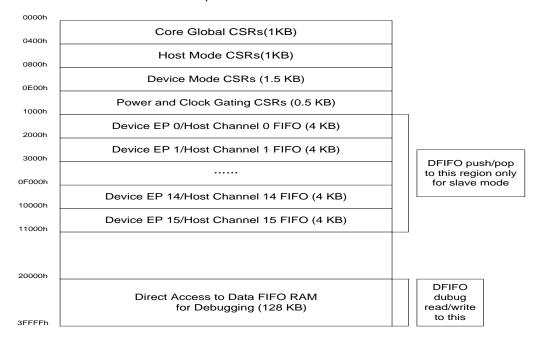

| 25.4 Reg  | jister Map                              | 581 |

| 25.4.1    | CSR Memory Map                          | 581 |

| 25.4.2    | Register Maps                           | 581 |

| 25.4.3    | Global CSR Map                          | 582 |

| 25.4.4    | Host Mode CSR Map                       | 583 |

| 25.4.5    | Device Mode CSR Map                     | 583 |

| 25.4.6    | Data FIFO (DFIFO) Access Register Map   | 585 |

| 25.5 Reg  | gister Descriptions                     | 586 |

| 25.5.1    | Application Access to the CSRs          | 586 |

| 25.5.2    | Overview of Commonly Used Register Bits | 587 |

| 25.5.3    | Global Registers                        | 591 |

| 25.5.4    | Host Mode Registers                     | 629 |

| 25.5.5    | Device Mode Registers                   | 647 |

| 25.6 Ope  | eration Flow                            | 680 |

| 25.6.1    | Core Initialization                     | 680 |

| 25.6.2    | Programming the Device Core             | 681 |

| 25.6.3    | Programming the Host Core               | 684 |

| 26 MAC.   |                                         | 686 |

| 26.1 Fea  | tures                                   | 686 |

|           | Section 8 Boot                          |     |

|           | Coolon C Boot                           |     |

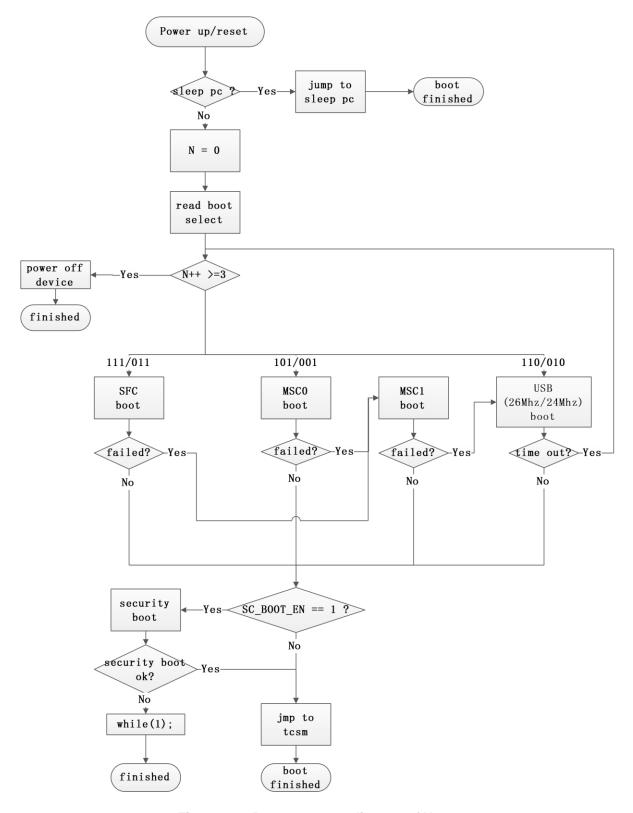

| 27 XBurs  | t Boot ROM Specification                | 688 |

| 27.1 Boo  | t Select                                | 688 |

| 27.2 Boo  | t Procedure                             | 688 |

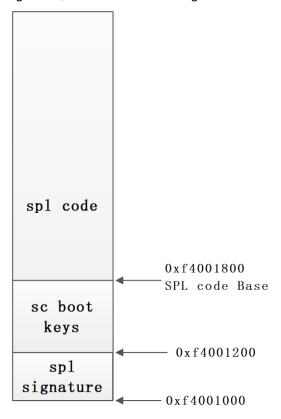

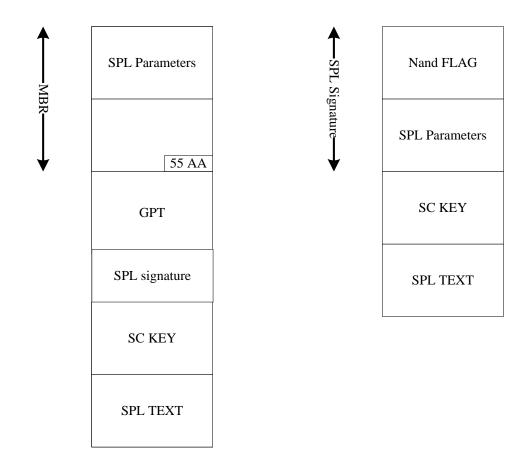

| 27.3 SPI  | _ Structure                             | 690 |

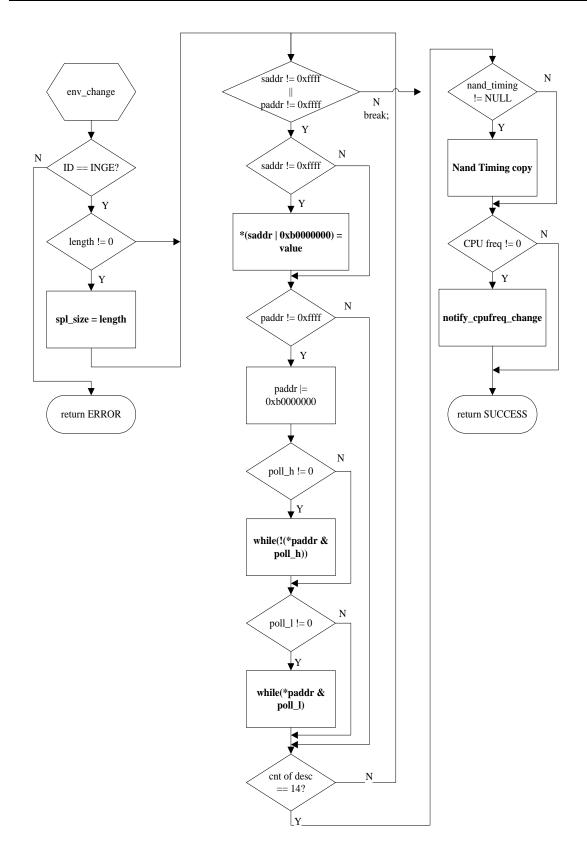

| 27.4 SPI  | Paramaters                              | 690 |

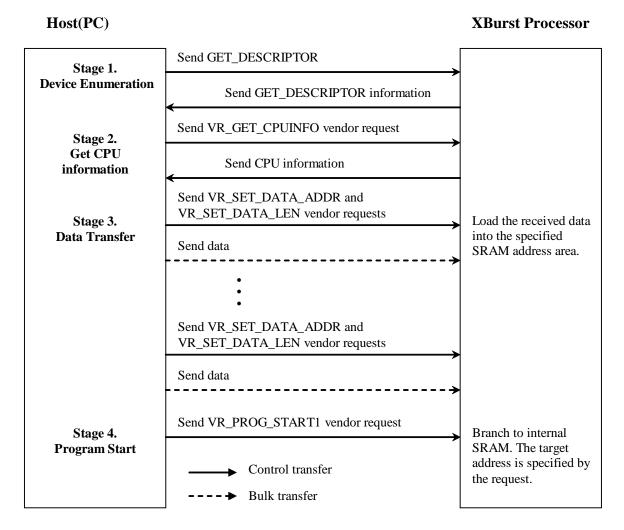

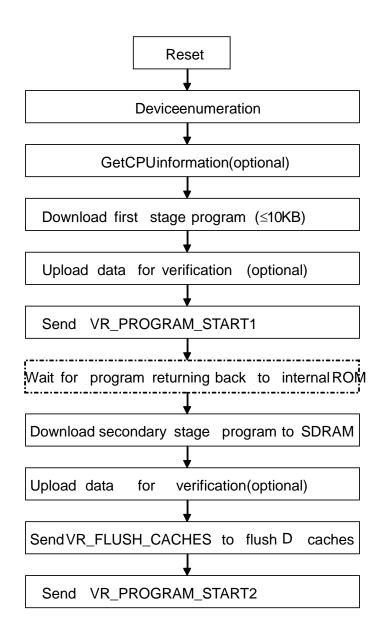

| 27.5 | USB Boot Specification  | . 694 |

|------|-------------------------|-------|

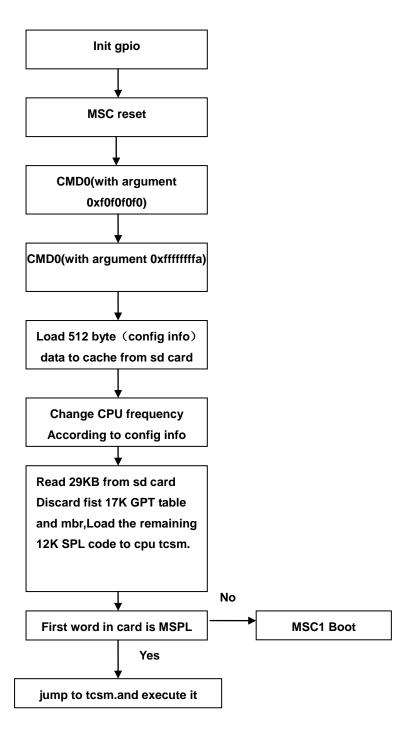

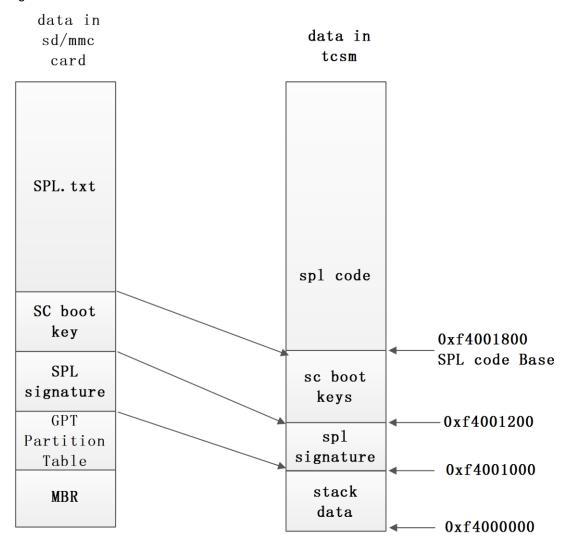

| 27.6 | MSC0 Boot Specification | . 698 |

| 27.7 | MSC1 boot Specification | . 700 |

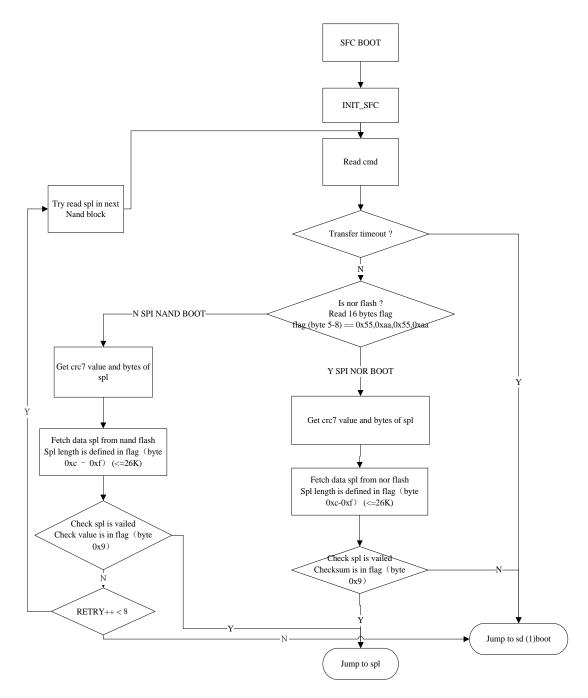

| 27.8 | SFC boot Specification  | . 700 |

# **TABLES**

| Table 4-1 SLCD Pins Description                                                      | 31  |

|--------------------------------------------------------------------------------------|-----|

| Table 4-2 Registers Memory Map-Address Base                                          | 33  |

| Table 4-3 SLCD Controller Registers Description                                      | 33  |

| Table 5-1 Camera Interface Pins Description                                          | 62  |

| Table 5-2 CIM Registers                                                              | 62  |

| Table 5-3 The modes and the corresponding signals used                               | 74  |

| Table 6-1 AIC Pins Description                                                       | 82  |

| Table 6-2 AIC Registers Description                                                  | 83  |

| Table 6-3 Sample data bit relate to SDATA_IN/SDATA_OUT bit                           | 101 |

| Table 6-4 Audio Sampling rate, BIT_CLK and SYS_CLK frequencies                       | 111 |

| Table 6-5 BIT_CLK divider setting                                                    | 112 |

| Table 6-6 Approximate common multiple of SYS_CLK for all sample rates                | 113 |

| Table 6-7 CPM/AIC clock divider setting for various sampling rate if PLL = 270.64MHz | 113 |

| Table 6-8 PLL parameters and audio sample errors for EXCLK=12MHz                     | 114 |

| Table 7-1 PCM Interface Pins Description                                             | 117 |

| Table 7-2 Registers Memory Map-Address Base                                          | 119 |

| Table 7-3 PCM Registers Description                                                  | 119 |

| Table 8-1 CODEC signal IO pin description                                            | 132 |

| Table 8-2 Internal CODEC Mapped Registers Description (AIC Registers)                | 135 |

| Table 8-3 Microphone/Line input performances                                         | 200 |

| Table 8-4 I/O buffer static characteristics                                          | 201 |

| Table 8-5 I/O buffer dynamic characteristics                                         | 201 |

| Table 9-1 DDRC Register                                                              | 205 |

| Table 10-1 I/O Pin Description                                                       | 245 |

| Table 10-2 SFC Registers Map                                                         | 247 |

| Table 10-3 Terms and Abbreviations                                                   | 263 |

| Table 11-1 Registers Memory Map-Address Base                                         | 267 |

| Table 11-2 CGU Registers Configuration                                               | 267 |

| Table 11-3 Power/Reset Management Controller Registers Configuration                 | 295 |

| Table 12-1 PWM Pins Description                                                      | 306 |

| Table 12-2 Registers Memory Map-Address Base                                         | 307 |

| Table 12-3 TCU Registers Configuration                                               | 307 |

| Table 13-1 Registers Memory Map-Address Base                                         | 328 |

| Table 13-2 SYS_OST Registers Configuration                                           | 329 |

| Table 14-1 Registers Memory Map-Address Base                                         | 336 |

| Table 14-2 INTC Register                                                             | 336 |

| Table 15-1 Registers Memory Map-Address Base                                         | 344 |

| Table 15-2 WDT Registers Configuration                                               | 345 |

| Table 16-1 Registers Memory Map-Address Base                                         | 349 |

| Table 16-2 DMA Channel Registers (n=0~31)                                            | 349 |

| Table 16-3 Registers Memory Map-Address Base                                         | 350 |

| Table 16-4 Global Control Registers                           | 350 |

|---------------------------------------------------------------|-----|

| Table 16-5 Transfer Request Types                             | 352 |

| Table 16-6 Available RDIL                                     | 354 |

| Table 16-7 TCSM space                                         | 364 |

| Table 16-8 Descriptor Structure                               | 367 |

| Table 17-1 Registers Memory Map-Address Base                  | 374 |

| Table 17-2 Registers for real time clock                      | 374 |

| Table 17-3 Registers for hibernating mode                     | 374 |

| Table 17-4 Clock select registers                             | 386 |

| Table 19-1 GPIO port summary table illustration               | 395 |

| Table 19-2 GPIO Port A summary                                | 396 |

| Table 19-3 GPIO Port B summary                                | 397 |

| Table 19-4 GPIO Port C summary                                | 398 |

| Table 19-5 GPIO Port D summary                                | 398 |

| Table 19-6 Registers Memory Map-Address Base                  | 399 |

| Table 19-7 GPIO Registers                                     | 400 |

| Table 20-1 SMB Pin Description                                | 443 |

| Table 20-2 Registers Memory Map-Address Base                  | 444 |

| Table 20-3 Registers Memory Map-Address Offset                | 444 |

| Table 21-1 Smart Card Controller Pins Description             | 481 |

| Table 21-2 Smart Card Controller Registers Description        | 481 |

| Table 22-1 SSI Controller Pins Description                    | 488 |

| Table 22-2 SSI Serial Port Registers                          | 496 |

| Table 22-3 SSI Interrupts                                     | 505 |

| Table 23-1 UART Pins Description                              | 508 |

| Table 23-2 Registers Memory Map Base Address                  | 509 |

| Table 23-3 UART Registers Map                                 | 510 |

| Table 23-4 UART Interrupt Identification Register Description | 514 |

| Table 23-5 Description of Proprietary Vocabulary              | 528 |

| Table 24-1 Command Data Block Structure                       | 535 |

| Table 24-2 Card Status Description                            | 538 |

| Table 24-3 SD Status Structure                                | 541 |

| Table 24-4 Registers Memory Map Base Address                  |     |

| Table 24-5 MSC Registers Map                                  | 545 |

| Table 24-6 How to stop multiple block write                   | 573 |

| Table 24-7 How to stop multiple block read                    | 573 |

| Table 24-8 Description of Proprietary Vocabulary              | 577 |

| Table 24-9 The mapping between Commands and Steps             | 577 |

| Table 25-1 OTG Pins Description                               | 580 |

| Table 25-2 Registers Memory Map Base Address                  | 581 |

| Table 25-3 Core Global CSR Map (000h-3FFh)                    |     |

| Table 25-4 Host Mode CSR Map (400h-7FFh)                      |     |

| Table 25-5 Device Mode CSR Map (800h-BFFh)                    | 583 |

| Table 25-6 Data FIFO (DFIFO) Access Register Map                                     | 585 |

|--------------------------------------------------------------------------------------|-----|

| Table 25-7 List of Commonly Used Register Bits                                       | 587 |

| Table 25-8 Control and Status Register: GOTGCTL                                      | 591 |

| Table 25-9 Interrupt Register: GOTGINT                                               | 595 |

| Table 25-10 AHB Configuration Register: GAHBCFG                                      | 596 |

| Table 25-11 USB Configuration Register: GUSBCFG                                      | 600 |

| Table 25-12 Reset Register: GRSTCTL                                                  | 605 |

| Table 25-13 Interrupt Register: GINTSTS                                              | 608 |

| Table 25-14 Interrupt Mask Register: GINTMSK                                         | 615 |

| Table 25-15 Host Mode Receive Status Debug Read/Status Read and Pop Registers:       |     |

| GRXSTSR/GRXSTSP                                                                      | 617 |

| Table 25-16 Device Mode Receive Status Debug Read/Status Read and Pop Registers:     |     |

| GRXSTSR/GRXSTSP                                                                      | 617 |

| Table 25-17 Receive FIFO Size Register: GRXFSIZ                                      | 618 |

| Table 25-18 Non-Periodic Transmit FIFO Size Register: GNPTXFSIZ (Host Mode and Devi  | ce  |

| Shared FIFO Mode)                                                                    | 619 |

| Table 25-19 Non-Periodic Transmit FIFO Size Register: GNPTXFSIZ (Device Dedicated FI | FO  |

| Mode)                                                                                | 619 |

| Table 25-20 Non-Periodic Transmit FIFO/Queue Status Register: GNPTXSTS               | 619 |

| Table 25-21 User HW Config1 Register: GHWCFG1                                        | 620 |

| Table 25-22 User HW Config2 Register: GHWCFG2                                        | 621 |

| Table 25-23 User HW Config3 Register: GHWCFG3                                        | 623 |

| Table 25-24 User HW Config4 Register: GHWCFG4                                        | 625 |

| Table 25-25 Global DFIFO Software Config Register: GDFIFOCFG                         | 627 |

| Table 25-26 Host Periodic Transmit FIFO Size Register: HPTXFSIZ                      | 628 |

| Table 25-27 Device Periodic Transmit FIFO-n Register: DPTXFSIZn                      | 628 |

| Table 25-28 Device In Endpoint Transmit FIFO Size Register: (DIEPTXFn)               | 629 |

| Table 25-29 Host Configuration Register: HCFG                                        | 630 |

| Table 25-30 Host Frame Interval Register: HFIR                                       | 632 |

| Table 25-31 Host Frame Number/Frame Time Remaining Register: HFNUM                   | 633 |

| Table 25-32 Host Periodic Transmit FIFO/Queue Status Register: HPTXSTS               | 633 |

| Table 25-33 Host All Channels Interrupt Register: HAINT                              | 634 |

| Table 25-34 Host All Channels Interrupt Mask Register: HAINTMSK                      | 634 |

| Table 25-35 Host Port Control and Status Register: HPRT                              | 635 |

| Table 25-36 Host Channel-n Characteristics Register: HCCHARn                         | 638 |

| Table 25-37 Host Channel-n Split Control Register: HCSPLTn                           | 640 |

| Table 25-38 Host Channel-n Interrupt Register: HCINTn                                | 641 |

| Table 25-39 Host Channel-n Interrupt Mask Register: HCINTMSKn                        | 643 |

| Table 25-40 Host Channel-n Transfer Size Register: HCTSIZn                           | 644 |

| Table 25-41 Host Channel-n DMA Address Register: HCDMAn                              | 646 |

| Table 25-42 Host Channel-n DMA Buffer Address Register: HCDMABn                      | 647 |

| Table 25-43 Host Frame List Base Address Register: HFLBAddr                          | 647 |

| Table 25-44 Device Configuration Register: DCFG                                      | 648 |

| Table 25-45 device Control Register: DCTL                                      | 650 |

|--------------------------------------------------------------------------------|-----|

| Table 25-46 Minimum Duration for Soft Disconnect                               | 654 |

| Table 25-47 Device Status Register: DSTS                                       | 654 |

| Table 25-48 Device IN Endpoint Common Interrupt Mask Register: DIEPMSK         | 656 |

| Table 25-49 Device OUT Endpoint Common Interrupt Mask Register: DOEPMSK        | 656 |

| Table 25-50 Device All Endpoints Interrupt Register: DAINT                     | 657 |

| Table 25-51 Device Endpoints Interrupt Mask Register: DAINTMSK                 | 658 |

| Table 25-52 Device IN Token Sequence Learning Queue Read Register 1: DTKNQR1   | 658 |

| Table 25-53 Device IN Token Sequence Learning Queue Register 2: DTKNQR2        | 659 |

| Table 25-54 Device IN Token Sequence Learning Queue Register 3: DTKNQR3        | 659 |

| Table 25-55 Device IN Token Sequence Learning Queue Register 4: DTKNQR4        | 659 |

| Table 25-56 Device VBUS Discharge Time Register: DVBUSDIS                      | 660 |

| Table 25-57 Device VBUS Pulsing Time Register (DVBUSPULSE)                     | 660 |

| Table 25-58 Device Threshold Control Register (DTHRCTL)                        | 661 |

| Table 25-59 Device IN Endpoint FIFO Empty Interrupt Mask Register: DIEPEMPMSK  | 662 |

| Table 25-60 Device Each Endpoint Interrupt Register: DEACHINT                  | 663 |

| Table 25-61 Device Each Endpoint Interrupt Register Mask: DEACHINTMSK          | 663 |

| Table 25-62 Device Each In Endpoint-n Interrupt Register: DIEPEACHMSKn         | 664 |

| Table 25-63 Device Each Out Endpoint-n Interrupt Register: DOEPEACHMSKn        | 665 |

| Table 25-64 Device Control IN Endpoint 0 Control Register: DIEPCTL0            | 665 |

| Table 25-65 Device OUT Endpoint 0 Control Register: DOEPCTL0                   | 667 |

| Table 25-66 Device Endpoint-n Control Register: DIEPCTLn/DOEPCTLn              | 669 |

| Table 25-67 Device Endpoint-n Interrupt Register: DIEPINTn/DOEPINTn            | 673 |

| Table 25-68 Device IN Endpoint 0 Transfer Size Register: DIEPTSIZ0             | 676 |

| Table 25-69 Device OUT Endpoint 0 Transfer Size Register: DOEPTSIZ0            | 677 |

| Table 25-70 Device Endpoint-n Transfer Size Register: DIEPTSIZn/DOEPTSIZn      | 677 |

| Table 25-71 Device Endpoint-n DMA Address Register: DIEPDMAn/DOEPDMAn          | 679 |

| Table 25-72 Device Endpoint-n DMA Buffer Address Register: DIEPDMABn/DOEPDMABn | 679 |

| Table 25-73 Device IN Endpoint Transmit FIFO Status Register: DTXFSTSn         | 680 |

| Table 27-1 Boot Configuration of X1000                                         | 688 |

| Table 27-2 SPL parameters structure                                            | 691 |

| Table 27-3 Transfer Types Used by the Boot Program                             | 694 |

| Table 27-4 Vendor Request 0 Setup Command Data Structure                       | 697 |

| Table 27-5 Vendor Request 1 Setup Command Data Structure                       | 697 |

| Table 27-6 Vendor Request 2 Setup Command Data Structure                       | 697 |

| Table 27-7 Vendor Request 3 Setup Command Data Structure                       | 697 |

| Table 27-8 Vendor Request 4 Setup Command Data Structure                       | 698 |

| Table 27-9 Vendor Request 5 Setup Command Data Structure                       | 698 |

| Table 27-10 SPI NOR flash boot flag informations(in spl signature)             | 702 |

| Table 27-11 SPI NAND flash boot flag informations(in spl signature)            | 702 |

# **FIGURES**

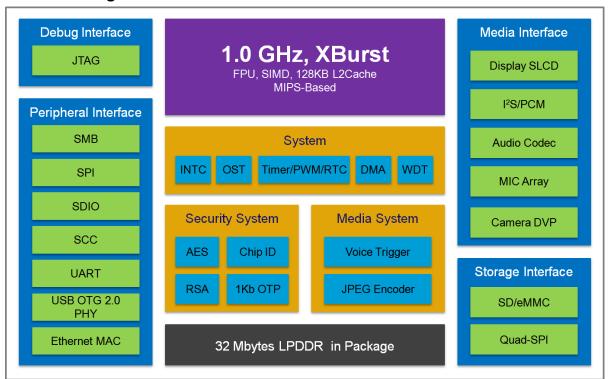

| Figure 1-1 X1000 Diagram                                                                 | 2     |

|------------------------------------------------------------------------------------------|-------|

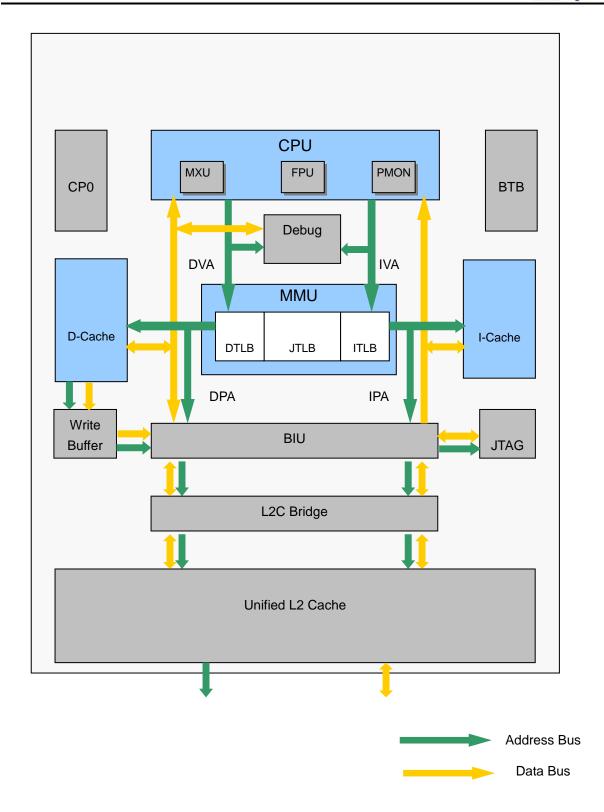

| Figure 2-1 Structure of CPU core                                                         | 12    |

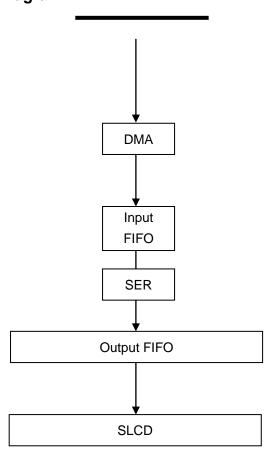

| Figure 4-1 Block Diagram of SLCD                                                         | 32    |

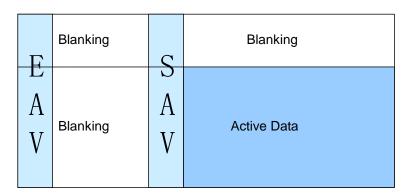

| Figure 5-1 ITU656 Progressive Mode                                                       | 76    |

| Figure 6-1 AIC Block Diagram                                                             | 80    |

| Figure 6-2 Interface to an External Master Mode I2S/MSB-Justified CODEC Diagram          | 81    |

| Figure 6-3 Interface to an External Slave Mode I2S/MSB-Justified CODEC Diagram           | 81    |

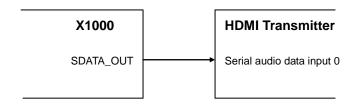

| Figure 6-4 Interface to a HDMI Transmitter via SPDIF Diagram                             | 82    |

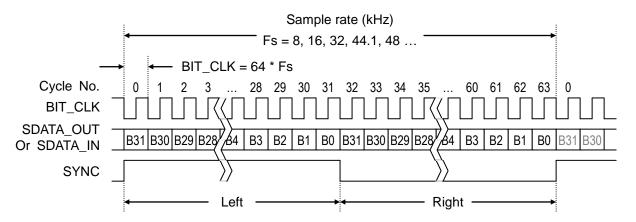

| Figure 6-5 I2S data format (A: LR mode)                                                  | 99    |

| Figure 6-6 I2S data format (B: RL mode)                                                  | 100   |

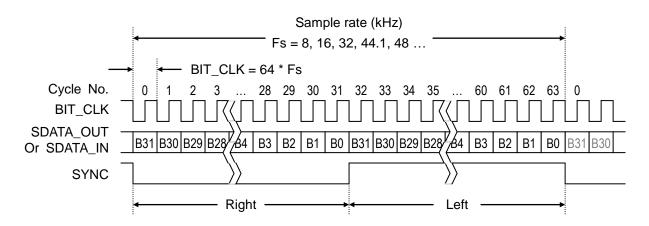

| Figure 6-7 MSB-justified data format (C: LR mode)                                        | 100   |

| Figure 6-8 MSB-justified data format (D: RL mode)                                        | 100   |

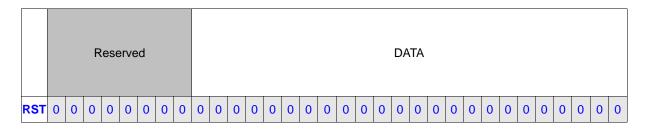

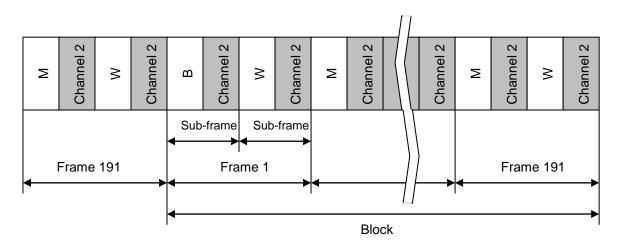

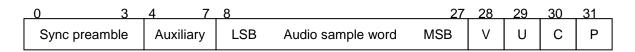

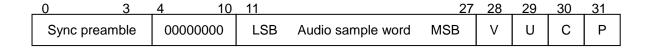

| Figure 6-9 Block format                                                                  | 102   |

| Figure 6-10 Sub-frame format in PCM mode                                                 | 102   |

| Figure 6-11 Sub-frame format in non-PCM mode                                             | 103   |

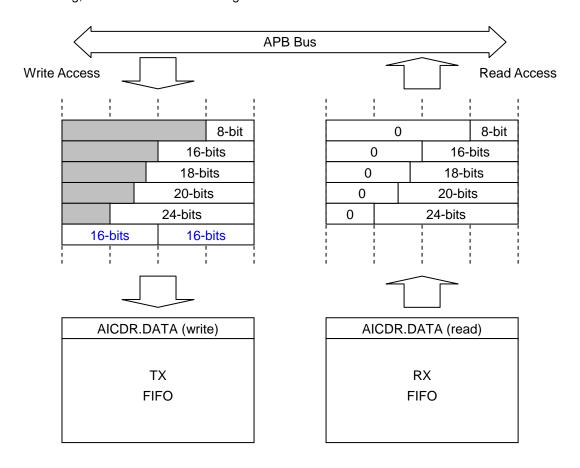

| Figure 6-12 Transmitting/Receiving FIFO access via APB Bus                               | 106   |

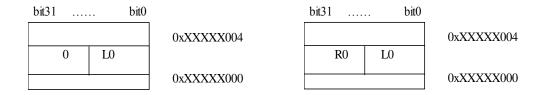

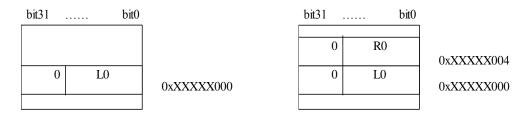

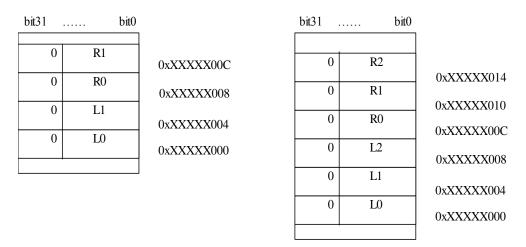

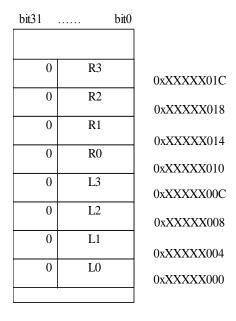

| Figure 6-13 One channel (Left) and Two channels (right) mode (16 bits packed mode)       | 108   |

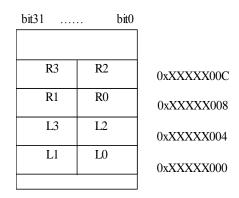

| Figure 6-14 Four channels (Left) and Six channels (right) mode (16 bits packed mode)     | 109   |

| Figure 6-15 Eight channels mode (16 bits packed mode)                                    | 109   |

| Figure 6-16 One channel (Left) and Two channels (right) mode                             | 109   |

| Figure 6-17 Four channels (Left) and Six channels (right) mode                           | 110   |

| Figure 6-18 Eight channels mode                                                          | 110   |

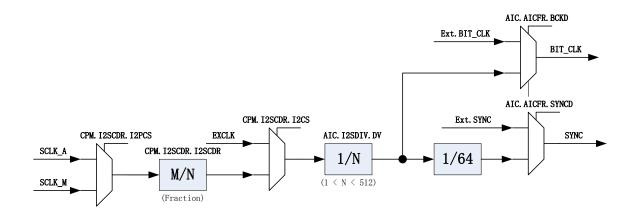

| Figure 6-19 SYS_CLK, BIT_CLK and SYNC generation scheme                                  | 112   |

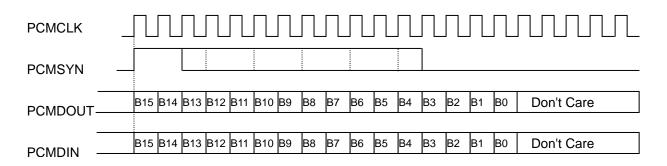

| Figure 7-1 Short Frame SYN Timing (Shown with 16bit Sample)                              | 125   |

| Figure 7-2 Short Frame SYN Timing (Shown with 16bit Sample)                              | 125   |

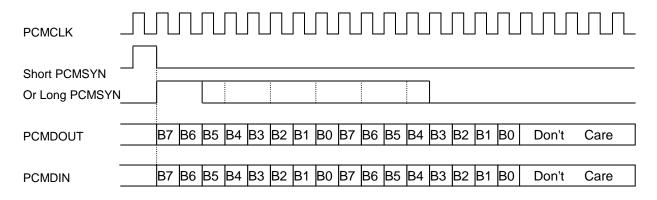

| Figure 7-3 Long Frame SYN Timing (Shown with 16bit Sample)                               | 126   |

| Figure 7-4 Long Frame SYN Timing (Shown with 16bit Sample)                               | 126   |

| Figure 7-5 Multi-Slot Frame SYN Timing (Shown with two Slots and 8bit Sample)            | 126   |

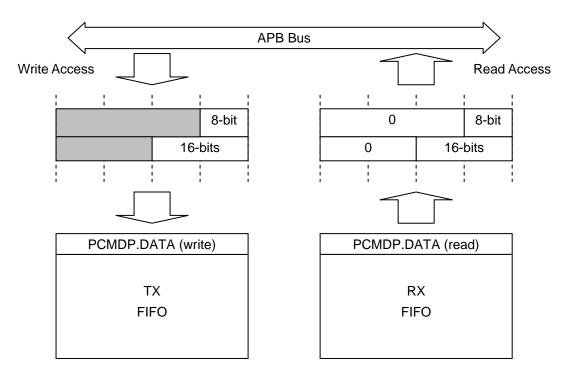

| Figure 7-6 Transmitting/Receiving FIFO access via APB Bus                                | 129   |

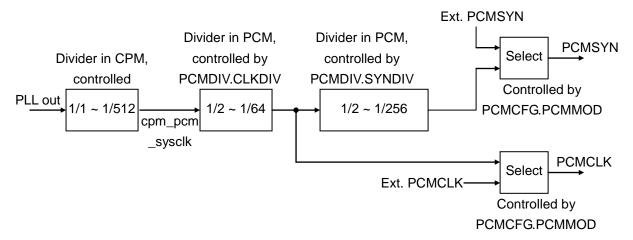

| Figure 7-7 PCMCLK and PCMSYN generation scheme                                           | 130   |

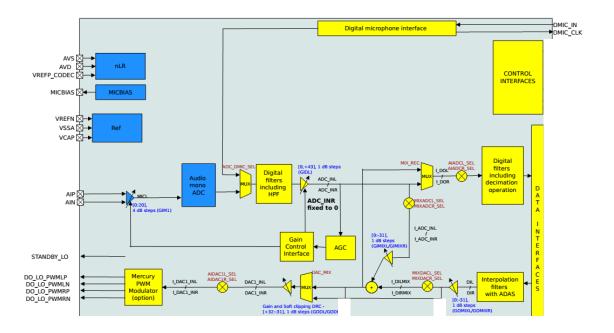

| Figure 8-1 CODEC block diagram                                                           | 133   |

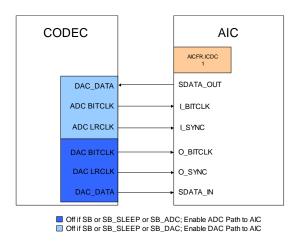

| Figure 8-2 Internal CODEC works with AIC                                                 | 133   |

| Figure 8-3 AGC adjusting waves                                                           | 181   |

| Figure 8-4 AGC adjust areas                                                              | 182   |

| Figure 8-5 signal above threshold at the output of the soft clipping DRC                 | 183   |

| Figure 8-6 Digital Mixer structure                                                       | 183   |

| Figure 8-7 Digital microphone interface connection                                       | 185   |

| Figure 8-8 Digital microphone timing diagram at MCLK = 12 MHz (DMIC_CLK = 3 MHz)         | 185   |

| Figure 8-9 Digital microphone modulation noise reference spectrum (with FFT resolution = | 20 Hz |

| and 7 terms Blackman-Harris windowing)                                                   | 186   |

| Figure 8-10 PSNT2 for VDDIO_CODEC when using PWM output                                  | 187   |

| Figure 8-11 PSNT2 for VDDIO_CODEC when using PWM output                                     | 187 |

|---------------------------------------------------------------------------------------------|-----|

| Figure 8-12 CODEC Power Diagram1                                                            | 188 |

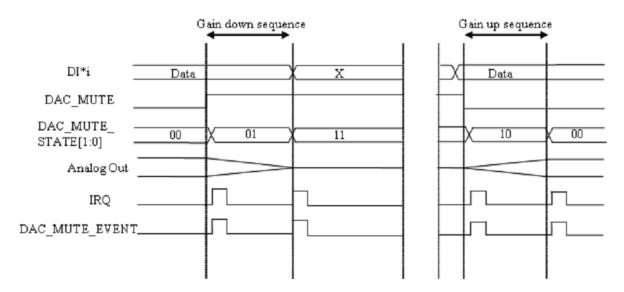

| Figure 8-13 ADC Gain up and gain down sequence1                                             | 189 |

| Figure 8-14 DAC Gain up and gain down sequence1                                             | 190 |

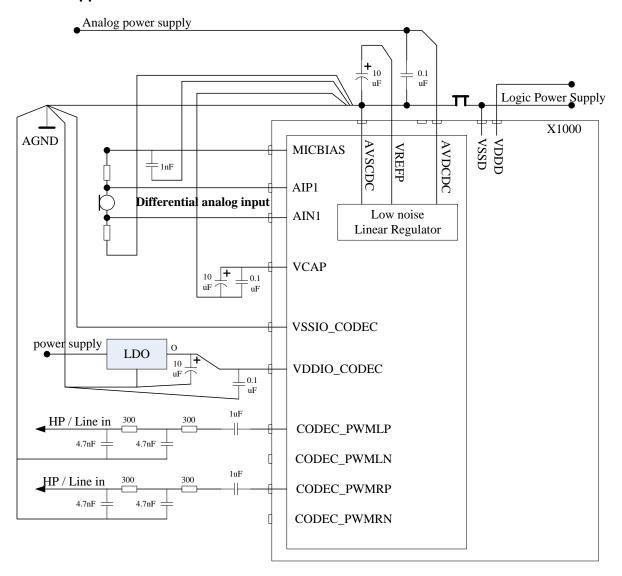

| Figure 8-15 Peripheral power supply connection1                                             | 193 |

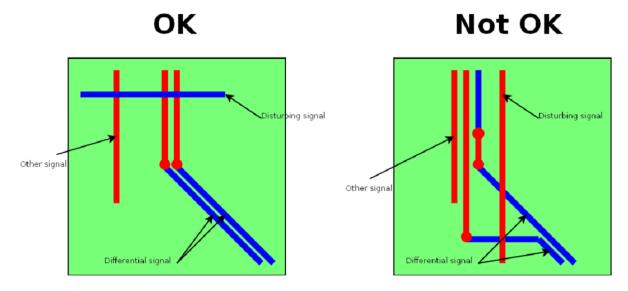

| Figure 8-16 Differential routing                                                            | 196 |

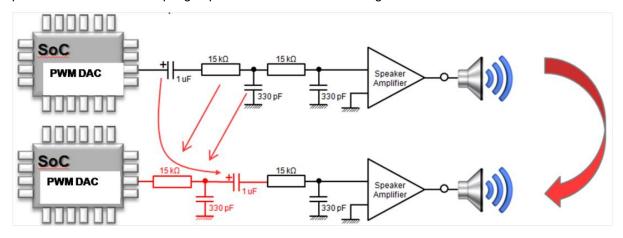

| Figure 8-17 PCB optimization for avoiding EMI issue                                         | 197 |

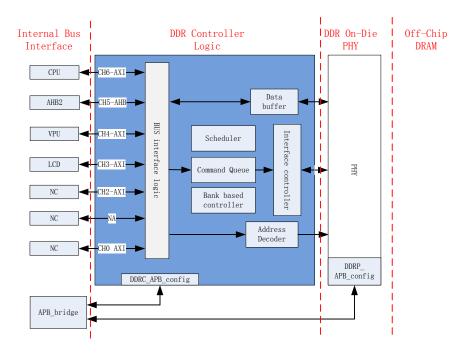

| Figure 9-1 DDR system block diagram                                                         | 205 |

| Figure 10-1 SFC Block Diagram                                                               | 243 |

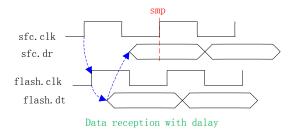

| Figure 10-2 Sample point(no delay)2                                                         | 244 |

| Figure 10-3 Sample point(has delay)2                                                        | 244 |

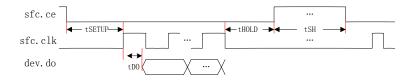

| Figure 10-4 AC timing                                                                       |     |

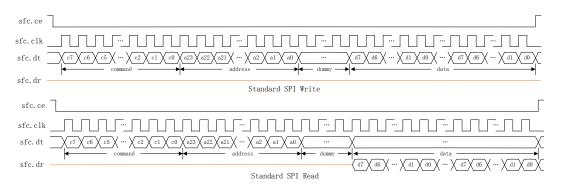

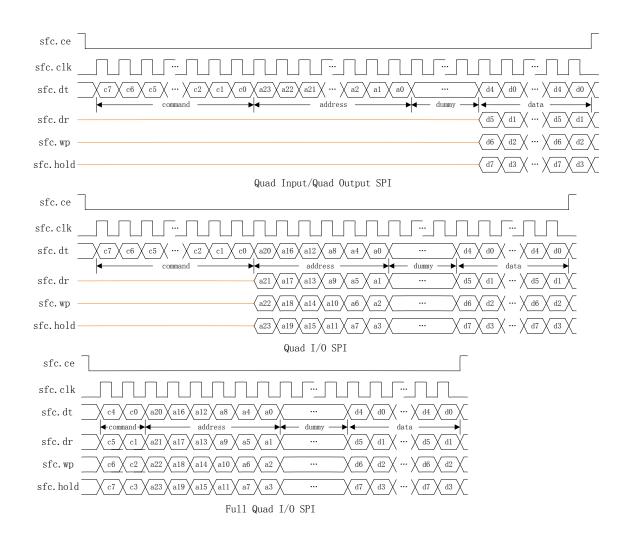

| Figure 10-5 Data Format(Standard SPI)                                                       | 245 |

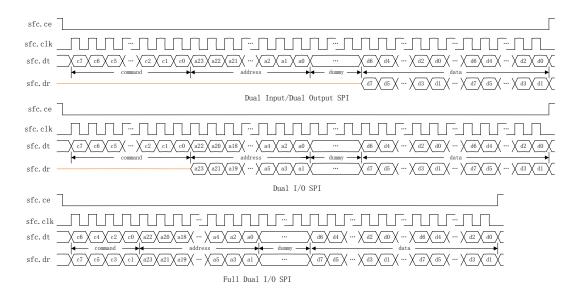

| Figure 10-6 Data Format(Dual SPI)                                                           | 245 |

| Figure 10-7 Data Format(Quad SPI)                                                           | 246 |

| Figure 10-8 Multi phases flow                                                               | 259 |

| Figure 10-9 One phase flow                                                                  | 260 |

| Figure 11-1 Block Diagram of PLL                                                            | 293 |

| Figure 16-1 Block Diagram of PDMA                                                           | 348 |

| Figure 16-2 Descriptor Transfer Flow                                                        | 368 |

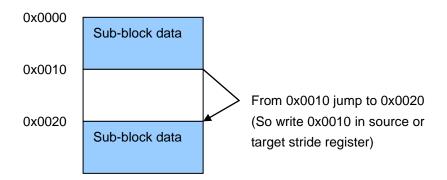

| Figure 16-3 Example for Stride Transfer Mode                                                | 369 |

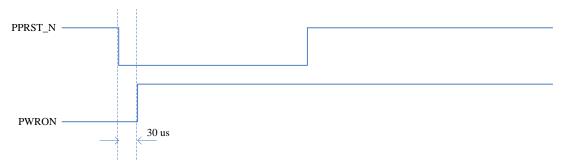

| Figure 17-1 Core Power On                                                                   |     |