# 1024 BIT (256x4) STATIC CMOS RAM

#### DESCRIPTION

The µPD5101L and µPD5101L-1 are very low power 1024 bit (256 words by 4 bits) static CMOS Random Access Memories. They meet the low power requirements of battery operated systems and can be used to ensure non-volatility of data in systems using battery backup power.

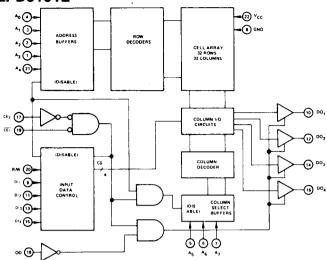

All inputs and outputs of the µPD5101L and µPD5101L-1 are TTL compatible. Two chip enables (CE<sub>1</sub>, CE<sub>2</sub>) are provided, with the devices being selected when CE<sub>1</sub> is low and CE2 is high. The devices can be placed in standby mode, drawing 10  $\mu$ A maximum, by driving CE<sub>1</sub> high and inhibiting all address and control line transitions. The standby mode can also be selected unconditionally by driving CE2 low.

The  $\mu$ PD5101L and  $\mu$ PD5101L-1 have separate input and output lines. They can be used in common I/O bus systems through the use of the OD (Output Disable) pin and OR-tying the input/output pins. Output data is the same polarity as input data and is nondestructively read out. Read mode is selected by placing a high on the R/W pin. Either device is guaranteed to retain data with the power supply voltage as low as 2.0 volts. Normal operation requires a single +5 volt supply.

The µPD5101L and µPD5101L-1 are fabricated using NEC's silicon gate complementary MOS (CMOS) process.

- FEATURES Directly TTL Compatible All Inputs and Outputs

- Three-State Output

- Access Time 650 ns (µPD5101L); 450 ns (µPD5101L-1)

- Single +5V Power Supply

- CE2 Controls Unconditional Standby Mode

- For operation at +3V Power Supply, Contact the NEC Sales Office.

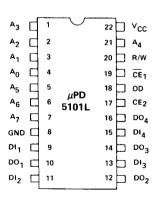

#### PIN CONFIGURATION

#### **PIN NAMES**

| DI1 - DI4                         | Data Input       |

|-----------------------------------|------------------|

| A <sub>0</sub> - A <sub>7</sub>   | Address Inputs   |

| R/W                               | Read/Write Input |

| CE <sub>1</sub> , CE <sub>2</sub> | Chip Enables     |

| OD                                | Output Disable   |

| DO1 - DO4                         | Data Output      |

| Vcc                               | Power (+5V)      |

|                                   |                  |

# μPD5101L

**BLOCK DIAGRAM**

www.Data Operating Temperature

0°C to +70°C

Storage Temperature

-40°C to +125°C

Voltage On Any Pin With Respect to Ground

-0.3 Volts to V<sub>CC</sub> +0.3 Volts

Power Supply Voltage

-0.3 to +7.0 Volts

$T_a = 25^{\circ}C$

\*COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$T_a = 0^{\circ}C$  to  $70^{\circ}C$ ;  $V_{CC} = +5V \pm 5\%$ , unless otherwise specified.

|                     |                  | LIMITS |       |      |      |                                                                                  |

|---------------------|------------------|--------|-------|------|------|----------------------------------------------------------------------------------|

| PARAMETER           | SYMBOL           | MIN    | түр 🛈 | MAX  | UNIT | TEST CONDITIONS                                                                  |

| Input High Leakage  | ILIH ②           |        |       | 1    | μА   | V <sub>IN</sub> = V <sub>CC</sub>                                                |

| Input Low Leakage   | 1111             |        |       | -1   | μА   | V <sub>IN</sub> = 0∨                                                             |

| Output High Leakage | 1LOH2            |        |       | 1    | μА   | CE <sub>1</sub> = 2.2V, V <sub>OUT</sub> = V <sub>CC</sub>                       |

| Output Low Leakage  | LOL ②            |        |       | - 1  | μА   | CE <sub>1</sub> = 2.2V, V <sub>OUT</sub> = 0.0V                                  |

| Operating Current   | <sup>1</sup> CC1 |        |       | 22   | mA   | V <sub>IN</sub> = V <sub>CC</sub> Except CE <sub>1</sub><br>≤0.65V, Outputs Open |

| Operating Current   | ICC2             |        |       | 27   | mΑ   | V <sub>IN</sub> = 2.2V Except CE <sub>1</sub><br>≤0.65V, Outputs Open            |

| Standby Current     | 'ccl②            |        |       | 10   | μА   | V <sub>1N</sub> = 0 to 5.25V<br>CE <sub>2</sub> ≤ 0.2V                           |

| Input Low Voltage   | VIL              | -0.3   |       | 0.65 | V    |                                                                                  |

| Input High Voltage  | VIH              | 2.2    |       | Vcc  | V    |                                                                                  |

| Output Low Voltage  | VOL              |        |       | 0.4  | ٧    | I <sub>OL</sub> = 2.0 mA                                                         |

| Output High Voltage | V <sub>OH1</sub> | 2.4    |       |      | ٧    | I <sub>OH</sub> =1.0 mA                                                          |

| Output High Voltage | V <sub>OH2</sub> | 3.5    |       |      | ٧    | I <sub>OH</sub> = -100 μA                                                        |

- Notes: 1 Typical values at T<sub>a</sub> = 25°C and nominal supply voltage.

- 2 Current through all inputs and outputs included in ICCL.

|                                       |                 |     | LIMITS |     |      |                       |

|---------------------------------------|-----------------|-----|--------|-----|------|-----------------------|

| PARAMETER                             | SYMBOL          | MIN | TYP    | MAX | UNIT | TEST CONDITIONS       |

| Input Capacitance<br>(All Input Pins) | C <sub>IN</sub> |     | 4      | 8   | pF   | VIN OV                |

| Output<br>Capacitance                 | COUT            |     | 8      | 12  | pF   | V <sub>OUT</sub> - 0V |

ABSOLUTE MAXIMUM RATINGS\*

DC CHARACTERISTICS

CAPACITANCE

$T_a = 0^{\circ}C$  to  $70^{\circ}C$ ;  $V_{CC} = 5V\pm5\%$ , unless otherwise specified

|                                                               |                  |       | LIMITS |     |         |     |     |      |                                             |

|---------------------------------------------------------------|------------------|-------|--------|-----|---------|-----|-----|------|---------------------------------------------|

| PARAMETER                                                     | SYMBOL           | 5101L |        |     | 5101L-1 |     |     | UNIT | TEST CONDITIONS                             |

|                                                               |                  | MIN   | TYP    | MAX | MIN     | ΤΥ₽ | MAX |      |                                             |

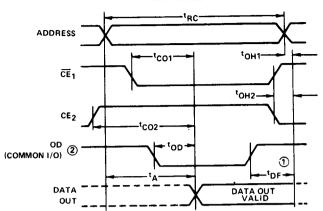

| Read Cycle                                                    | <sup>t</sup> RC  | 650   |        |     | 450     |     |     | ns   | Input pulse amplitude:<br>0,65 to 2,2 Volts |

| Access Time                                                   | t <sub>A</sub>   |       |        | 650 |         |     | 450 | ns   | Input rise and fall                         |

| Chip Enable (CE <sub>1</sub> )<br>to Output                   | <sup>t</sup> CO1 |       |        | 600 |         |     | 400 | ns   | times: 20 ns                                |

| Chip Enable (CE <sub>2</sub> )<br>to Output                   | tCO2             |       |        | 700 |         |     | 500 | ns   | Timing measurement reference level:         |

| Output Disable to<br>Output                                   | tOD              |       |        | 350 |         |     | 250 | ns   | 1,5 Volt Output load: ITTL                  |

| Data Output to<br>High Z State                                | <sup>†</sup> DF  | 0     |        | 150 | 0       |     | 130 | ns   | Gate and C <sub>L</sub> = 100 pF            |

| Previous Read Data<br>Valid with Respect<br>to Address Change | <sup>t</sup> OH1 | 0     |        |     | 0       |     |     | ns   |                                             |

| Previous Read Data<br>Valid with Respect<br>to Chip Enable    | <sup>t</sup> OH2 | 0     |        |     | 0       |     |     | ns   |                                             |

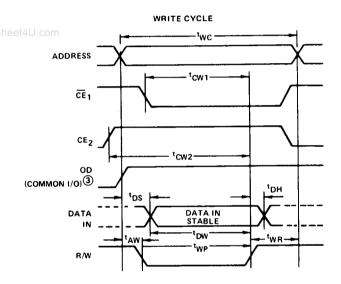

### WRITE CYCLE

$T_a = 0^{\circ}C$  to  $70^{\circ}C$ ;  $V_{CC} = 5V \pm 5\%$ , unless otherwise specified

|                                            |                 |       |     | LIM | IITS    |     |     |      |                                     |

|--------------------------------------------|-----------------|-------|-----|-----|---------|-----|-----|------|-------------------------------------|

| PARAMETER                                  | SYMBOL          | 5101L |     |     | 5101L-1 |     |     | UNIT | TEST CONDITIONS                     |

|                                            |                 | MIN   | TYP | MAX | MIN     | TYP | MAX |      |                                     |

| Write Cycle                                | tWC             | 650   |     |     | 450     |     |     | ns   | Input pulse amplitude:              |

| Write Delay                                | <sup>t</sup> AW | 150   |     |     | 130     |     |     | ns   | 0.65 to 2.2 Volts                   |

| Chip Enable (CE <sub>1</sub> )<br>to Write | †CW1            | 550   |     |     | 350     |     |     | ' ns | Input rise and fall<br>times: 20 ns |

| Chip Enable (CE <sub>2</sub> )<br>to Write | tCW2            | 550   |     |     | 350     |     |     | ns   | Timing measurement reference level: |

| Data Setup                                 | ¹DW             | 400   |     |     | 250     |     |     | ns   | 1.5 Volt                            |

| Data Hold                                  | ¹DH             | 100   |     |     | 50      |     |     | ns   | Output load: ITTL                   |

| Write Pulse                                | twp             | 400   |     |     | 250     |     |     | ns   | Gate and C <sub>1</sub> =           |

| Write Recovery                             | twn             | 50    |     |     | 50      |     |     | ns   | 100 pF                              |

| Output Disable Setup                       | tD\$            | 150   |     |     | 130     |     |     |      |                                     |

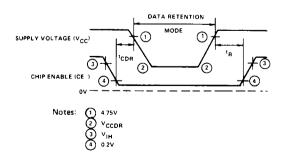

# LOW VCC DATA RETENTION Ta = 0°C to 70°C CHARACTERISTICS

|                             |                  | LIMITS |     |     | <u> </u> |                                                      |

|-----------------------------|------------------|--------|-----|-----|----------|------------------------------------------------------|

| PARAMETER                   | SYMBOL           | MIN    | TYP | MAX | UNIT     | TEST CONDITIONS                                      |

| VCC for Data<br>Retention   | VCCDR            | +2.0   |     |     | ٧        | CE <sub>2</sub> ≤ +0.2V                              |

| Data Retention<br>Current   | ICCDR            |        |     | +10 | μА       | V <sub>CCDR</sub> = +2.0V<br>CE <sub>2</sub> ≤ +0.2V |

| Chip Deselect<br>Setup Time | <sup>†</sup> CDR | 0      |     |     | ns       |                                                      |

| Chip Deselect<br>Hold Time  | ₹R               | tRCÛ   |     |     | ns       |                                                      |

Note: 1) tRC = Read Cycle Time

TIMING WAVEFORMS

Notes: 1 Typical values are for T<sub>a</sub> = 25°C and nominal supply voltage.

OD may be tied low for separate I/O operation.

3 During the write cycle, OD is "high" for common I/O and

During the write cycle, OD is "high" for common I/O and "don't care" for separate I/O operation.

LOW  $V_{\mbox{\footnotesize{CC}}}$  DATA RETENTION

TYPICAL OPERATING CHARACTERISTICS

ww.DataSneet40.com

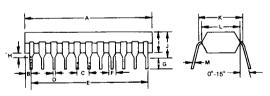

| ITEM | MILLIMETERS                   | INCHES            |

|------|-------------------------------|-------------------|

| A    | 28.0 Max.                     | 1.10 Max.         |

| В    | 1.4 Max.                      | 0.025 Max.        |

| С    | 2.54                          | 0.10              |

| ٥    | 0.50 0.10                     | 0.02 0.004        |

| E    | 25.4                          | 1.0               |

| F    | 1.40                          | 0.055             |

| G    | 2,54 Min.                     | 0.10 Min.         |

| н    | 0.5 Min.                      | 0.02 Min.         |

| _    | 4.7 Max.                      | 0.18 Max.         |

| ٠    | 5.2 Max.                      | 0.20 Max.         |

| К    | 10.16                         | 0.40              |

| L    | 8.5                           | 0.33              |

| м    | 0.25 <sup>+0.10</sup><br>0.05 | 0.01 +0.004 0.002 |

5101LDS-REV1-12-81-CAT

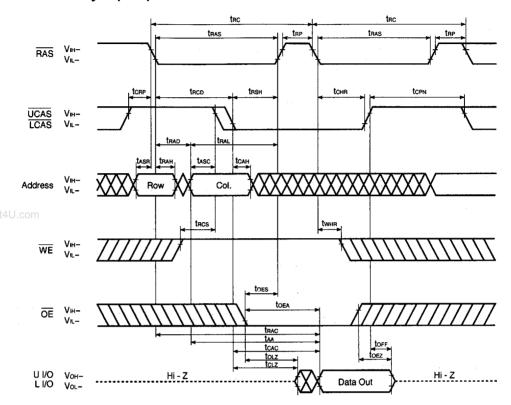

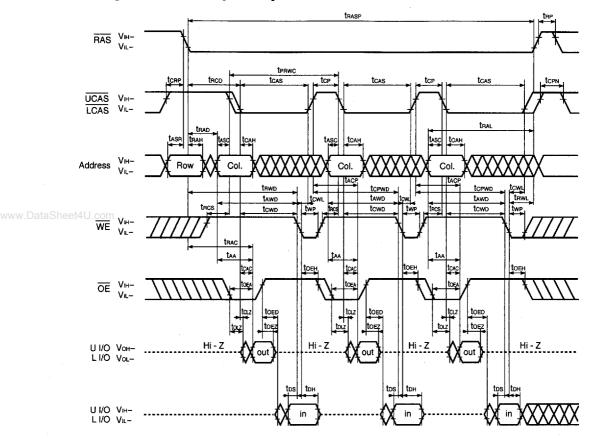

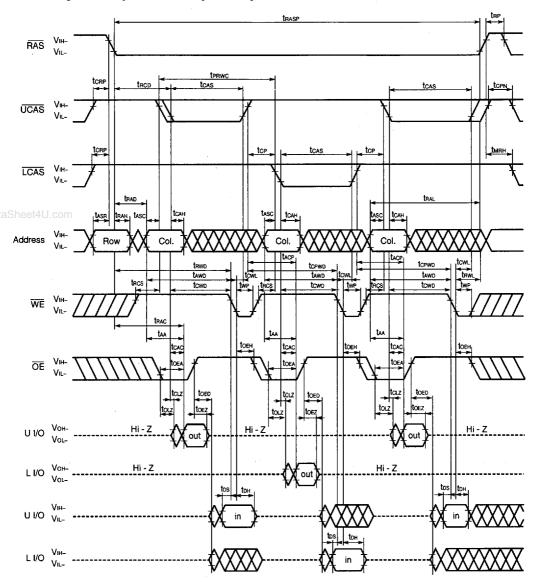

## Fast Page Mode Read Modify Write Cycle

Remark In the fast page mode, read, write and read modify write cycles are available for each of the consecutive CAS cycles within the same RAS cycle.

## Fast Page Mode Byte Read Modify Write Cycle

Remarks 1. In the fast page mode, read, write and read modify write cycles are available for each of the consecutive CAS cycles within the same RAS cycle.

2. This cycle can be used to control either UCAS or LCAS only. Or, it can be used to control UCAS or LCAS simultaneously, or at random.

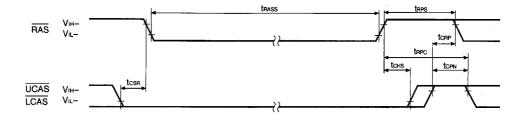

# CAS Before RAS Self Refresh Cycle (Only for the μPD42S18160)

Remark Address, WE, OE: Don't care L I/O, U I/O: Hi-Z

#### Cautions on Use of CAS Before RAS Self Refresh

CAS before RAS self refresh can be used independently when used in combination with distributed CAS before RAS long refresh; However, when used in combination with burst CAS before RAS long refresh or with long RAS only refresh (both distributed and burst), the following cautions must be observed.

(1) Normal Combined Use of CAS Before RAS Self Refresh and Burst CAS Before RAS Long Refresh

When CAS before RAS self refresh and burst CAS before RAS long refresh are used in combination, please

perform CAS before RAS refresh as follows just before and after setting CAS before RAS self refresh.

$\mu$ PD42S18160: 1,024 times within a 16 ms interval

(2) Normal Combined Use of CAS Before RAS Self Refresh and Long RAS Only Refresh

When CAS before RAS self refresh and RAS only refresh are used in combination, please perform RAS only refresh as follows just before and after setting CAS before RAS self refresh.

μPD42S18160: 1,024 times within a 16 ms interval

(3) If trass (MIN.) is not satisfied at the beginning of CAS before RAS self refresh cycles (tras < 100 μs), CAS before RAS refresh cycles will be executed one time.</p>

If 10  $\mu$ s < t<sub>RAS</sub> < 100  $\mu$ s,  $\overline{RAS}$  precharge time for  $\overline{CAS}$  before  $\overline{RAS}$  self refresh (t<sub>RPS</sub>) is applied. And refresh cycles as follows should be met.

μPD42S18160: 1,024 times within a 128 ms interval

For details, please refer to How to use DRAM User's Manual.

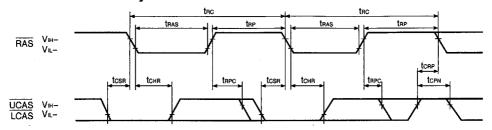

# CAS Before RAS Refresh Cycle

Remark Address, WE, OE: Don't care L I/O, U I/O: Hi-Z

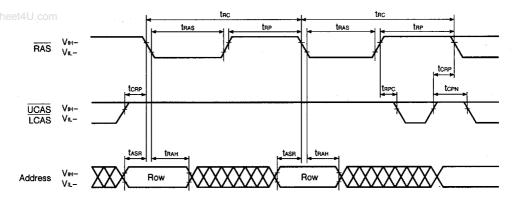

# **RAS** Only Refresh Cycle

Remark WE, OE: Don't care L I/O, U I/O: Hi-Z

## Hidden Refresh Cycle (Read)