# AN-1001 Understanding Power MOSFET Parameters

## Content

| 1. | Abso | olute Maximum Ratings                                      | 3  |

|----|------|------------------------------------------------------------|----|

|    | 1.1  | Drain-Source Voltage (VDs)                                 | 3  |

|    | 1.2  | Gate-Source Voltage (VGs)                                  | 3  |

|    | 1.3  | Continuous Drain Current (ID)                              | 3  |

|    | 1.4  | Pulsed Drain Current (Ідм)                                 | 4  |

|    | 1.5  | Single Pulse Avalanche Current (IAs)                       | 4  |

|    | 1.6  | Single Pulse Avalanche Energy (EAs)                        | 4  |

|    | 1.7  | Total Power Dissipation (PD)                               | 5  |

|    | 1.8  | Operating Junction and Storage Temperature Range (TJ,TSTG) | 5  |

| 2. | Ther | rmal Performance                                           | 6  |

|    | 2.1  | Junction To Case Thermal Resistance (ReJc)                 | 6  |

|    | 2.2  | Junction To Ambient Thermal Resistance (RፀJA)              | 6  |

| 3. | Elec | trical Specifications                                      | 7  |

|    | 3.1  | Drain-Source Breakdown Voltage (BVDss)                     | 7  |

|    | 3.2  | Gate Threshold Voltage (Vgs(тн))                           | 7  |

|    | 3.3  | Gate-Source Leakage Current (Igss)                         | 8  |

|    | 3.4  | Drain-Source Leakage Current (IDss)                        | 8  |

|    | 3.5  | Drain-Source On-State Resistance (RDS(ON))                 | 8  |

|    | 3.6  | Forward Transconductance (gfs)                             | 9  |

| 4. | Dyna | amic                                                       | 10 |

|    | 4.1  | Total Gate Charge (Qg)                                     | 10 |

|    | 4.2  | Capactance (Ciss, Coss, Crss)                              | 10 |

|    | 4.3  | Gate Resistance (Rg)                                       | 10 |

| 5. | Swit | tching Time                                                | 11 |

|    | 5.1  | Switching Time (Td(on), Tr, Td(off), Tf)                   | 11 |

| 6. | Sour | rce-Drain Diode Characteristics                            | 12 |

|    | 6.1  | Forward Voltage (Vsd)                                      | 12 |

|    | 6.2  | Body Diode Reverse Recovery (trr,Qrr)                      | 12 |

| 7. | Chai | racteristics Curves                                        | 13 |

|    | Outp | put Characteristics                                        | 13 |

|    | Tran | nsfer Characteristics                                      | 13 |

|    | Gate | e-Source Voltage vs. Gate Charge                           | 14 |

|    | On-F | Resistance vs. Junction Temperature                        | 15 |

## TAIWAN SEMICONDUCTOR

## Taiwan Semiconductor

| Source-Drain Diode Forward Current vs. Voltage            | . 16 |

|-----------------------------------------------------------|------|

| BVDss vs. Junction Temperature                            | . 16 |

| Capacitance vs. Drain-Source Voltage                      | . 17 |

| SOA                                                       | . 18 |

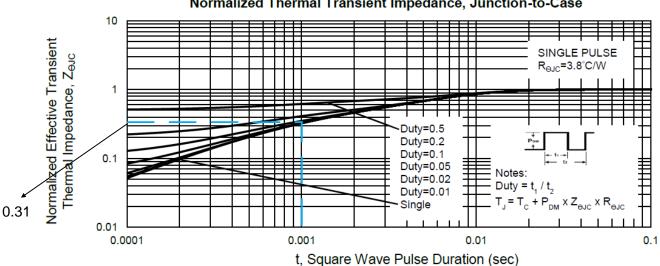

| Normalized Thermal Transient Impedance, Junction-to -Case | . 19 |

## **MOSFET datasheet parameters introduction**

## Introduction

When choosing a MOSFET, parameters that are focused on by most engineers intuitively are  $V_{DS}$ ,  $R_{DS(on)}$ ,  $I_D$ . However, in power systems, it is significant to pick up a suitable MOSFET based on different applications. In this application note, Taiwan Semiconductor (TSC) introduces the definition of every single parameter of a MOSFET, and from chapter 3, TSC also explains how each parameter is realized, hoping this would help designers on the power projects.

## 1. Absolute Maximum Ratings

| ABSOLUTE MAXIMUM RATIN                                                     |                                   |                 |       | г           |       |

|----------------------------------------------------------------------------|-----------------------------------|-----------------|-------|-------------|-------|

| PARAMETER                                                                  |                                   | SYMBOL          | LIMIT | UNIT        | Notes |

| Drain-Source Voltage                                                       | Drain-Source Voltage              |                 |       | V           | 1.1   |

| Gate-Source Voltage                                                        |                                   | V <sub>GS</sub> | ±20   | V           | 1.2   |

| Continuous Drain Current (Note 1)                                          | T <sub>c</sub> = 25°C             |                 | 39    |             | 4.2   |

| Lontinuous Drain Current                                                   | T <sub>A</sub> = 25°C             |                 | 11    | A           | 1.3   |

| Pulsed Drain Current<br>Single Pulse Avalanche Current <sup>(Note 2)</sup> |                                   | I <sub>DM</sub> | 156   | А           | 1.4   |

|                                                                            |                                   | I <sub>AS</sub> | 15.6  | А           | 1.5   |

| Single Pulse Avalanche Energy (Note                                        | 2)                                | E <sub>AS</sub> | 36.5  | mJ          | 1.6   |

| Total Dower Dissignation                                                   | T <sub>c</sub> = 25°C             |                 | 33    | <b>\</b> A/ |       |

| Total Power Dissipation                                                    | T <sub>c</sub> = 125°C            | P <sub>D</sub>  | 6.6   | W           |       |

| Tatal David Discipation                                                    | T <sub>A</sub> = 25°C             |                 | 2.6   |             | 1.7   |

| Total Power Dissipation                                                    | T <sub>A</sub> = 125°C            | P <sub>D</sub>  | 0.5   | W           |       |

| Operating Junction and Storage Te                                          | T <sub>J</sub> , T <sub>STG</sub> | - 55 to +150    | °C    | 1.8         |       |

#### 1.1 Drain-Source Voltage ( $V_{DS}$ )

$V_{DS}$  represents MOSFET absolute maximum voltage between Drain and Source. In operations, voltage stress of Drain-Source should not exceed maximum rated value.

#### 1.2 Gate-Source Voltage (V<sub>GS</sub>)

$V_{GS}$  represents operating driver voltage between Gate and Source. In operations, voltage stress of Gate-Source should not exceed maximum rated value.

#### 1.3 Continuous Drain Current ( $I_{\text{D}}$ )

I<sub>D</sub> represents MOSFET's continuous conduction current and could be calculated by below equation.

$$I_{D} = \sqrt{\frac{T_{J} - T_{C}}{R_{\theta JC} \times R_{DS(ON)} \times K}}$$

T<sub>J</sub> = Junction Temperature

T<sub>C</sub> = Case Temperature

R<sub>DS(ON)</sub> = Drain-Source On-State Resistance

$R_{\theta JC}$  = Junction to Case Thermal Resistance

K = On-Resistance vs. Junction Temperature

#### 1.4 Pulsed Drain Current ( $I_{DM}$ )

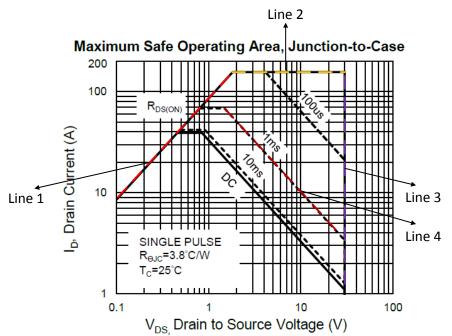

$I_{DM}$  represents maximum limit current in MOSFET SOA (Safe Operating Area ). A MOSFET could be well operated within SOA to make sure the stability and safety of a power system.

#### 1.5 Single Pulse Avalanche Current ( $I_{AS}$ )

When power MOSFET enters the avalanche mode, the current transformed into the form of voltage across Drain and Source of a MOSFET is called avalanche current ( $I_{AS}$ ).

#### 1.6 Single Pulse Avalanche Energy ( $E_{AS}$ )

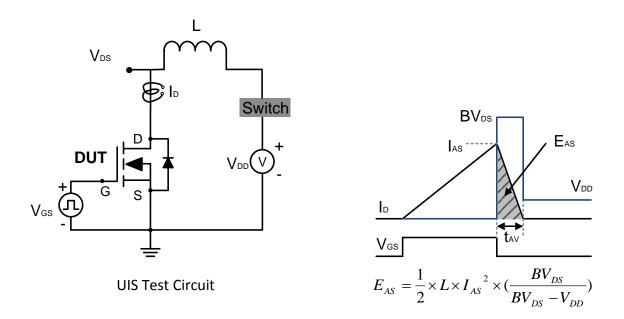

UIL (unclamped inductive load) or UIS (unclamped inductive switching) tests are important to check the degree of robustness of a power MOSFET.  $E_{AS}$  represents allowed maximum energy in either one pulse that is over rated  $V_{DS}$ . When the operating voltage exceeds the specified  $V_{DS}$  at off state of a MOSFET, it will enter the avalanche mode and cause high power dissipation. The parameter is often taken into consideration when inductive load or transient loading is operated.

The UIS test circuit: When applying a V<sub>GS</sub> signal to a DUT and the DUT is turned on, the current will start to charge Inductor (L), phenomenon of the I<sub>D</sub> current rising rate behaves linearly as above picture. When the required I<sub>D</sub> is reached to I<sub>AS</sub>, the DUT is then turned off, causing the Inductor to dissipate all of its stored energy and enforcing the DUT to reach its breakdown voltage rating. The DUT will remain in breakdown (BV<sub>DS</sub>) until all of the energy is dissipated. The blue area is E<sub>AS</sub> (Energy Avalanche Single).

#### 1.7 Total Power Dissipation ( $P_D$ )

P<sub>D</sub> represents the capability of maximum power dissipation that a MOSFET can handle. Moreover, capability of power dissipation varies by different temperature conditions.

When case temperature (T<sub>c</sub>) is considered, equation would be:

$$P_D = \frac{T_J - T_C}{R_{\theta J C}}$$

As for ambient temperature (T<sub>A</sub>), equation turns into:

$$P_D = \frac{T_J - T_A}{R_{\theta IA}}$$

T<sub>J</sub> = Junction Temperature

T<sub>c</sub> = Case Temperature

$R_{\theta JC}$  = Junction to Case Thermal Resistance

$R_{\theta JA}$  = Junction to Ambient Thermal Resistance

#### 1.8 Operating Junction and Storage Temperature Range (T<sub>J</sub>, T<sub>STG</sub>)

T<sub>J</sub> represents maximum operating temperature of a MOSFET. A MOSFET should be avoided to be operated over the rated temperature limit.

$T_{STG}$  represents the range of temperature for storage or transportation of a MOSFET. It must be storage in specified temperature values.

## 2. Thermal Performance

| THERMAL PERFORMANCE                    |                  |       |      |       |  |  |  |  |

|----------------------------------------|------------------|-------|------|-------|--|--|--|--|

| PARAMETER                              | SYMBOL           | LIMIT | UNIT | Notes |  |  |  |  |

| Junction to Case Thermal Resistance    | R <sub>ejc</sub> | 3.8   | °C/W | 2.1   |  |  |  |  |

| Junction to Ambient Thermal Resistance | R <sub>OJA</sub> | 48    | °C/W | 2.2   |  |  |  |  |

#### 2.1 Junction To Case Thermal Resistance ( $R_{\Theta JC}$ )

$R_{\Theta JC}$  is the sum of the junction to case thermal resistances. The case thermal reference is defined at the solder mounting surface of the drain pins.

#### 2.2 Junction To Ambient Thermal Resistance ( $R_{\Theta JA}$ )

$R_{\Theta JA}$  is the sum of the junction to case and case to ambient thermal resistances. The case thermal reference is defined at the solder mounting surface of the drain pins.  $R_{\Theta JA}$  is guaranteed by design while  $R_{\Theta CA}$  is determined by the user's board design.

## 3. Electrical Specifications

| ELECTRICAL SPECIFICATIONS (T <sub>A</sub> = 25°C unless otherwise noted) |                                                       |                        |     |      |      |      |       |  |

|--------------------------------------------------------------------------|-------------------------------------------------------|------------------------|-----|------|------|------|-------|--|

| PARAMETER                                                                | CONDITIONS                                            | SYMBOL                 | MIN | ТҮР  | ΜΑΧ  | UNIT | Notes |  |

| Static                                                                   | Static                                                |                        |     |      |      |      |       |  |

| Drain-Source Breakdown Voltage                                           | $V_{GS} = 0V, I_{D} = 250 \mu A$                      | BV <sub>DSS</sub>      | 30  |      |      | V    | 3.1   |  |

| Gate Threshold Voltage                                                   | $V_{GS} = V_{DS}, I_{D} = 250 \mu A$                  | V <sub>GS(TH)</sub>    | 1.2 | 1.9  | 2.5  | V    | 3.2   |  |

| Gate-Source Leakage Current                                              | $V_{GS} = \pm 20V, V_{DS} = 0V$                       | I <sub>GSS</sub>       |     |      | ±100 | nA   | 3.3   |  |

|                                                                          | $V_{GS} = 0V, V_{DS} = 30V$                           | I <sub>DSS</sub>       |     |      | 1    |      |       |  |

| Drain-Source Leakage Current                                             | $V_{GS} = 0V, V_{DS} = 30V$<br>T <sub>J</sub> = 125°C |                        |     |      | 100  | μΑ   | 3.4   |  |

| Drain-Source On-State Resistance                                         | V <sub>GS</sub> = 10V, I <sub>D</sub> = 11A           | R <sub>DS(on)</sub>    |     | 8.3  | 11.7 |      |       |  |

| (Note 3)                                                                 | V <sub>GS</sub> = 4.5V, I <sub>D</sub> = 11A          |                        |     | 11.9 | 14.9 | mΩ   | 3.5   |  |

| Forward Transconductance (Note 3)                                        | V <sub>DS</sub> = 5V, I <sub>D</sub> = 11A            | <b>g</b> <sub>fs</sub> |     | 35   |      | S    | 3.6   |  |

#### 3.1 Drain-Source Breakdown Voltage ( BV<sub>DSS</sub> )

To measure breakdown voltage of a MOSFET, at first, short Gate pin and Source pin, and then, supply the  $I_D=250\mu A$ , and monitor the reading of  $V_{DS}$ .

$BV_{DSS}$  is determined when  $I_D$  reaches 250  $\mu A.$  Gate pin is shorted to Source pin.

#### 3.2 Gate Threshold Voltage ( $V_{GS(TH)}$ )

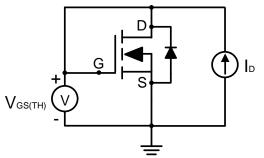

To measure gate threshold voltage of a MOSFET, at first, short Gate pin and Drain pin, and then, with a given  $I_D=250\mu$ A, and monitor the voltage difference between Gate-Source. One significant characteristics of  $V_{GS(TH)}$  is its negative temperature coefficient. If power system has to be operated at a certain minus degree, to avoid unpredicted being turned on,  $V_{GS(TH)}$  needs to be taken into consideration.

$V_{GS(TH)}$  is determined when I<sub>D</sub> reaches 250µA. Gate pin is shorted to Drain pin.

#### 3.3 Gate-Source Leakage Current ( $I_{GSS}$ )

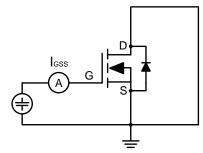

To measure Gate-Source leakage current of a MOSFET, at first, short Drain pin and Source pin, and then, apply maximum allowable voltage on Gate-Source and monitor the leakage current of Gate-Source. I<sub>GSS</sub> is dependent on the structure and design of the gate oxide.

I<sub>GSS</sub> is determined when maximum V<sub>GS</sub> voltage is applied. Drain pin is shorted to source pin

#### 3.4 Drain-Source Leakage Current ( I<sub>DSS</sub> )

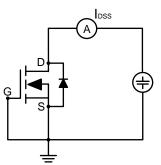

To measure Drain-Source leakage current of a MOSFET, at first, short Gate pin and Source pin, and then, apply maximum allowable voltage on Drain-Source and monitor the leakage current of Drain-Source.

I<sub>DSS</sub> is determined when maximum V<sub>DS</sub> voltage is applied. Gate pin is shorted to Source pin

#### 3.5 Drain-Source On-State Resistance (RDS(on))

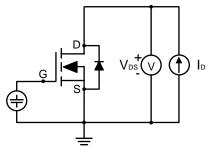

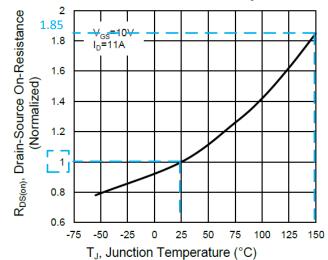

To measure Drain-Source on resistance,  $R_{DS(on)}$ , at first, apply a voltage across Gate-Source, which is specified to be higher than  $V_{GS(TH)}$ . With a given current source,  $I_D$ , measure the voltage drop across Drain-Source,  $V_{DS}$ . And after that, through the equation,  $R_{DS(on)} = V_{DS} / I_D$ ,  $R_{DS(on)}$  is observed. In TSC MOSFET datasheet, two additional figures are introduced as well. One is  $R_{DS(on)}$  vs  $V_{GS}$  graph since  $R_{DS(on)}$  varies by different amplitude of  $V_{GS}$ . The other one is  $R_{DS(on)}$  vs  $T_J$ . Characteristics of  $R_{DS(on)}$  is positive temperature coefficient. It is important to consider the surrounding temperature of selecting a MOSFET in a power system.

Apply specified  $V_{GS}$ , and given  $I_{D}$  measured  $V_{DS}$  of a MOSFET, then  $R_{DS(on)}$  is obtained

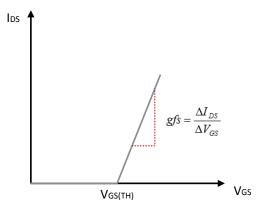

#### 3.6 Forward Transconductance ( $g_{fs}$ )

Forward transconductance,  $g_{fs}$ , represents the signal gain (drain current divided by gate voltage) of a MOSFET. Higher  $g_{fs}$  indicates the high current ( $I_{DS}$ ) handling capability can be gained from the low gate voltage ( $V_{GS}$ ). It is also expressed as below equation.

| Dynamic <sup>(Note 4)</sup>  |                                                                                           |                  |     |     |     |    |     |

|------------------------------|-------------------------------------------------------------------------------------------|------------------|-----|-----|-----|----|-----|

| Total Gate Charge            | $V_{GS} = 10V, V_{DS} = 15V, I_D$<br>= 11A<br>$V_{GS} = 4.5V, V_{DS} = 15V, I_D$<br>= 11A | Q <sub>g</sub>   |     | 9.2 |     |    |     |

| Total Gate Charge            |                                                                                           | Qg               |     | 4.5 |     | nC | 4.1 |

| Gate-Source Charge           |                                                                                           | $Q_{gs}$         |     | 1.9 |     |    |     |

| Gate-Drain Charge            | - 11A                                                                                     | $Q_{gd}$         |     | 1.7 |     |    |     |

| Input Capacitance            |                                                                                           | C <sub>iss</sub> |     | 562 |     |    |     |

| Output Capacitance           | $V_{GS} = 0V, V_{DS} = 15V$<br>f = 1.0MHz                                                 | C <sub>oss</sub> |     | 144 |     | pF | 4.2 |

| Reverse Transfer Capacitance | T = 1.0WHZ                                                                                | C <sub>rss</sub> |     | 50  |     |    |     |

| Gate Resistance              | f = 1.0MHz, open drain                                                                    | R <sub>g</sub>   | 0.5 | 1.7 | 3.4 | Ω  | 4.3 |

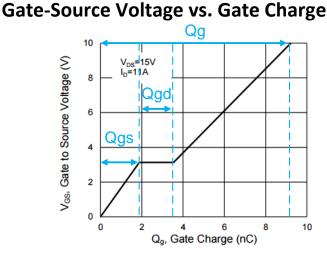

#### 4.1 Total Gate Charge ( $Q_{\rm g}$ )

Gate charge plays prominently in high frequency switching applications. Total gate charge  $Q_g$  include  $Q_{gs}$  and  $Q_{gd}$ .  $Q_{gs}$  represents the accumulation of Gate-Source capacitance while  $Q_{gd}$  is the accumulation of Gate-Drain capacitance, also called miller capacitor. In high frequency operations,  $Q_g$  should be selected as small as possible. Another tip of Gate charge for picking up a MOSFET in H-bridge power system design is that ratio of  $Q_{gd}/Q_{gs}$  be lower than 1 to prevent the circuit from shoot through.

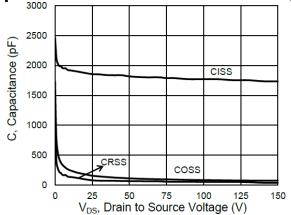

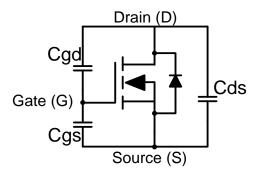

#### 4.2 Capacitances ( C<sub>iss</sub>, C<sub>oss</sub>, C<sub>rss</sub> )

C<sub>iss</sub>, C<sub>oss</sub>, and C<sub>rss</sub>, like gate charge, also influence on switching performance. In TSC MOSFET Datasheet, either one would be tested at various Drain-Source voltages and under 1MHz frequency conditions. Relationships of MOSFET capacitances are listed below.

$$C_{iss} = C_{gs} + C_{gd}$$

$$C_{oss} = C_{ds} + C_{gd}$$

$$C_{rss} = C_{gd}.$$

#### 4.3 Gate Resistance ( $R_{\rm g}$ )

R<sub>g</sub> is designed and implemented inside gate area. And with the help of MOSFET embedded Rg, the external gate drive circuit could be simplified.

## 5. Switching time

| Switching (Note 4)  |                                                                  |                     |  |      |  |    |     |  |

|---------------------|------------------------------------------------------------------|---------------------|--|------|--|----|-----|--|

| Turn-On Delay Time  | $V_{GS} = 10V, V_{DS} = 15V,$<br>$I_{D} = 7A, R_{G} = 10\Omega,$ | t <sub>d(on)</sub>  |  | 8.4  |  | ns |     |  |

| Turn-On Rise Time   |                                                                  | t <sub>r</sub>      |  | 4.3  |  |    |     |  |

| Turn-Off Delay Time |                                                                  | t <sub>d(off)</sub> |  | 22.4 |  |    | 5.1 |  |

| Turn-Off Fall Time  |                                                                  | t <sub>f</sub>      |  | 3.1  |  |    |     |  |

#### 5.1 Switching Time ( $t_{d(on)}$ , $t_r$ , $t_{d(off)}$ , $t_f$ )

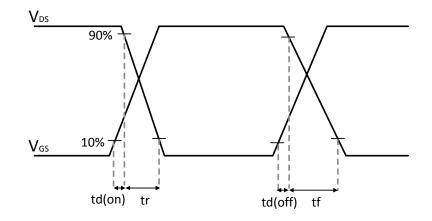

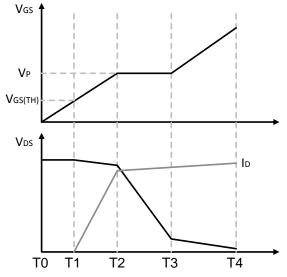

Switching time includes  $t_{d(on)}$ ,  $t_r$ ,  $t_{d(off)}$ , and  $t_f$  four main parameters and also represent important impact on switching loss of MOSFET. Each one is described as below.

#### $t_{d(on)}$ – Turn-on Delay Time

The turn-on delay time is defined as the time interval measured between 10% of  $V_{GS}$  rising from zero and 90% of  $V_{DS}$  falling from rated voltage.

#### t<sub>r</sub> – Rise Time

$t_r$  represents the time interval between  $V_{DS}$  falling from 90% to 10% of rated voltage.  $I_D$  starts to rise and is considered to be the major turn-on losses during this period.

#### $t_{d(off)} - \text{Turn-off Delay Time}$

The turn-off delay time is defined as the time interval measured between 10% of  $V_{DS}$  rising from zero and 90% of  $V_{GS}$  falling from rated voltage.

#### t<sub>f</sub> – Fall Time -

$t_f$  represents the time interval between  $V_{DS}$  rising from 10% to 90% of rated voltage.  $I_D$  starts to fall and is considered to be the major turn-off losses during this period.

## 6. Source-Drain Diode Characteristics

| Source-Drain Diode       |                                            |                 |  |      |     |    |     |  |

|--------------------------|--------------------------------------------|-----------------|--|------|-----|----|-----|--|

| Forward Voltage (Note 3) | V <sub>GS</sub> = 0V, I <sub>S</sub> = 11A | V <sub>SD</sub> |  |      | 1.2 | V  | 6.1 |  |

| Reverse Recovery Time    | I <sub>s</sub> = 11A ,                     | t <sub>rr</sub> |  | 14.7 |     | ns |     |  |

| Reverse Recovery Charge  | dl/dt = 100A/µs                            | Q <sub>rr</sub> |  | 7.3  |     | nC | 6.2 |  |

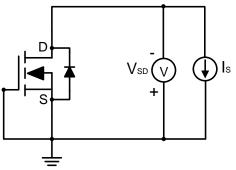

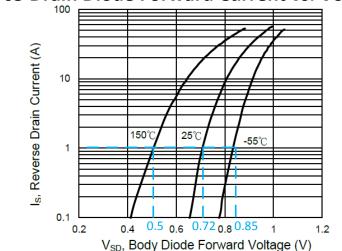

#### 6.1 Forward Voltage (VsD)

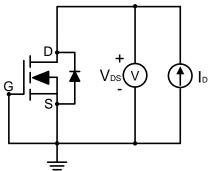

To measure Source-Drain voltage, VSD, at first, short Gate pin and Source pin. Apply a specified reverse current,  $I_S$ , and  $V_{SD}$  is measured.

The  $V_{SD}$  is measured by applying  $I_S$  current. Gate pin is shorted to Source pin.

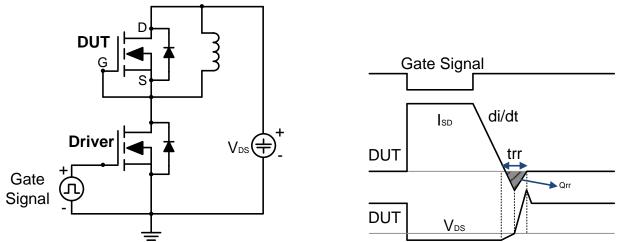

#### 6.2 Body Diode Reverse Recovery ( $t_{rr}$ , $Q_{rr}$ )

To measure reverse recovery time,  $t_{rr}$  and reverse recovery charge,  $Q_{rr}$ , at first, short Gate pin and Source pin of DUT MOSFET. Moreover, a gate drive circuit, a given voltage source,  $V_{dd}$ , and an inductor are required to form a diode recovery test circuit. When MOSFET of gate drive circuit is turned on, L is charged; when it is turned off, energy of inductor will be discharged through intrinsic body diode of DUT MOSFET. When MOSFET of gate drive circuit is turned on again, the body diode of DUT will be reversed biased and reverse recovery starts to behave.  $t_{rr}$  and  $Q_{rr}$  are measured.

$t_{rr}$  and  $Q_{rr}$  are measured through above test circuit. Short Gate pin and Source pin of DUT MOSFET In applications, when  $I_{SD}$  reaches back to zero, the voltage spike happens on Drain-Source due to inductor energy released to  $C_{oss}$  of MOSFET. Higher  $Q_{rr}$  would cause severe voltage spike and vice versa.

## 7. Characteristics Curves

(T<sub>A</sub> = 25°C unless otherwise noted)

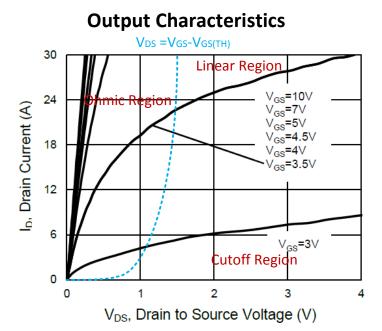

In output characteristics, three major regions are introduced, Ohmic region, Linear region, and Cut off region. The figure also shows curve defined by  $I_D$  vs  $V_{DS}$  at various gate to source voltage conditions. When MOSFET is turned on with  $V_{GS} < V_{GS(TH)}$ , it is operated in cut off region , when  $V_{DS}>V_{GS}-V_{GS(TH)}$ , it is operated at linear region. Finally, when  $V_{DS} < V_{GS}-V_{GS(TH)}$ , it is operated in Ohmic region. The blue dash line is defined by  $V_{DS} = V_{GS} - V_{GS(TH)}$ .

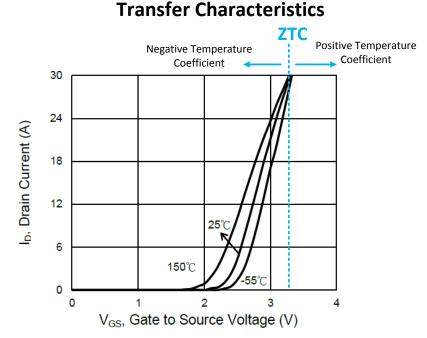

The transfer characteristics curve represents both  $V_{GS}$  and  $I_D$  relationship. From above, there is a ZTC point (Zero Temperature Coefficient). If  $V_{GS}$  is under ZTC point,  $V_{GS}$  becomes a negative temperature coefficient and vice versa.

Gate charge include 3 specified values, Qgs, Qgd ,and Qg. Qgs denotes Gate to Source charge. Qgd denotes Gate to Drain charge, which is also called the miller effect charge. Qg denotes the total gate charge.

Operations of Gate Charge are presented as below from above diagram.

1. T0~T1

When  $V_{GS}$  rises and reaches to  $V_{GS(TH)}$ ,  $C_{GS}$  is the capacitor to be charged. At the time, both  $I_D$  and  $V_{DS}$  present unchanged.

2. T1~T2

At this time interval, MOSFET is working in linear region.  $V_{GS}$  continues stepping up to the plateau voltage,  $V_P$ .  $C_{GS}$  is completely charged and  $I_D$  is raised up to full load current.

3. T2 ~ T3

At this time interval, MOSFET is still working in linear region. And,  $V_{DS}$  voltage starts to decrease and finally drops to zero. So the  $C_{GD}$  \* ( $dV_{DS}/dt$ ) becomes big and thus, creates current flowing through  $C_{GD}$ , which blocks  $V_{GS}$  keeps rising and maintains constant. During this time,  $R_{DS(on)}$ changes from high impedance to low impedance, entering Ohmic region.

4. T3 ~ T4

In this timing, V<sub>GS</sub> is raised up to rated value and MOSFET is operated in Ohmic region.

## **On-Resistance vs. Junction Temperature**

From the curve of  $R_{DS(on)}$  vs.  $T_J$ , it's seen the normalized  $R_{DS(on)}$  is 1 at  $T_J=25$ °C, and 1.85 at  $T_J=150$ °C. This indicates if the RDS(on) is 12mohm at  $T_J=25$ °C, it is expected to be 22.2 mohm at  $T_J=150$ °C.

$\therefore R_{DS(on)} = 12 \text{mohm}$   $\therefore \underline{R}_{DS(on) - 150C} = (R_{DS(0n) - 25C} \times K) = 12 \text{mohm} * 1.85 => 22.2 \text{ mohm}$

## Source-Drain Diode Forward Current vs. Voltage

From above curve, it is easily seen V<sub>SD</sub> has negative temperature coefficient. So, it is expected to obtain lower V<sub>SD</sub> voltage at higher temperature. From curve remarked, V<sub>SD</sub> is 0.5V at T<sub>J</sub>=150°C; V<sub>SD</sub> is 0.72V at T<sub>J</sub>=25°C; V<sub>SD</sub> is 0.85V at T<sub>J</sub>=-55°C.

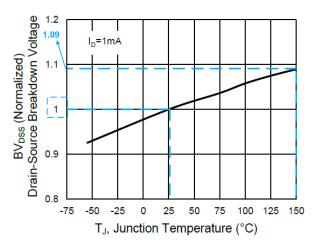

#### **BV**<sub>DSS</sub> vs. Junction Temperature

Above curve is BV<sub>DSS</sub> vs. T<sub>J</sub>. BV<sub>DSS</sub> is positive temperature coefficient. Based on above curve, It is seen the normalized BV<sub>DSS</sub> is 1 at T<sub>J</sub>=25°C, and 1.09 at T<sub>J</sub>=150°C. That is, if the BV<sub>DSS</sub> is 30V at T<sub>J</sub>=25°C, it is expected BV<sub>DSS</sub> is 32.7V at T<sub>J</sub>=150°C.

$$\underline{K} = (K_{-150^{\circ}C} / K_{-25^{\circ}C}) = 1.09 / 1 \Rightarrow 1.09$$

$$\therefore BV_{DSS} = 30V \qquad \therefore \underline{BV}_{DSS-150^{\circ}C} = (BV_{DSS-25^{\circ}C} \times K) = 30V * 1.09 \Rightarrow 32.7V$$

### Capacitance vs. Drain-Source Voltage

MOSFET have three types capacitances, Ciss, Coss and Crss. Regarding to the relationship of these capacitances, V<sub>DS</sub> voltage and frequency, it is introduced from above curve with a fixed frequency to observe to variations of  $C_{iss}$ ,  $C_{oss}$ , and  $C_{rss}$ . These three capacitances will affect the switching loss of power system. Below shows defined three types capacitances.

**MOSFET Equivalent Circuit**

SOA is defined the maximum value of  $V_{DS}$ ,  $I_D$  and time envelope of operation which guarantees safe operation when MOSFET works is actively biased. Four lines are used to determine the maximum operating limits.

#### Line 1

$R_{DS(on)}$  limits. For example, take TSC 30V MOSFET as example, whose maximum  $R_{DS(on)}$  is 11.7 mohm. According to the ohm's law, when  $V_{DS}$  is 1.0V and  $R_{DS(on)}$  is 11.7 mohm.  $I_D = 1.0V / 11.7$ mohm = 85.47A.

Line 2

The  $I_{DM}$  is defined by Pulsed Drain Current of datasheet. It is based on the  $I_D@T_C 25^{\circ}C$  value and generally speaking,  $I_{DM} = 4 \times I_D(@T_C 25^{\circ}C)$

$$I_{D} = \sqrt{\frac{T_{J} - T_{C}}{R_{\theta IC} \times K \times R_{ds(on)}}} \quad @25^{\circ}C$$

Line 3

This line is limited by the breakdown voltage.

Line 4

This line is limited by the a lot of parameters, including T<sub>J</sub>, T<sub>C</sub>, P<sub>D</sub>, R<sub> $\theta$ JC</sub>, Z<sub> $\theta$ JC</sub>, and K factor (R<sub>DS(on)</sub> vs. T<sub>J</sub>). The normalized effective transient thermal impedance (Z<sub> $\theta$ JC</sub>) depends on different square wave pulse duration(t) then got the both P<sub>D</sub> and I<sub>D</sub> from below equation. For example, take TSC 30V MOSFET as example:

$$V_{DS}$$

= 30V,  $R_{\theta JC}$  is 3.8°C/W,  $Z_{\theta JC}$  is 0.31@1mS

Taiwan Semiconductor

$$P_D = \frac{T_J - T_C}{R_{\theta JC} \times Z_{\theta JC}} \qquad I_D = \frac{P_D}{V_{DS}}$$

$P_{D} = (150^{\circ}\text{C} - 25^{\circ}\text{C})/(3.8^{\circ}\text{C/W x 0.31}) = 106.11\text{W} \qquad I_{D} = 106.11\text{W}/30\text{V} = 3.54\text{A}$ So, @1ms pulse and 30V condition, suggested operating current will not be exceeding 3.54A.

> K is 1.85 @ 150°C - ( Please refer to spec) R<sub>DS(on)</sub> is 11.7mohm

$$I_{D} = \sqrt{\frac{T_{J} - T_{C}}{R_{\theta JC} \times K \times R_{ds(on)} \times Z_{\theta JC}}} \qquad V_{DS} = \frac{P_{D}}{I_{D}}$$

$$I_D = \sqrt{\frac{150^{\circ}C - 25^{\circ}C}{3.8^{\circ}C/W \times 0.31 \times 1.85 \times 11.7 mohm}} = 70.02A @ 1ms$$

$V_{DS}$  = 106.11W / 70.02A = 1.515V ( Corner voltage @1ms condition )

Normalized Thermal Transient Impedance, Junction-to-Case Normalized Thermal Transient Impedance, Junction-to-Case

Above picture provides the normalized effective transient thermal impedance. These curves can be Junction to Ambient or Case based. From above, TSC 30V MOSFET is based on junction to case condition. As the duty cycle and the pulse duration increase, the transient thermal impedance gets close to 1. In the other words, It approaches to steady state thermal resistance.

$$T_J = T_C + P_{DM} \times Z_{\theta JC} \times R_{\theta JC}$$

For example, the TSM120NA03CR run in single pulse condition, the  $Z_{\theta JC}$  based on curve is 0.31 at 1ms. The  $R_{\theta JC}$  is 3.8°C/W and  $P_{DM}$  is 1.5W. So the junction temperature of TSM120NA03CR at  $T_C$ =100°C can be got as below list.

T<sub>J</sub> = 100°C + 1.5W x 0.31 x 3.8°C/W = 101.767°C

## References

- 1. TSM120NA03CR ------ 30V Power MOSFET Datasheet

- 2. Power FETs and their applications ----- Edwin S. Oxner

- 3. POWER MOSFETS Theory and Applications ----- Duncan A. Grant / John Gowar

## Authors

- HL Lin : Product Application Manager : hl\_lin@mail.ts.com.tw

- Childs Chung : Product Marketing Manager : Childs@mail.ts.com.tw

Jerry Chen : Vice President of Technical Marketing : Jerry\_chen@mail.ts.com.tw

## Taiwan Semiconductor Co., Ltd.

## Headquarters

Address: 11F. No. 25 Sec. 3, Beishin Rd, Shindian District, New Taipei City, Taiwan R.O.C. Telephone: +886-2-8913-1588 E-mail: <u>marketing@mail.ts.com.tw</u> Website: <u>www.taiwansemi.com</u>