# NCR 5380 SCSI

# **Interface Chip**

# **Design Manual**

Copyright © 1985, by NCR Corporation Dayton, Ohio All Rights Reserved Printed in U.S.A.

This document contains the latest information available at the time of publication. However, NCR reserves the right to modify the contents of this material at any time. Also, all features, functions and operations described herein may not be marketed by NCR in all parts of the world. Therefore, before using this document, consult your NCR representative or NCR office for the information that is applicable and current.

# TABLE OF CONTENTS

| SECTION |          |                                  | PAG | λE |  |  |

|---------|----------|----------------------------------|-----|----|--|--|

| 1.      | Genera   | I Description                    | (   | 3  |  |  |

| 2.      | SCSI B   | ackground                        | 4   | 4  |  |  |

| 3.      |          | ck Diagram                       |     |    |  |  |

| 4.      | Pin Des  | scription                        |     |    |  |  |

|         | 4.1      | Microprocessor Interface Signals | (   | 6  |  |  |

|         | 4.2      | SCSI Interface Signals           |     |    |  |  |

| 5.      | Electric | al Characteristics               |     |    |  |  |

| 6.      | Internal | Registers                        |     |    |  |  |

|         | 6.0      | General                          |     |    |  |  |

|         | 6.1      | Data Registers                   | '   | 10 |  |  |

|         | 6.1.1    | Current SCSI Data Register       | '   | 10 |  |  |

|         | 6.1.2    | Output Data Register             | '   | 10 |  |  |

|         | 6.1.3    | Input Data Register              |     |    |  |  |

|         | 6.2      | Initiator Command Register       | '   | 11 |  |  |

|         | 6.3      | Mode Register                    | '   | 13 |  |  |

|         | 6.4      | Target Command Register          | '   | 14 |  |  |

|         | 6.5      | Current SCSI Bus Status Register | '   | 15 |  |  |

|         | 6.6      | Select Enable Register           |     | 15 |  |  |

|         | 6.7      | Bus and Status Register          | '   | 15 |  |  |

|         | 6.8      | DMA Registers                    | '   | 16 |  |  |

|         | 6.8.1    | Start DMA Send                   | '   | 16 |  |  |

|         | 6.8.2    | Start DMA Target Receive         |     | 17 |  |  |

|         | 6.8.3    | Start DMA Initiator Receive      | '   | 17 |  |  |

|         | 6.9      | Reset Parity/Interrupt           | '   | 17 |  |  |

| 7.      | On-Chi   | p SCSI Hardware Support          | '   | 18 |  |  |

| 8.      | Interrup | bts                              |     |    |  |  |

|         | 8.1      | Selection/Reselection            |     | 19 |  |  |

|         | 8.2      | End of Process (EOP) Interrupt   | :   | 20 |  |  |

|         | 8.3      | SCSI Bus Reset                   | :   | 21 |  |  |

|         | 8.4      | Parity Error                     | :   | 21 |  |  |

|         | 8.5      | Bus Phase Mismatch               |     | 22 |  |  |

|         | 8.6      | Loss of BSY                      | :   | 22 |  |  |

| 9.  | Reset C | Conditions                                  |

|-----|---------|---------------------------------------------|

|     | 9.1     | Hardware Chip Reset                         |

|     | 9.2     | SCSI Bus Reset Received                     |

|     | 9.3     | SCSI Bus Reset Issued                       |

| 10. | Data Tr | ansfers                                     |

|     | 10.1    | Programmed I/O Transfers                    |

|     | 10.2    | Normal DMA Mode                             |

|     | 10.3    | Block Mode DMA                              |

|     | 10.4    | Pseudo DMA Mode                             |

|     | 10.5    | Halting a DMA Operation                     |

|     | 10.5.1  | Using the EOP Signal                        |

|     | 10.5.2  |                                             |

|     | 10.5.3  | Resetting the DMA MODE Bit                  |

| 11. | Externa | I Timing Diagrams                           |

|     | 11.1    | CPU Write                                   |

|     | 11.2    | CPU Read                                    |

|     | 11.3    | DMA Write (Non-block Mode) Target Send      |

|     | 11.4    | DMA Write (Non-block Mode) Initiator Send   |

|     | 11.5    | DMA Read (Non-block Mode) Target Receive    |

|     | 11.6    | DMA Read (Non-block Mode) Initiator Receive |

|     | 11.7    | DMA Write (Block Mode) Target Send          |

|     | 11.8    | DMA Read (Block Mode) Target Receive        |

|     | 11.9    | Reset                                       |

|     | 11.10   | Arbitration                                 |

# **APPENDICES**

| A1. | NCR 5380 vs. NCR 5385/86          | . 34 |

|-----|-----------------------------------|------|

|     | Flowcharts/Software               | . 35 |

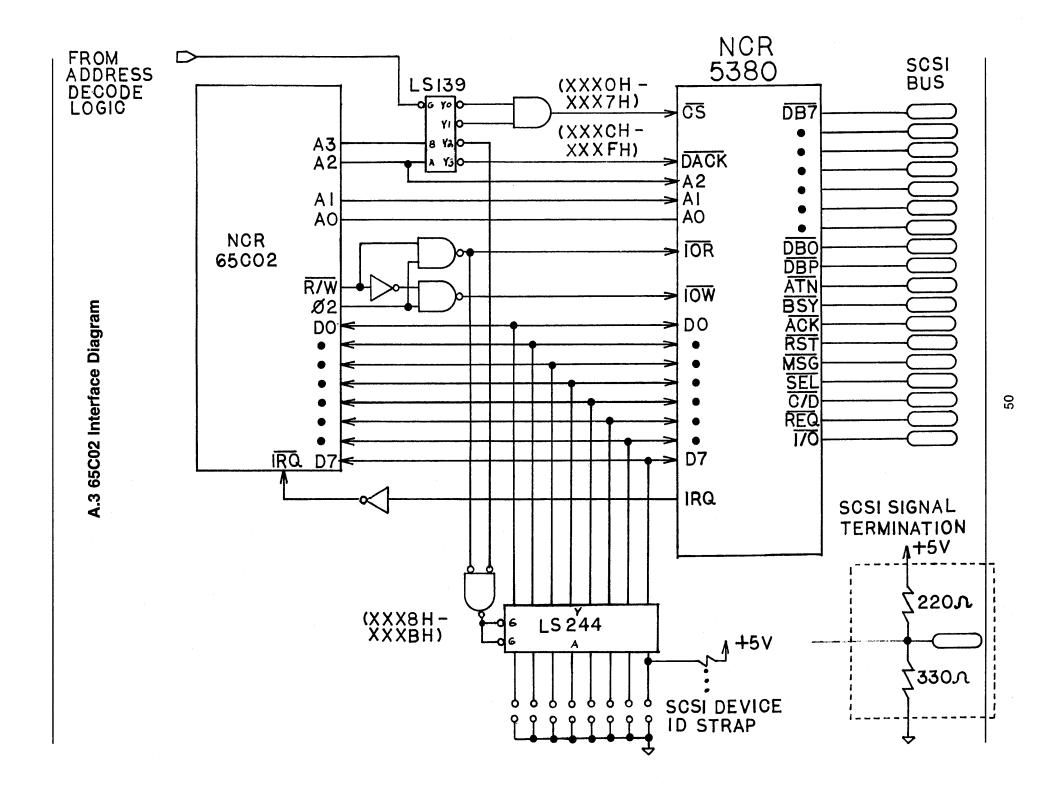

| A3. | 65C02 Interface Diagram           | . 50 |

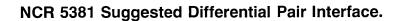

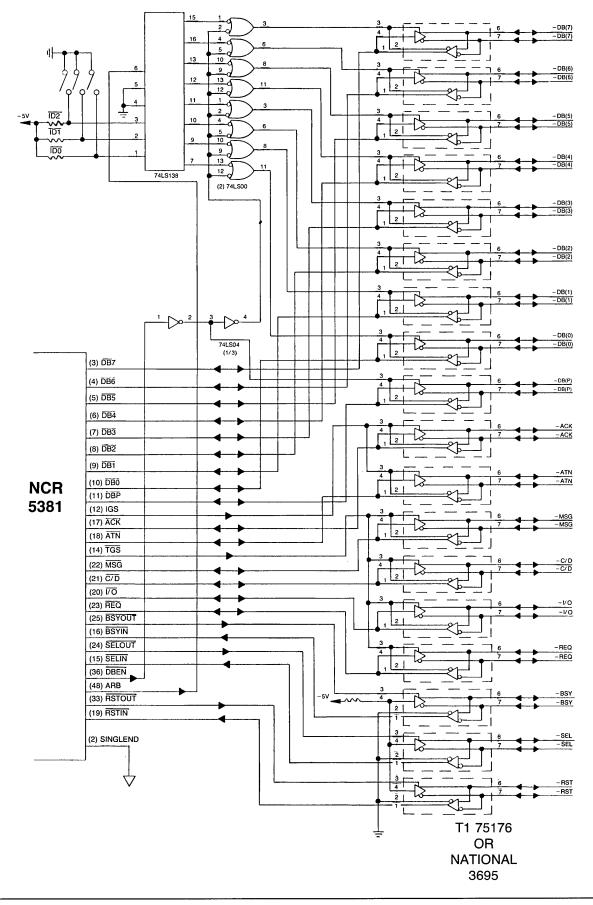

| A4. | NCR 5381 Differential Pair Option | . 51 |

| A5. | SCSI/Plus                         | . 54 |

| A6. | Register Reference Chart          | . 56 |

# SECTION 1 GENERAL DESCRIPTION

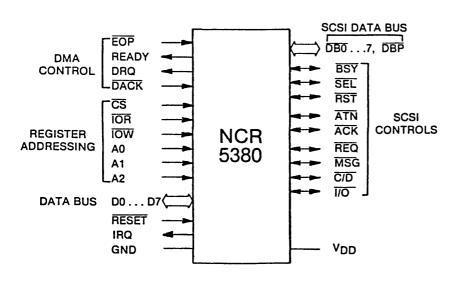

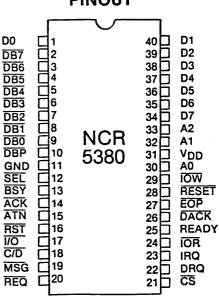

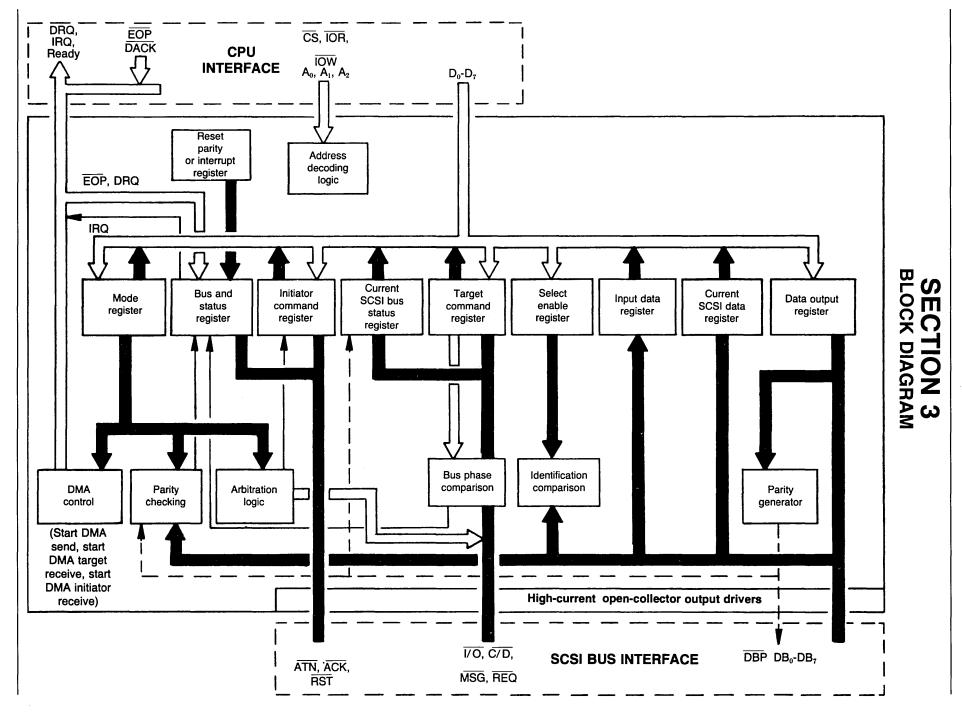

The NCR 5380 SCSI interface device is a 40 pin NMOS device designed to accommodate the Small Computer Systems Interface (SCSI) as defined by the ANSI X3T9.2 committee. The NCR 5380 operates in both the initiator and target roles and can therefore be used in host adapter, host port and formatter designs. This device supports arbitration, including reselection. Special high-current open collector output drivers, capable of sinking 48mA at 0.5V, allow for direct connection to the SCSI bus. Differential pair operation is supported using a 48 pin version of this part, designated the NCR 5381 (refer to Appendix A4).

The NCR 5380 communicates with the system microprocessor as a peripheral device. The chip is controlled by reading and writing several internal registers which may be addressed as standard or memory mapped I/O. Minimal processor intervention is required for DMA transfers because the 5380 controls the necessary handshake signals. The NCR 5380 interrupts the MPU when it detects a bus condition that requires attention. Normal and block mode DMA is provided to match many popular DMA controllers.

#### SCSI INTERFACE

- \* Asynchronous, interface to 1.5 MBPS

- \* Supports initiator and target roles

- \* Parity generation w/optional checking

- \* Supports arbitration

- \* Direct control of all bus signals

- \* High current outputs drive SCSI bus directly

#### **MPU INTERFACE**

- \* Memory or I/O mapped interface

- \* DMA or programmed I/O

- \* Normal or block mode DMA

- \* Optional MPU interrupts

**FUNCTIONAL PIN GROUPING**

#### PINOUT

# SECTION 2 SCSI BACKGROUND

SCSI (Small Computer Systems Interface) has evolved from the SASI (Shugart Associates Systems Interface) disk controller interface standard developed by Shugart Associates in the late 1970's. NCR and Shugart jointly approached the ANSC X3T9.3 subcommittee in December of 1981 and proposed that a committee be formed to develop an intelligent interface standard based on SASI. The ANSC X3T9.3 subcommittee divided into two groups so that SASI could be pursued. In February of 1982, NCR and Shugart Associates presented SASI as a working document. It was agreed that a separate group should develop the standard and the ANSC X3T9.2 subcommittee was established. This group met in April of that year and formally changed the name to the Small Computer Systems Interface (SCSI).

The proposed standard has since been forwarded from the subcommittee and is becoming a major industry standard. It is expected that other standards organizations such as ECMA (European Computer Manufactures Association) and ISO (International Standards Organization) will adopt the proposed standard as well.

NCR Microelectronics announced the NCR 5385, the first SCSI protocol controller, in April of 1983. This product family includes the NCR 5386 and the soon-to-be-announced NCR 5386S. The NCR 5380 and 5381 were designed to compliment this initial offering. Differences between the product families are described in Appendix A1.

This design manual is not an SCSI specification and assumes some prior knowledge of the SCSI proposed standard. Copies of the proposed standard may be obtained, with pre-payment of \$20, from:

X3 Secretariat, Computer and Business Equipment Manufacturers Association 311 First Street, NW, Suite 500 Washington, D.C. 20001

Please include a self-addressed mailing label.

Other documents which may be useful are:

- NCR 5385 SCSI Protocol Controller Data Sheet (MC-704)

- NCR 5385 SCSI Protocol Controller User's Guide (MC-903)

- SCSI Engineering Notebook

These documents may be obtained by contacting your local NCR Microelectronics sales representative or by writing/ calling:

NCR Microelectronics Logic Products Marketing 1635 Aeroplaza Drive Colorado Springs, CO 80916 PH# 1-800-525-2252

σı

# SECTION 4 PIN DESCRIPTION

# 4.1 Microprocessor Interface Signals

| Pin Name   | Pin #      | Description                                                                                                                                                                                                    |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0, A1, A2 | 30, 32, 33 | INPUTS These signals are used with $\overline{\text{CS}}$ , $\overline{\text{IOR}}$ or $\overline{\text{IOW}}$ to address all internal registers.                                                              |

| CS         | 21         | INPUT Chip Select enables a read or write of the internal register selected by A0, A1 and A2. $\overline{CS}$ is an active low signal.                                                                         |

| DACK       | 26         | INPUT<br>DMA Acknowledge resets DRQ and selects the data<br>register for input or output data transfers. DACK is an<br>active low signal.                                                                      |

| DRQ        | 22         | OUTPUT<br>DMA Request indicates that the data register is ready<br>to be read or written. DRQ occurs only if DMA mode is<br>true in the Command Register. It is cleared by DACK.                               |

| D0 D7      | 1,40 34    | BI-DIRECTIONAL, TRI-STATE<br>Microprocessor data bus active high                                                                                                                                               |

| EOP        | 27         | INPUT<br>The End of Process signal is used to terminate a<br>DMA transfer. If asserted during a DMA cycle, the<br>current byte will be transferred but no additional bytes<br>will be requested.               |

| ĪOR        | 24         | INPUT I/ O Read is used to read an internal register selected by $\overline{CS}$ and A0, A1 and A2. It also selects the Input Data Register when used with $\overline{DACK}$ . $\overline{IOR}$ is active low. |

| Pin Name      | Pin # | Description                                                                                                                                                                                                                                                                 |

|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĪOW           | 29    | INPUT I/ O Write is used to write an internal register selected by $\overline{CS}$ and A0, A1 and A2. It also selects the Output Data Register when used with $\overline{DACK}$ . $\overline{IOW}$ is active low.                                                           |

| IRQ           | 23    | OUTPUT<br>Interrupt Request alerts a microprocessor of an error<br>condition or an event completion.                                                                                                                                                                        |

| READY         | 25    | OUTPUT<br>Ready can be used to control the speed of block<br>mode DMA transfers. This signal goes active to indi-<br>cate the chip is ready to send/receive data and re-<br>mains false after a transfer until the last byte is sent or<br>until the DMA Mode bit is reset. |

| RESET         | 28    | INPUT<br>Reset clears all registers. It does not force the SCSI<br>signal RST to the active state. RESET is an active low<br>signal.                                                                                                                                        |

| Power Signals |       |                                                                                                                                                                                                                                                                             |

| Pin Name      | Pin # | Description                                                                                                                                                                                                                                                                 |

| Pin Name | Pin # | Description |  |

|----------|-------|-------------|--|

| VDD      | 31    | +5 VOLTS    |  |

| GND      | 11    | GROUND      |  |

# 4.2 SCSI Interface Signals

The following signals are all bi-directional, active low, open collector signals. With 48 mA sink capability, all pins interface directly with the SCSI bus.

| Pin Name   | Pin #    | Description                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK        | 14       | Driven by an initiator, $\overline{ACK}$ indicates an acknow-<br>ledgment for a REQ/ACK data transfer handshake.<br>In the target role, $\overline{ACK}$ is received as a response to<br>the $\overline{REQ}$ signal.                                                                                                                          |

| ATN        | 15       | Driven by an initiator, $\overline{\text{ATN}}$ indicates an attention condition. This signal is received in the target role.                                                                                                                                                                                                                  |

| BSY        | 13       | This signal indicates that the SCSI bus is being used<br>and can be driven by both the initiator and the target<br>device.                                                                                                                                                                                                                     |

| C/D        | 18       | A signal driven by the target, $\overline{C/D}$ indicates Control or Data information is on the data bus. This signal is received by the initiator.                                                                                                                                                                                            |

| 1/0        | 17       | $\overline{I/O}$ is a signal driven by a target which controls the direction of data movement on the SCSI bus. True indicates input to the initiator. This signal is also used to distinguish between Selection and Reselection phases.                                                                                                        |

| MSG        | 19       | $\overline{\text{MSG}}$ is a signal driven by the target during the Message phase. This signal is received by the initiator.                                                                                                                                                                                                                   |

| REQ        | 20       | Driven by a target, $\overrightarrow{\text{REQ}}$ indicates a request for a REQ/ACK data transfer handshake. This signal is received by the initiator.                                                                                                                                                                                         |

| RST        | 16       | The $\overrightarrow{RST}$ signal indicates an SCSI bus RESET condition.                                                                                                                                                                                                                                                                       |

| DB0<br>DBP | 92<br>10 | These eight data bits ( $\overline{DB0}$ - $\overline{DB7}$ ) plus a parity bit ( $\overline{DBP}$ ) form the data bus. $\overline{DB7}$ is the most significant bit and has the highest priority during the Arbitration phase. Data parity is odd. Parity is always generated and optionally checked. Parity is not valid during arbitration. |

| SEL        | 12       | $\overline{\text{SEL}}$ is used by an initiator to select a target or by a target to reselect an initiator.                                                                                                                                                                                                                                    |

# SECTION 5 ELECTRICAL CHARACTERISTICS OPERATING CONDITIONS

| PARAMETER                                               | SYMBOL                                   | MIN       | MAX               | UNITS              |

|---------------------------------------------------------|------------------------------------------|-----------|-------------------|--------------------|

| Supply Voltage<br>Supply Current<br>Ambient Temperature | V <sub>DD</sub><br>I <sub>DD</sub><br>TA | 4.75<br>0 | 5.25<br>145<br>70 | Volts<br>mA.<br>°C |

# **INPUT SIGNAL REQUIREMENTS**

| PARAMETER                                                                                                   | CONDITIONS | MIN         | MAX         | UNITS                      |

|-------------------------------------------------------------------------------------------------------------|------------|-------------|-------------|----------------------------|

| High-level, Input VIH<br>Low-level, Input VIL                                                               |            | 2.0<br>-0.3 | 5.25<br>0.8 | Volts<br>Volts             |

| SCSI BUS pins 2 20<br>High-level Input Current, I <sub>IH</sub><br>Low-level Input Current, I <sub>IL</sub> |            |             | 50<br>-50   | <i>ц</i> а.<br><i>ц</i> а. |

| All other pins<br>High-level Input Current, IIH<br>Low-level Input Current, IIL                             |            |             | 10<br>-10   | да.<br>да.                 |

# **OUTPUT SIGNAL REQUIREMENTS**

| PARAMETER                                                       | CONDITIONS                                                                                                     | MIN | MAX | UNITS          |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|----------------|

| SCSI BUS pins 2 20<br>Low-level Output VOL                      | V <sub>DD</sub> = 4.75 V<br>I <sub>OL</sub> = 48.0mA.                                                          |     | 0.5 | Volts          |

| All other pins<br>High-level Output VOH<br>Low-level Output VOL | V <sub>DD</sub> = 4.75 V<br>I <sub>OH</sub> = -3.0mA.<br>V <sub>DD</sub> = 4.75 V<br>I <sub>OL</sub> = 7.0 mA. | 2.4 | 0.5 | Volts<br>Volts |

#### PRELIMINARY

Notice: This is not a final specification. Some parametric limits are subject to change.

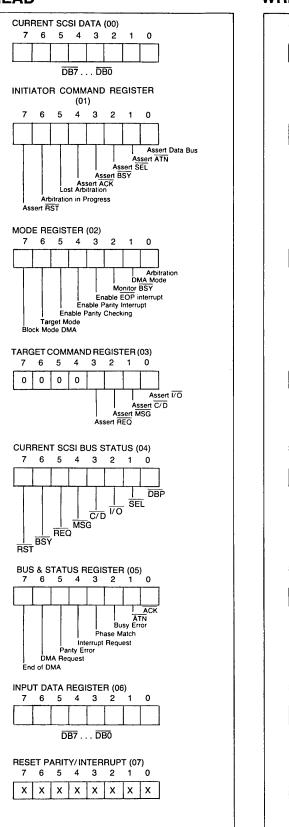

# SECTION 6 INTERNAL REGISTERS

#### 6.0 General

The NCR 5380 SCSI Interface Device appears as a set of eight registers to the controlling CPU. By reading and writing the appropriate registers, the CPU may initiate any SCSI bus activity or may sample and assert any signal on the SCSI bus. This allows the user to implement all or portions of the SCSI protocol in software. These registers are read (written) by activating  $\overline{CS}$  with an address on A2-A0 and then issuing an  $\overline{IOR}$  ( $\overline{IOW}$ ) pulse. This section describes the operation of the internal registers.

#### Address

| A2 | A1 | <b>A</b> 0 | R/W | Register Name               |

|----|----|------------|-----|-----------------------------|

| 0  | 0  | 0          | R   | Current SCSI Data           |

| 0  | 0  | 0          | W   | Output Data                 |

| 0  | 0  | 1          | R/W | Initiator Command           |

| 0  | 1  | 0          | R/W | Mode                        |

| 0  | 1  | 1          | R/W | Target Command              |

| 1  | 0  | 0          | R   | Current SCSI Bus Status     |

| 1  | 0  | 0          | W   | Select Enable               |

| 1  | 0  | 1          | R   | Bus and Status              |

| 1  | 0  | 1          | W   | Start DMA Send              |

| 1  | 1  | 0          | R   | Input Data                  |

| 1  | 1  | 0          | W   | Start DMA Target Receive    |

| 1  | 1  | 1          | R   | Reset Parity/Interrupts     |

| 1  | 1  | 1          | W   | Start DMA Initiator Receive |

**Register Summary**

#### 6.1 Data Registers

The data registers are used to transfer SCSI commands, data, status, and message bytes between the microprocessor data bus and the SCSI bus. The NCR 5380 does not interpret any information that passes through the data registers. The data registers consist of the transparent Current SCSI Data Register, the Output Data Register, and the Input Data Register.

# 6.1.1 Current SCSI Data Register— Address 0 (Read-only)

The Current SCSI Data Register is a read-only register which allows the microprocessor to read the active SCSI data bus. This is accomplished by activating  $\overline{CS}$ with an address on A2-A0 of 000 and issuing an  $\overline{IOR}$ pulse. If parity checking is enabled, the SCSI bus parity is checked at the beginning of the read cycle. This register is used during a programmed I/O data read or during arbitration to check for higher priority arbitrating devices. Parity is not guaranteed valid during arbitration.

### 6.1.2 Output Data Register— Address 0 (write-only)

The Output Data Register is a write-only register that is used to send data to the SCSI bus. This is accomplished by either using a normal MPU write, or under DMA control, by using IOW and DACK. This register is also used to assert the proper ID bits or the SCSI bus during the arbitration and selection phases.

#### **Output Data Register**

#### 6.1.3 Input Data Register— Address 6 (Read-only)

The Input Data Register is a read-only register that is used to read latched data from the SCSI bus. Data is latched either during a DMA Target receive operation when ACK (pin 14) goes active or during a DMA Initiator receive when REQ (pin 20) goes active. The DMA Mode bit (port 2, bit 1) must be set before data can be latched in the Input Data Register. This register may be read under DMA control using IOR and DACK. Parity is optionally checked when the Input Data Register is loaded.

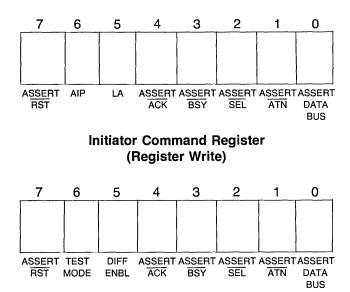

## 6.2 Initiator Command Register— Address 1 (Read/Write)

The Initiator Command Register is a read/write register which is used to assert certain SCSI bus signals, to monitor those signals, and to monitor the progress of bus arbitration. Many of these bits are significant only when being used as an Initiator; however, most can be used during Target role operation.

#### Initiator Command Register (Register Read)

The following describes the operation of all bits in the Initiator Command Register.

# BIT 7—ASSERT RST

Whenever a one (1) is written to bit 7 of the Initiator Command Register, the RST signal (pin 16) is asserted on the SCSI bus. The RST signal will remain asserted until this bit is reset or until an external RESET (pin 28) occurs. After this bit is set (1), IRQ (pin 23) goes active and all internal logic and control registers are reset (except for the interrupt latch and the ASSERT RST bit). Writing a zero (0) to bit 7 of the Initiator Command Register de-asserts the RST signal. Reading this register simply reflects the status of this bit.

# BIT 6—AIP (Arbitration in Progress—read bit)

This bit is used to determine if arbitration is in progress. For this bit to be active, the ARBITRATE bit (port 2, bit 0) must have been set previously. It indicates that a bus free condition has been detected and that the chip has asserted  $\overrightarrow{BSY}$  (pin 13) and the contents of the Output Data Register (port 0) onto the SCSI bus. AIP will remain active until the ARBITRATE bit is reset.

## BIT 6—TEST MODE (write bit)

This bit may be written during a test environment to disable all output drivers, effectively removing the NCR 5380 from the circuit. Resetting this bit returns the part to normal operation.

# BIT 5—LA (Lost Arbitration—read bit)

This bit, when active, indicates that the NCR 5380 detected a bus free condition, arbitrated for use of the bus by asserting  $\overrightarrow{\text{BSY}}$  (pin 13) and its ID on the data bus and lost arbitration due to  $\overrightarrow{\text{SEL}}$  (pin 12) being asserted by another bus device. For this bit to be active the ARBITRATE bit (port 2, bit 0) must be active.

## BIT 5—DIFF ENBL (Differential Enable—write bit)

This bit is not used in the NCR 5380 and is only meaningful in the NCR 5381, a 48 pin device which supports external differential pair transceivers. DIFF ENBL should only be asserted if the device is physically connected as either an Initiator or as a Target. If enabled, the signal TGS (pin 14—NCR 5381) is asserted if the TARGETMODE bit (port 2, bit 6) is set (1) or the signal IGS (pin 12—NCR 5381) is asserted if the TARGETMODE bit is reset (0).

# BIT 4-ASSERT ACK

This bit is used by the bus initiator to assert  $\overrightarrow{ACK}$  (pin 14) on the SCSI bus. In order to assert  $\overrightarrow{ACK}$  the TARGETMODE bit (port 2, bit 6) must be false. Writing a zero to this bit resets  $\overrightarrow{ACK}$  on the SCSI bus. Reading this register simply reflects the status of this bit.

# BIT 3-ASSERT BSY

Writing a one (1) into this bit position asserts  $\overline{BSY}$  (pin 13) onto the SCSI bus. Conversely, a zero (0) resets the  $\overline{BSY}$  signal. Asserting  $\overline{BSY}$  indicates a successful selection or reselection and resetting this bit creates a bus disconnect condition. Reading this register simply reflects the status of this bit.

# BIT 2-ASSERT SEL

Writing a one (1) into this bit position asserts SEL (pin 12) onto the SCSI bus. SEL is normally asserted after arbitration has been successfully completed. SEL may be de-asserted by resetting this bit to a zero. A read of this register simply reflects the status of this bit.

# BIT 1—ASSERT ATN

ATN (pin 15) may be asserted on the SCSI bus by setting this bit to a one (1) if the TARGETMODE bit (port 2, bit 6) is false. ATN is normally asserted by the initiator to request a Message Out bus phase. Note that since ASSERT SEL and ASSERT ATN are in the same register, a select with ATN may be implemented with one MPU write. ATN may be de-asserted by resetting this bit to a zero (0). A read of this register simply reflects the status of this bit.

## BIT 0-ASSERT DATA BUS

The ASSERT DATA BUS bit, when set, allows the contents of the Output Data Register to be enabled as chip outputs on the signals DB0-DB7. Parity is also generated and asserted on DBP. In the NCR 5381, this bit asserts the DBEN signal (pin 36). Resetting this bit disables the output data bus or the DBEN signal.

When connected as an Initiator, the outputs are only enabled if the TARGETMODE bit (port 2, bit 6) is false, the received signal  $\overline{I/O}$  (pin 17) is false, and the phase signals (C/D, I/O, and MSG) match the contents of the ASSERT  $\overline{C/D}$ , ASSERT  $\overline{I/O}$ , and ASSERT  $\overline{MSG}$  in the Target Command Register.

This bit should also be set during DMA send operations.

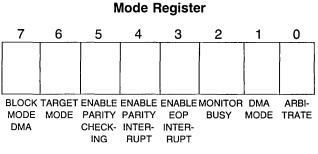

# 6.3 Mode Register—Address 2 (Read/Write)

The Mode Register is used to control the operation of the chip. This register determines whether the NCR 5380 operates as an initiator or a target, whether DMA transfers are being used, whether parity is checked, and whether interrupts are generated on various external conditions. This register may be read to check the value of these internal control bits. The following describes the operation of these control bits.

#### BIT 7—BLOCK MODE DMA

The BLOCK MODE DMA bit controls the characteristics of the DMA DRQ-DACK handshake. When this bit is reset (0) and the DMA MODE bit is active (1), the DMA handshake uses the normal interlocked handshake and the rising edge of DACK (pin 26) indicates the end of each byte being transferred. In block mode operation, BLOCK MODE DMA bit set (1) and DMA MODE bit set (1), the end of IOR (pin 24) or IOW (pin 29) signifies the end of each byte transferred and DACK is allowed to remain active throughout the DMA operation. READY (pin 25) can then be used to request the next transfer.

#### BIT 6—TARGETMODE

The TARGETMODE bit allows the NCR 5380 to operate as either an SCSI bus initiator, bit reset (0), or as an SCSI bus target device, bit set (1). In order for the signals  $\overline{\text{ATN}}$  (pin 15) and  $\overline{\text{ACK}}$  (pin 14) to be asserted on the SCSI bus, the TARGETMODE bit must be reset (0). In order for the signals  $\overline{\text{C/D}}$ ,  $\overline{\text{I/O}}$ ,  $\overline{\text{MSG}}$  and  $\overline{\text{REQ}}$  to be asserted on the SCSI bus, the SCSI bus, the TARGETMODE bit must be reset (1).

#### **BIT 5—ENABLE PARITY CHECKING**

The ENABLE PARITY CHECKING bit determines whether parity errors will be ignored or saved in the parity error latch. If this bit is reset (0), parity will be ignored. Conversely, if this bit is set (1) parity errors will be saved.

#### **BIT 4—ENABLE PARITY INTERRUPT**

The ENABLE PARITY INTERRUPT bit, when set (1), will cause an interrupt (IRQ) to occur if a parity error is detected. A parity interrupt will only be generated if the ENABLE PARITY CHECKING bit (bit 5) is also enabled (1).

#### BIT 3-ENABLE EOP INTERRUPT

The ENABLE EOP INTERRUPT, when set (1), causes an interrupt to occur when an  $\overline{\text{EOP}}$  (End of Process) signal (pin 27) is received from the DMA controller logic.

#### **BIT 2-MONITOR BUSY**

The MONITOR BUSY bit, when true (1), causes an interrupt to be generated for an unexpected loss of  $\overline{\text{BSY}}$  (pin 13). When the interrupt is generated due to loss of  $\overline{\text{BSY}}$ , the lower 6 bits of the Initiator Command Register are reset (0) and all signals are removed from the SCSI bus.

#### BIT 1-DMA MODE

The DMA MODE bit is normally used to enable a DMA transfer and must be set (1) prior to writing ports 5 through 7. Ports 5 through 7 are used to start DMA transfers. The TARGETMODE bit (port 2, bit 6) must be consistent with writes to port 6 and 7 [i.e. set (1) for a write to port 6 and reset (0) for a write to port 7]. The control bit ASSERT DATA BUS (port 1, bit 0) must be true (1) for all DMA send operations. In the DMA mode, REQ (pin 20) and ACK (pin 14) are automatically controlled.

The DMA MODE bit is not reset upon the receipt of an  $\overline{EOP}$  signal. Any DMA transfer may be stopped by writing a zero into this bit location, however care must be taken not to cause  $\overline{CS}$  and  $\overline{DACK}$  to be active simultaneously.

#### **BIT 0—ARBITRATE**

The ARBITRATE bit is set (1) to start the arbitration process. Prior to setting this bit the Output Data Register should contain the proper SCSI device ID value. Only one data bit should be active for SCSI bus arbitration. The NCR 5380 will wait for a bus free condition before entering the arbitration phase. The results of the arbitration phase may be determined by reading the status bits LA and AIP (port 1, bits 5 & 6 respectively).

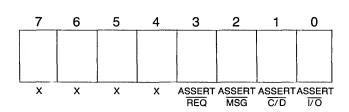

#### 6.4 Target Command Register— Address 3 (Read/Write)

When connected as a target device, the Target Command Register allows the MPU to control the SCSI bus information transfer phase and/or to assert  $\overline{\text{REQ}}$  (pin 20) simply by writing this register. The TARGETMODE bit (port 2, bit 6) must be true (1) for bus assertion to occur. The SCSI bus phases are described in the following table.

#### **SCSI Information Transfer Phases**

| Bus Phase   | ASSERT | ASSERT | ASSERT |

|-------------|--------|--------|--------|

| Data Out    | 0      | 0      | 0      |

| Unspecified | 0      | 0      | 1      |

| Command     | 0      | 1      | 0      |

| Message Out | 0      | 1      | 1      |

| Data In     | 1      | 0      | 0      |

| Unspecified | 1      | 0      | 1      |

| Status      | 1      | 1      | 0      |

| Message In  | 1      | 1      | 1      |

When connected as an Initiator with DMA Mode true, if the phase lines (I/O, C/D, and MSG) do not match the phase bits in the Target Command Register, a phase mismatch interrupt is generated when  $\overline{REQ}$  (pin 20) goes active. In order to send data as an Initiator, the ASSERT I/O, ASSERT C/D, and ASSERT MSG bits must match the corresponding bits in the Current SCSI Bus Status Register (port 4). The ASSERT  $\overline{REQ}$  bit (bit 3) has no meaning when operating as an Initiator.

#### **Target Command Register**

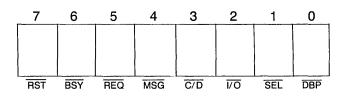

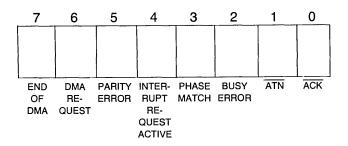

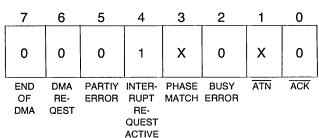

## 6.5 Current SCSI Bus Status Register—Address 4 (Read-only)

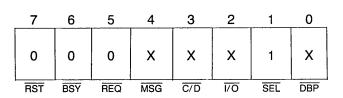

The Current SCSI Bus Status register is a read-only register which is used to monitor seven SCSI bus control signals plus the data bus parity bit. For example, an Initiator device can use this register to determine the current bus phase and to poll REQ for pending data transfers. This register may also be used to determine why a particular interrupt occurred. The following describes the Current SCSI Bus Status Register.

**Current SCSI Bus Status Register**

# 6.6 Select Enable Register—Address 4 (Write-only)

The Select Enable Register is a write-only register which is used as a mask to monitor a single ID during a selection attempt. The simultaneous occurrence of the correct ID bit,  $\overline{BSY}$  false, and  $\overline{SEL}$  true will cause an interrupt. This interrupt can be disabled by resetting all bits in this register. If the ENABLE PARITY CHECK-ING bit (port 2, bit 5) is active (1), parity will be checked during selection.

# 6.7 Bus and Status Register—Address 5 (Read-only)

The Bus and Status Register is a read-only register which can be used to monitor the remaining SCSI control signals not found in the Current SCSI Bus Status Register (ATN & ACK) as well as six other status bits. The following describes each bit of the Bus and Status Register individually.

#### BIT 7—END OF DMA TRANSFER

The END OF DMA TRANSFER bit is set if EOP (pin 27), DACK (pin 26), and either IOR (pin 24), or IOW (pin 29) are simultaneously active for at least 100 nsec. Since the EOP signal can occur during the last byte sent to the Output Data Register (port 0), the REQ and ACK signals should be monitored to insure that the last byte has been transferred. This bit is reset when the DMA MODE bit is reset (0) in the Mode Register (port 2).

#### BIT 6-DMA REQUEST

The DMA REQUEST bit allows the MPU to sample the output pin DRQ (pin 22). DRQ can be cleared by asserting DACK (pin 26) or by resetting the DMA MODE bit (bit 1) in the Mode Register (port 2). The DRQ signal does not reset when a phase mismatch interrupt occurs.

#### **BIT 5—PARITY ERROR**

This bit is set if a parity error occurs during a data receive or a device selection. The PARITY ERROR bit can only be set (1) if the ENABLE PARITY CHECK bit (port 2, bit 5) is active (1). This bit may be cleared by reading the Reset Parity/Interrupt Register (port 7).

#### BIT 4—INTERRUPT REQUEST ACTIVE

This bit is set if an enabled interrupt condition occurs. It reflects the current state of the IRQ (pin 23) output and can be cleared by reading the Reset Parity/Interrupt Register (port 7).

#### BIT 3—PHASE MATCH

The SCSI signals  $\overline{\text{MSG}}$ ,  $\overline{\text{C/D}}$ , and  $\overline{\text{I/O}}$  (pins 19, 18, and 17) represent the current information transfer phase. The PHASE MATCH bit indicates whether the current SCSI bus phase matches the lower 3 bits of the Target Command Register. PHASE MATCH is continuously updated and is only significant when operating as a bus initiator. A Phase Match is required for data transfers to occur on the SCSI bus.

#### BIT 2—BUSY ERROR

The BUSY ERROR bit is active if an unexpected loss of the BSY signal (pin 13) has occurred. This latch is set whenever the MONITOR BUSY bit (port 2, bit 2) is true and BSY is false. An unexpected loss of BSY will disable any SCSI outputs and will reset the DMA MODE bit (port 2, bit 1).

#### BIT 1—ATN

This bit reflects the condition of the SCSI bus control signal  $\overline{\text{ATN}}$  (pin 15). This signal is normally monitored by the target device.

#### BIT 0-ACK

This bit reflects the condition of the SCSI bus control signal ACK (pin 14). This signal is normally monitored by the target device.

### 6.8 DMA Registers

Three write-only registers are used to initiate all DMA activity. They are Start DMA Send (port 5), Start DMA Target Receive (port 6) and Start DMA Initiator Receive (port 7). Simply writing these registers starts the DMA transfers. Data presented to the NCR 5380 on signals D0-D7 during the register write is meaningless and has no effect on the operation. Prior to writing these registers the BLOCK MODE DMA bit (bit 7), the DMA MODE bit (bit 1) and the TARGETMODE bit (bit 6) in the Mode Register (port 2) must be appropriately set. The individual registers are briefly described below.

### 6.8.1 Start DMA Send—Address 5 (Write-only)

This register is written to initiate a DMA send, from the DMA to the SCSI bus, for either initiator or target role operations. The DMA MODE bit (port 2, bit 1) must be set prior to writing this register.

## 6.8.2 Start DMA Target Receive—Address 6 (Write-only)

This register is written to initiate a DMA receive, from the SCSI bus to the DMA, for target operation only. The DMA MODE bit (bit 1) and the TARGETMODE bit (bit 6) in the Mode Register (port 2) must both be set (1) prior to writing this register.

# 6.8.3 Start DMA Initiator Receive—Address 7 (Write-only)

This register is written to initiate a DMA receive, from the SCSI bus to the DMA, for initiator operation only. The DMA MODE bit (bit 1) must be true (1) and the TARGETMODE bit (bit 6) must be false (0) in the Mode Register (port 2) prior to writing this register.

# 6.9 Reset Parity/Interrupt—Address 7 (Read-only)

Reading this register resets the PARITY ERROR bit (bit 5), the INTERRUPT REQUEST bit (bit 4) and the BUSY ERROR bit (bit 2) in the Bus and Status Register (port 5).

# SECTION 7 ON-CHIP SCSI HARDWARE SUPPORT

The NCR 5380 is easy to use because of its simple architecture. The chip allows direct control and monitoring of the SCSI bus by providing a latch for each signal. However, portions of the protocol define timings which are much too quick for traditional microprocessors to control. Therefore, hardware support has been provided for DMA transfers, bus arbitration, phase change monitoring, bus disconnection, bus reset, parity generation, parity checking, and device selection/reselection.

Arbitration is accomplished using a bus-free filter to continuously monitor  $\overline{\text{BSY}}$ . If  $\overline{\text{BSY}}$  remains inactive for at least 400 nsec then the SCSI bus is considered free

and arbitration may begin. Arbitration will begin if the bus is free, SEL is inactive and the ARBITRATION bit (port 2, bit 0) is active. Once arbitration has begun (BSY asserted), an arbitration delay of 2.2  $\mu$ sec must elapse before the data bus can be examined to determine if arbitration has been won. This delay must be implemented in the controlling software driver.

The NCR 5380 is a clockless device. Delays such as bus free delay, bus set delay and bus settle delay are implemented using gate delays. These delays may differ between devices because of inherent process variations, but are well within the proposed ANSI X3T9.2 specification (Revision 14B).

# SECTION 8 INTERRUPTS

The NCR 5380 provides an interrupt output (IRQ) to indicate a task completion or an abnormal bus occurrence. The use of interrupts is optional and may be disabled by resetting the appropriate bits in the Mode Register (port 2) or the Select Enable Register (port 4).

When an interrupt occurs, the Bus and Status Register and the Current SCSI Bus Status Register must be read to determine which condition created the interrupt. IRQ (pin 23) can be reset simply by reading the Reset Parity/Interrupt Register (port 7) or by an external chip reset (RESET active for 200 nsec).

Assuming the NCR 5380 has been properly initialized, an interrupt will be generated if the chip is selected or reselected, if an EOP signal occurs during a DMA transfer, if an SCSI bus reset occurs, if a parity error occurs during a data transfer, if a bus phase mismatch occurs, or if an SCSI bus disconnection occurs.

## 8.1 Selection/Reselection

The NCR 5380 can generate a select interrupt if  $\overline{SEL}$  (pin 12) is true (1), its device ID is true (1) and  $\overline{BSY}$  (pin 13) is false for at least a bus settle delay (400 ns). If  $\overline{I/O}$  (pin 17) is active this should be considered a reselect interrupt. The correct ID bit is determined by a match in the Select Enable Register (port 4). Only a single bit match is required to generate an interrupt. This interrupt may be disabled by writing zeros into all bits of the Select Enable Register.

If parity is supported, parity should also be good during the selection phase. Therefore, if the ENABLE PAR-ITY BIT (port 2, bit 5) is active, then the PARITY ERROR bit should be checked to insure that a proper selection has occurred. The ENABLE PARITY INTERRUPT bit need not be set for this interrupt to be generated.

The proposed SCSI specification also requires that no more than two device IDs be active during the selection process. To insure this, the Current SCSI Data Register (port 0) should be read.

The proper values for the Bus and Status Register (port 5) and the Current SCSI Bus Status Register (port 4) are displayed below.

# Bus and Status Register

# 8.2 End of Process (EOP) Interrupt

An End of Process signal (EOP, pin 27) which occurs during a DMA transfer (DMAMODE true) will set the END OF DMA status bit (port 5, bit 7) and will optionally generate an interrupt if ENABLE EOP INTERRUPT bit (port 2, bit 3) is true. The EOP pulse will not be recognized (END OF DMA bit set) unless EOP, DACK and either IOR or IOW are concurrently active for at least 100 nsec. DMA transfers can still occur if EOP/ was not asserted at the correct time. This interrupt can be disabled by resetting the ENABLE EOP INTERRUPT bit.

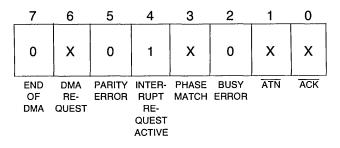

The proper values for the Bus and Status Register (port 5) and the Current SCSI Bus Status Register (port 4) for this interrupt are displayed below.

| 7                | 6                   | 5 | 4 | 3              | 2 | 1   | 0   |

|------------------|---------------------|---|---|----------------|---|-----|-----|

| 1                | 0                   | 0 | 1 | 0              | 0 | 0   | x   |

| END<br>OF<br>DMA | DMA<br>RE-<br>QUEST |   |   | PHASE<br>MATCH |   | ATN | ACK |

#### **Bus and Status Register**

#### **Current SCSI Bus Status Register**

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     |     |     |

| 0   | 1   | X   | X   | X   | X   | 0   | X   |

|     |     |     |     |     |     |     |     |

| RST | BSY | REQ | MSG | C/D | 1/0 | SEL | DBP |

The END OF DMA bit is used to determine when a block transfer is complete. Receive operations are complete when there is no data left in the chip and no additional handshakes occurring. The only exception to this is receiving data as an initiator and the target opts to send additional data for the same phase. In this case, REQ goes active and the new data is present in the Input Data Register. Since a phase mismatch interrupt will not occur, REQ and ACK need to be sampled to determine that the Target is attempting to send more data.

For send operations, the END OF DMA bit is set when the DMA finishes its transfer, but the SCSI transfer may still be in progress. If connected as a Target,  $\overline{\text{REQ}}$ and  $\overline{\text{ACK}}$  should be sampled until both are false. If connected as an Initiator, a phase change interrupt can be used to signal the completion of the previous phase. It is possible for the Target to request additional data for the same phase. In this case, a phase change will not occur and both  $\overline{\text{REQ}}$  and  $\overline{\text{ACK}}$  must be sampled to determine when the last byte was transferred.

#### 8.3 SCSI Bus Reset

The NCR 5380 generates an interrupt when the  $\overrightarrow{RST}$  signal (pin 16) transitions to true. The device releases all bus signals within a bus clear delay (800 nsec) of this transition. This interrupt also occurs after setting the ASSERT  $\overrightarrow{RST}$  bit (port 1, bit 7). This interrupt cannot be disabled. (Note: The  $\overrightarrow{RST}$  signal is not latched in bit 7 of the Current SCSI Bus Status Register and may not be active when this port is read. For this case, the Bus Reset interrupt may be determined by default.)

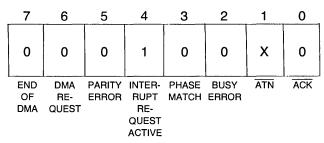

The proper values for the Bus and Status Register (port 5) and the Current SCSI Bus Status Register (port 4) are displayed below.

## 8.4 Parity Error

An interrupt is generated for a received parity error if the ENABLE PARITY CHECK (bit 5) and the ENABLE PARITY INTERRUPT (bit 4) bits are set (1) in the Mode Register (port 2). Parity is checked during a read of the Current SCSI Data Register (port 0) and during a DMA receive operation. A parity error can be detected without generating an interrupt by disabling the ENA-BLE PARITY INTERRUPT bit and checking the PAR-ITY ERROR flag (port 5, bit 5).

The proper values for the Bus and Status Register (port 5) and the Current SCSI Bus Status Register (port 4) are displayed below.

| _ | 7                | 6                   | 5               | 4 | 3              | 2 | 1   | 0   |

|---|------------------|---------------------|-----------------|---|----------------|---|-----|-----|

|   | 0                | х                   | 1               | 1 | 1              | 0 | x   | x   |

|   | END<br>OF<br>DMA | DMA<br>RE-<br>QUEST | PARITY<br>ERROR |   | PHASE<br>MATCH |   | ATN | ACK |

#### **Bus and Status Register**

#### Current SCSI Bus Status Register

|   | 7   | 6   | 5   | 4   | 3   | _2  | 1   | 0   | 1 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|---|

|   | x   | x   | x   | x   | x   | x   | x   | х   |   |

| • | RST | BSY | REQ | MSG | C/D | 1/0 | SEL | DBP |   |

# Bus and Status Register

#### **Current SCSI Bus Status Register**

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |   |

|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 0   | 1   | 1   | x   | x   | x   | 0   | х   |   |

| RST | BSY | REQ | MSG | C/D | 1/0 | SEL | DBP | • |

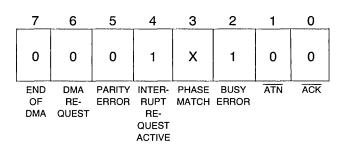

## 8.5 Bus Phase Mismatch

The SCSI phase lines are comprised of the signals  $\overline{I/O}$ ,  $\overline{C/D}$  and  $\overline{MSG}$ . These signals are compared with the corresponding bits in the Target Command Register: ASSERT  $\overline{I/O}$  (bit 0), ASSERT  $\overline{C/D}$  (bit 1) and ASSERT  $\overline{MSG}$  (bit 2). The comparison occurs continually and is reflected in the PHASE MATCH bit (bit 3) of the Bus and Status Register (port 5). If the DMA MODE bit (port 2, bit 1) is active and a phase mismatch occurs when  $\overline{REQ}$  (pin 20) transitions from false to true, an interrupt (IRQ) is generated.

A phase mismatch prevents the recognition of REQ and removes the chip from the bus during an initiator send operation. (DB0-DB7, DBP will not be driven even though the ASSERT DATA BUS bit (port 1, bit 0) is active.) This interrupt is only significant when connected as an Initiator and may be disabled by resetting the DMA MODE bit. (Note: It is possible for this interrupt to occur when connected as a Target if another device is driving the phase lines to a different state.)

The proper values for the Bus and Status Register (port 5) and the Current SCSI Bus Status Register (port 4) are displayed below.

# Bus and Status Register

#### **Current SCSI Bus Status Register**

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |   |

|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 0   | 1   | х   | x   | х   | х   | 0   | х   |   |

| RST | BSY | REQ | MSG | C/D | 1/0 | SEL | DBP | • |

## 8.6 Loss of BSY

If the MONITOR BUSY bit (bit 2) in the Mode Register (port 2) is active, an interrupt will be generated if the BSY signal (pin 13) goes false for at least a bus settle delay (400 nsec). This interrupt may be disabled by resetting the MONITOR BUSY bit. Register values are as follows.

**Current SCSI Bus Status Register**

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | x   | x   | x   | 0   | 0   |

| RST | BSY | REQ | MSG | C/D | 1/0 | SEL | DBP |

# SECTION 9 RESET CONDITIONS

Three possible reset situations exist with the NCR 5380, as follows:

# 9.1 Hardware Chip Reset

When the signal RESET/ (pin 28) is active for at least 200 nsec, the NCR 5380 device is re-initialized and all internal logic and control registers are cleared. This is a chip reset only and does not create an SCSI bus reset condition.

# 9.2 SCSI Bus Reset (RST) Received

When an SCSI RST signal (pin 16) is received, an IRQ interrupt is generated and a chip reset is performed. All internal logic and registers are cleared, except for the IRQ interrupt latch and the ASSERT RST bit (bit 7) in

the Initiator Command Register (port 1). (Note: The RST signal may be sampled by reading the Current SCSI Bus Status Register (port 4); however, this signal is not latched and may not be present when this port is read.)

# 9.3 SCSI Bus Reset (RST) Issued

If the CPU sets the ASSERT RST bit (bit 7) in the Initiator Command Register (port 1), the RST signal (pin 16) goes active on the SCSI bus and an internal reset is performed. Again, all internal logic and registers are cleared except for the IRQ interrupt latch and the ASSERT RST bit (bit 7) in the Initiator Command Register (port 1). The RST signal will continue to be active until the ASSERT RST bit is reset or until a hardware reset occurs.

# SECTION 10 DATA TRANSFERS

Data may be transferred between SCSI bus devices in one of four modes: Programmed I/O; Normal DMA; Block Mode DMA; or Pseudo DMA. The following sections describe these modes in detail. (Note: For all data transfers operations DACK and CS should never be active simultaneously.)

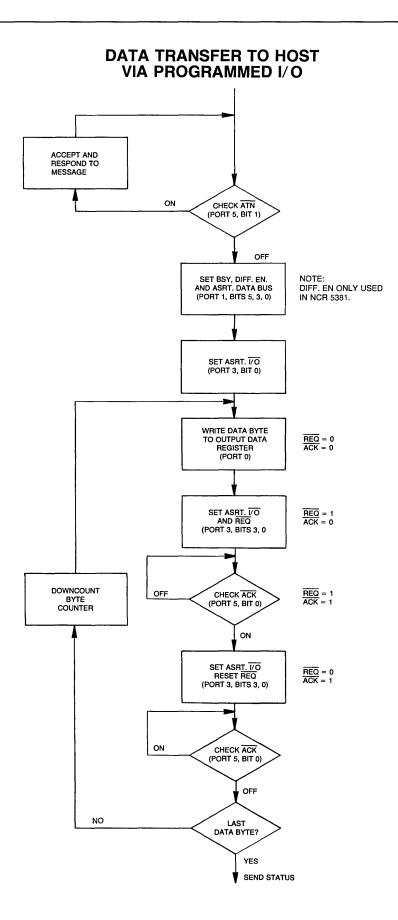

# 10.1 Programmed I/O Transfers

Programmed I/O is the most primitive form of data transfer. The  $\overline{REQ}$  (pin 20) and  $\overline{ACK}$  (pin 14) hand-shake signals are individually monitored and asserted by reading and writing the appropriate register bits. This type of transfer is normally used when transferring small blocks of data such as command blocks or message and status bytes.

An Initiator send operation would begin by setting the  $\overline{C/D}$ ,  $\overline{I/O}$ , and  $\overline{MSG}$  bits in the Target Command Register to the correct state so that a phase match exists. In addition to the phase match condition, it is necessary for the ASSERT DATA BUS bit (port 1, bit 0) to be true and the received  $\overline{I/O}$  signal to be false for the 5380 to send data.

For each transfer, the data is loaded into the Output Data Register (port 0). The MPU then waits for the REQ bit (port 4, bit 5) to become active. Once REQ goes active the PHASE MATCH bit (port 5, bit 3) is checked and the ASSERT ACK bit (port 1, bit 4) is set. The REQ bit is sampled until it becomes false and the MPU resets the ASSERT ACK bit to complete the transfer.

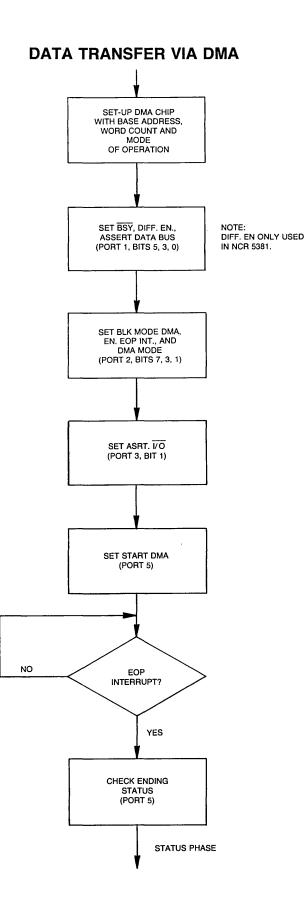

## **10.2 Normal DMA Mode**

DMA transfers are normally used for large block transfers. The SCSI chip outputs a DMA request (DRQ - pin 22) whenever it is ready for a byte transfer. External DMA logic uses this DRQ signal to generate DACK and an IOR or an IOW pulse to the NCR 5380. DRQ goes inactive when DACK is asserted and DACK goes inactive sometime after the minimum read or write pulse width. This process is repeated for every byte. For this mode, DACK should not be allowed to cycle unless a transfer is taking place.

Refer to Section 10.5 for information on halting a DMA transfer.

# 10.3 Block Mode DMA

Some popular DMA controllers such as the Intel 8237 provide a block mode DMA transfer. This type of transfer allows the DMA controller to transfer blocks of data without relinquishing the use of the data bus to the MPU after each byte is transferred. Thus, faster transfer rates are achieved by eliminating the repetitive access and release of the MPU bus.

If the BLOCK MODE DMA bit (port 2, bit 7) is active, the NCR 5380 will begin the transfer by asserting DRQ. The DMA controller then asserts  $\overrightarrow{DACK}$  for the remainder of the block transfer. DRQ goes inactive after detecting  $\overrightarrow{DACK}$  and also remains inactive for the duration of the transfer. The READY output (pin 25) is used to control the transfer rate.

Non-block mode DMA transfers end when DACK goes false, whereas block mode transfers end when IOR or IOW becomes inactive. Since this is the case, DMA transfers may be started sooner in a block mode transfer. To obtain optimum performance in block mode operation, the DMA logic may optionally use the normal DMA mode interlocking handshake. READY is still available to throttle the DMA transfer, but DRQ is 30 to 40 nsec faster than READY and may be used to start the cycle sooner.

The methods described in Section 10.5 "Halting A DMA Operation" apply for all DMA operations.

# 10.4 Pseudo DMA Mode

To avoid the tedium of monitoring and asserting the request/ acknowledge handshake signals for programmed I/O transfers, the system may be designed to implement a pseudo DMA mode. This mode is implemented by programming the NCR 5380 to operate in the DMA mode, but using the MPU to emulate the DMA handshake. DRQ (pin 22) may be detected by polling the DMA REQ bit (bit 6) in the Bus and Status Register (port 5), by sampling the signal through an external port or by using it to generate an MPU interrupt. Once DRQ is detected, the MPU can perform a DMA port read or write data transfer. This MPU read/write is externally decoded to generate the appropriate DACK and IOR or IOW signals.

Often, external decoding logic is necessary to generate the NCR 5380  $\overline{CS}$  signal. This same logic may be used to generate DACK at no extra system cost and provide an increased performance in programmed IO transfers.

# 10.5 Halting A DMA Operation

The  $\overrightarrow{\text{EOP}}$  signal is not the only way to halt a DMA transfer. A bus phase mismatch or a reset of the DMA MODE bit (port 2, bit 1) can also terminate a DMA cycle for the current bus phase.

# 10.5.1 Using the EOP Signal

If  $\overline{\text{EOP}}$  is used, it should be asserted for at least 100 nsec while DACK and  $\overline{\text{IOR}}$  or  $\overline{\text{IOW}}$  are simultaneously active. Note, however, that if  $\overline{\text{IOR}}$  or  $\overline{\text{IOW}}$  is not active an interrupt will be generated, but the DMA activity will continue. The  $\overline{\text{EOP}}$  signal does not reset the DMA MODE bit. Since the  $\overline{\text{EOP}}$  signal can occur during the last byte sent to the Output Data Register (port 0), the  $\overline{\text{REQ}}$  and  $\overline{\text{ACK}}$  signals should be monitored to insure that the last byte has transferred.

# 10.5.2 Bus Phase Mismatch Interrupt

A bus phase mismatch interrupt may be used to halt the transfer if operating as an Initiator. Using this method frees the host from maintaining a data length counter and frees the DMA logic from providing the EOP signal. If performing an initiator send operation, the NCR 5380 requires DACK to cycle before ACK goes inactive. Since phase changes cannot occur if ACK is active, either DACK must be cycled after the last byte is sent or the DMA MODE bit must be reset in order to receive the phase mismatch interrupt.

# 10.5.3 Resetting the DMA MODE Bit

A DMA operation may be halted at any time simply by resetting the DMA MODE bit. It is recommended that the DMA MODE bit be reset after receiving an EOP or bus phase mismatch interrupt. The DMA MODE bit must then be set before writing any of the start DMA registers for subsequent bus phases.

If resetting the DMA MODE bit is used instead of  $\overline{\text{EOP}}$  for Target role operation, then care must be taken to reset this bit at the proper time. If receiving data as a target device, the DMA MODE bit must be reset once the last DRQ is received and before DACK is asserted to prevent an additional  $\overline{\text{REQ}}$  from occurring. Resetting this bit causes DRQ to go inactive. However, the last byte received remains in the Input Data Register and may be obtained either by performing a normal MPU read or by cycling DACK and IOR. In most cases  $\overline{\text{EOP}}$  is easier to use when operating as a Target device.

# SECTION 11 EXTERNAL TIMING DIAGRAMS

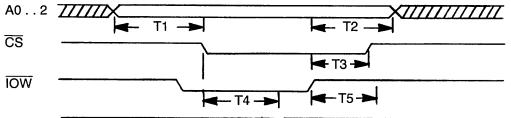

## **11.1 CPU WRITE**

| NAME | DESCRIPTION                          | MIN. | TYP. | MAX. | UNITS |

|------|--------------------------------------|------|------|------|-------|

| T1   | Address setup to write enable *      | 20   |      |      | ns.   |

| T2   | Address hold from end write enable * | 20   |      |      | ns.   |

| Т3   | Write enable width *                 | 70   |      |      | ns.   |

| T4   | Chip select hold from end of IOW     | 0    |      |      | ns.   |

| T5   | Data setup to end of write enable *  | 50   |      |      | ns.   |

| Т6   | Data hold time from end of IOW       | 30   |      |      | ns.   |

$^{\ast}$  Write enable is the occurrence of  $\overline{\text{IOW}}$  and  $\overline{\text{CS}}$

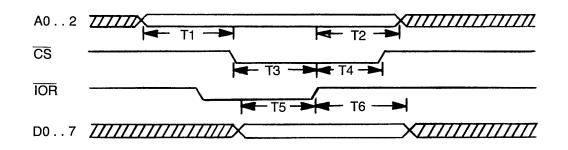

## 11.2 CPU READ

D0..7

| NAME | DESCRIPTION                         | MIN. | TYP. | MAX. | UNITS |

|------|-------------------------------------|------|------|------|-------|

| T1   | Address setup to read enable *      | 20   |      |      | ns.   |

| T2   | Address hold from end read enable * | 20   |      |      | ns.   |

| T3   | Chip select hold from end of IOR    | 0    |      |      | ns.   |

| T4   | Data access time from read enable * |      |      | 130  | ns.   |

| T5   | Data hold time from end of IOR      | 20   |      |      | ns.   |

\* Read enable is the occurrence of  $\overline{\text{IOR}}$  and  $\overline{\text{CS}}$

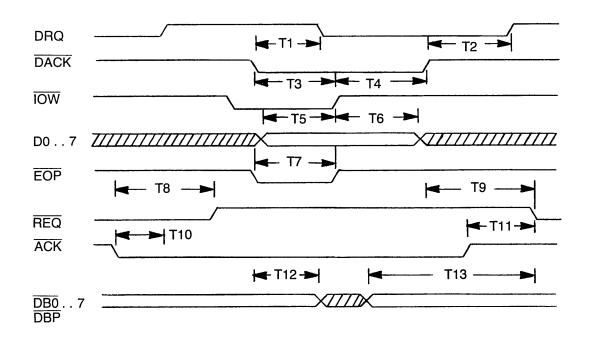

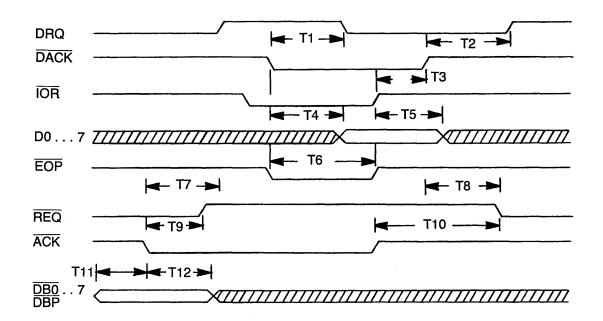

| NAME | DESCRIPTION                         | MIN. | TYP. | MAX. | UNITS |

|------|-------------------------------------|------|------|------|-------|

| T1   | DRQ false from DACK true            |      |      | 130  | ns.   |

| T2   | DACK false to DRQ true              | 30   |      |      | ns.   |

| Т3   | Write enable width *                | 100  |      |      | ns.   |

| T4   | DACK hold from end of IOW           | 0    |      |      | ns.   |

| T5   | Data setup to end of write enable * | 50   |      |      | ns.   |

| Т6   | Data hold time from end of IOW      | 40   |      |      | ns.   |

| T7   | Width of EOP pulse (note 1)         | 100  |      |      | ns.   |

| Т8   | ACK true to REQ false               | 25   | 110  | 125  | ns.   |

| Т9   | REQ from end of DACK (ACK false)    | 30   | 140  | 150  | ns.   |

| T10  | ACK true to DRQ true (target)       | 15   | 100  | 110  | ns.   |

| T11  | REQ from end of ACK (DACK false)    | 20   | 140  | 150  | ns.   |

| T12  | DATA hold from write enable         | 15   |      |      | ns.   |

| T13  | Data setup to REQ true (target)     | 60   |      |      | ns.   |

$\ast$  Write enable is the occurrence of  $\overline{\text{IOW}}$  and  $\overline{\text{DACK}}$

Note 1:  $\overline{\text{EOP}}$ ,  $\overline{\text{IOW}}$ , and  $\overline{\text{DACK}}$  must be concurrently true for at least T7 for proper recognition of the  $\overline{\text{EOP}}$  pulse.

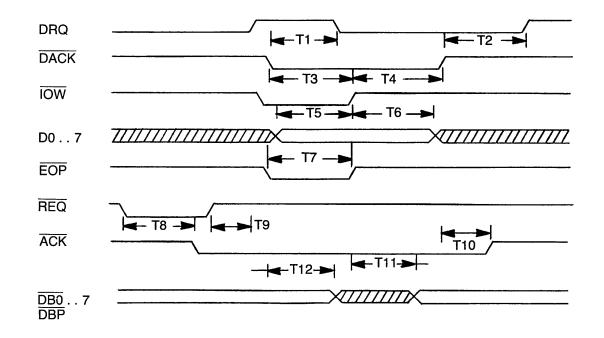

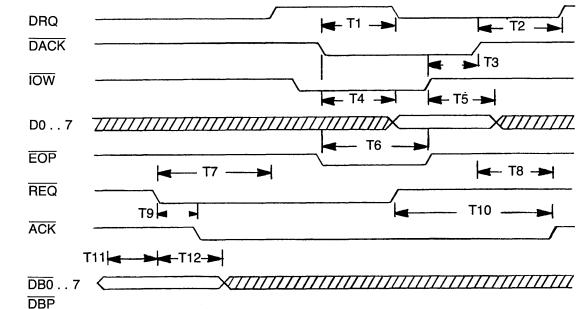

# 11.4 DMA WRITE (NON-BLOCK MODE) INITIATOR SEND

| NAME | DESCRIPTION                                     | MIN. | TYP. | MAX. | UNITS |

|------|-------------------------------------------------|------|------|------|-------|

| T1   | DRQ false from DACK true                        |      |      | 130  | ns.   |

| T2   | DACK false to DRQ true                          | 30   |      |      | ns.   |

| Т3   | Write enable width *                            | 100  |      |      | ns.   |

| T4   | DACK hold from end of IOW                       | 0    |      |      | ns.   |

| T5   | Data setup to end of write enable *             | 50   |      |      | ns.   |

| T6   | Data hold time from end of IOW                  | 40   |      |      | ns.   |

| T7   | Width of $\overline{\text{EOP}}$ pulse (note 1) | 100  |      |      | ns.   |

| Т8   | REQ true to ACK true                            | 20   | 150  | 160  | ns.   |

| Т9   | REQ false to DRQ true                           | 20   | 100  | 110  | ns.   |

| T10  | DACK false to ACK false                         | 25   | 140  | 150  | ns.   |

| T11  | IOW false to valid SCSI data                    |      |      | 100  | ns.   |

| T12  | DATA hold from write enable                     | 15   |      |      | ns.   |

$\ast$  Write enable is the occurrence of  $\overline{\text{IOW}}$  and  $\overline{\text{DACK}}$

Note 1:  $\overline{EOP}$ ,  $\overline{IOW}$ , and  $\overline{DACK}$  must be concurrently true for at least T7 for proper recognition of the  $\overline{EOP}$  pulse.

# 11.5 DMA READ (NON-BLOCK MODE) TARGET RECEIVE

| NAME | DESCRIPTION                         | MIN. | TYP. | MAX. | UNITS |

|------|-------------------------------------|------|------|------|-------|

| T1   | DRQ false from DACK true            |      |      | 130  | ns.   |

| T2   | DACK false to DRQ true              | 30   |      |      | ns.   |

| Т3   | DACK hold time from end of IOR      | 0    |      |      | ns.   |

| T4   | Data access time from read enable * |      |      | 115  | ns.   |

| T5   | Data hold time from end of IOR      | 20   |      |      | ns.   |

| T6   | Width of EOP pulse (note 1)         | 100  |      |      | ns.   |

| T7   | ACK true to DRQ true                | 15   | 100  | 110  | ns.   |

| T8   | DACK false to REQ true (ACK false)  | 30   |      | 150  | ns.   |

| Т9   | ACK true to REQ false               | 25   | 110  | 125  | ns.   |

| T10  | ACK false to REQ true (DACK false)  | 20   | 140  | 150  | ns.   |

| T11  | DATA setup time to ACK              | 20   |      |      | ns.   |

| T12  | DATA hold time from ACK             | 50   |      |      | ns.   |

\* Read enable is the occurrence of  $\overline{\text{IOR}}$  and  $\overline{\text{DACK}}$

Note 1:  $\overline{EOP}$ ,  $\overline{IOR}$ , and  $\overline{DACK}$  must be concurrently true for at least T6 for proper recognition of the  $\overline{EOP}$  pulse.

| _ | DB07 <<br>DBP | ×1111111111111111111111111111111111111 |      | ///// | 1111 | ////// |

|---|---------------|----------------------------------------|------|-------|------|--------|

|   | NAME          | DESCRIPTION                            | MIN. | TYP.  | MAX. | UNITS  |

|   | T1_           | DRQ false from DACK true               |      |       | 130  | ns.    |

|   | T2            | DACK false to DRQ true                 | 30   |       |      | ns.    |

|   | Т3            | DACK hold time from end of IOR         | 0    |       |      | ns.    |

|   | T4            | Data access time from read enable *    |      |       | 115  | ns.    |

|   | T5            | Data hold time from end of IOR         | 20   |       | -    | ns.    |

| T4  | Data access time from read enable * |     |     | 115 | ns. |

|-----|-------------------------------------|-----|-----|-----|-----|

| T5  | T5 Data hold time from end of IOR   |     |     |     | ns. |

| T6  | Width of EOP pulse (note 1)         | 100 |     |     | ns. |

| T7  | REQ true to DRQ true                | 20  | 140 | 150 | ns. |

| T8  | DACK false to ACK false (REQ false) | 25  | 140 | 160 | ns. |

| Т9  | REQ true to ACK true                | 20  | 150 | 160 | ns. |

| T10 | REQ false to ACK false (DACK false) | 15  | 120 | 140 | ns. |

| T11 | DATA setup time to REQ              | 20  |     |     | ns. |

| T12 | DATA hold time from REQ             | 50  |     |     | ns. |

\*Read enable is the occurrence of  $\overline{\text{IOR}}$  and  $\overline{\text{DACK}}$

Note 1:  $\overline{EOP}$ ,  $\overline{IOR}$ , and  $\overline{DACK}$  must be concurrently true for at least T6 for proper recognition of the  $\overline{EOP}$  pulse.

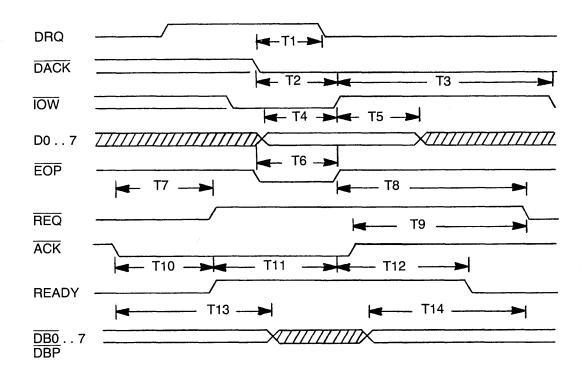

# 11.6 DMA READ (NON-BLOCK MODE) INITIATOR RECEIVE

| NAME | DESCRIPTION                         | MIN. | TYP. | MAX. | UNITS |

|------|-------------------------------------|------|------|------|-------|

| T1   | DRQ false from DACK true            |      |      | 130  | ns.   |

| T2   | Write enable width *                | 100  |      |      | ns.   |

| Т3   | Write recovery time                 | 120  |      |      | ns.   |

| T4   | Data setup to end of write enable * | 50   |      |      | ns.   |

| T5   | Data hold time from end of IOW      | 40   |      |      | ns.   |

| Т6   | Width of EOP pulse (note 1)         | 100  |      |      | ns.   |

| T7   | ACK true to REQ false               | 25   | 110  | 125  | ns.   |

| Т8   | REQ from end of IOW (ACK false)     | 40   |      | 180  | ns.   |

| Т9   | REQ from end of ACK (IOW false)     | 20   | 160  | 170  | ns.   |

| T10  | ACK true to READY true              | 20   | 130  | 140  | ns.   |

| T11  | READY true to IOW false             | 70   |      |      | ns.   |

| T12  | IOW false to READY false            | 20   | 130  | 140  | ns.   |

| T13  | DATA hold from ACK true             | 40   |      |      | ns.   |

| T14  | Data setup to REQ true              | 60   |      |      | ns.   |

$\ast$  Write enable is the occurrence of  $\overline{\text{IOW}}$  and  $\overline{\text{DACK}}$

Note 1:  $\overline{EOP}$ ,  $\overline{IOW}$ , and  $\overline{DACK}$  must be concurrently true for at least T6 for proper recognition of the  $\overline{EOP}$  pulse.

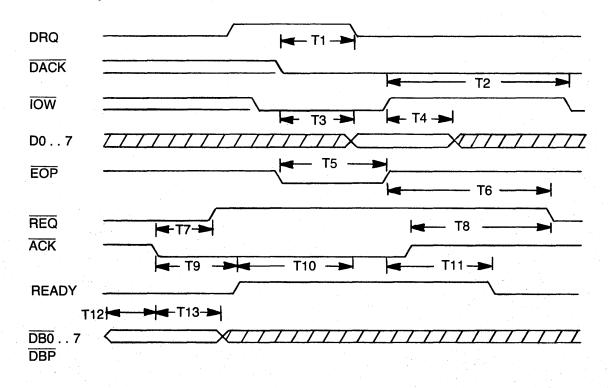

# 11.8 DMA READ (BLOCK MODE) TARGET RECEIVE

| NAME | DESCRIPTION                         | MIN. | TYP. | MAX. | UNITS |

|------|-------------------------------------|------|------|------|-------|

| T1   | DRQ false from DACK true            |      |      | 130  | ns.   |

| T2   | IOR recovery time                   | 120  |      |      | ns.   |

| Т3   | Data access time from read enable * |      | 100  | 110  | ns.   |

| T4   | Data hold time from end of IOR      | 20   |      |      | ns.   |

| T5   | Width of EOP pulse (note 1)         | 100  |      |      | ns.   |

| T6   | IOR false to REQ true (ACK false)   | 30   | 180  | 190  | ns.   |

| T7   | ACK true to REQ false               | 25   | 110  | 125  | ns.   |

| T8   | ACK false to REQ true (IOR false)   | 20   | 160  | 170  | ns.   |

| Т9   | ACK true to READY true              | 20   | 130  | 140  | ns.   |

| T10  | READY true to valid data            |      |      | 50   | ns.   |

| T11  | IOR false to READY false            | 20   | 125  | 140  | ns.   |

| T12  | DATA setup time to ACK              | 20   |      |      | ns.   |

| T13  | DATA hold time from ACK             | 50   |      |      | ns.   |

\* Read enable is the occurrence of IOR and DACK

Note 1:  $\overline{EOP}$ ,  $\overline{IOR}$ , and  $\overline{DACK}$  must be concurrently true for at least T5 for proper recognition of the  $\overline{EOP}$  pulse.

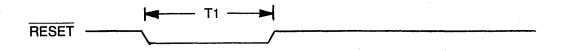

# 11.9 RESET

| NAME | DESCRIPTION            | MIN. | TYP. | MAX. | UNITS |

|------|------------------------|------|------|------|-------|

| T1   | Minimum width of reset | 200  |      |      | ns.   |

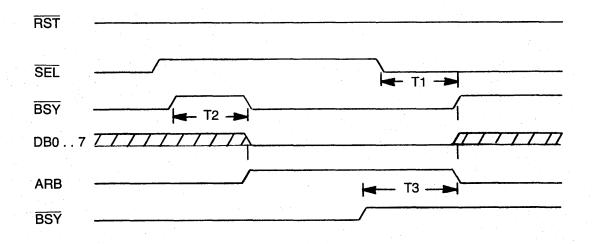

# **11.10 ARBITRATION**

| NAME | DESCRIPTION                    | MIN. | TYP. | MAX. | UNITS |

|------|--------------------------------|------|------|------|-------|

| T1   | Bus clear from SEL true        |      |      | 600  | ns.   |

| T2   | ARBITRATE start from BSY false | 1200 |      | 2200 | ns.   |

| Т3   | Bus clear from BSY false       |      |      | 1100 | ns.   |

# APPENDICES A1. NCR 5380 vs. NCR 5385/86

The NCR 5380 was designed to provide a low-cost SCSI interface using a minimum number of parts. Much of the intelligence and some of the features included in the NCR 5385/86 have been removed. In some instances, such as arbitration, this causes the controlling CPU to provide more of the protocol control. The NCR 5385/86 remains appropriate for many applications and will continue to be strongly supported.

The main differences between the NCR 5380 and the NCR 5385/86 are shown in the following table.

| Functional Areas      | 5380                               | 5385/86                  |

|-----------------------|------------------------------------|--------------------------|

| Arbitration           | Optional,<br>Firmware<br>Dependant | Automatically<br>Invoked |

| Maximum Transfer Rate | 1.5 MBPS                           | 2.5 MBPS                 |

| Transfer Counter      | None                               | 24 bits                  |

| Data Buffering        | Single                             | Double                   |

| Clock Circuitry       | None Req'd                         | 5-10 MHz                 |

| O.C. Transceivers     | On-chip                            | External                 |

| Differential Pair     | External<br>(NCR 5381)             | External                 |

| Synchronous Mode      | No Firm<br>Plans                   | NCR 5386s                |

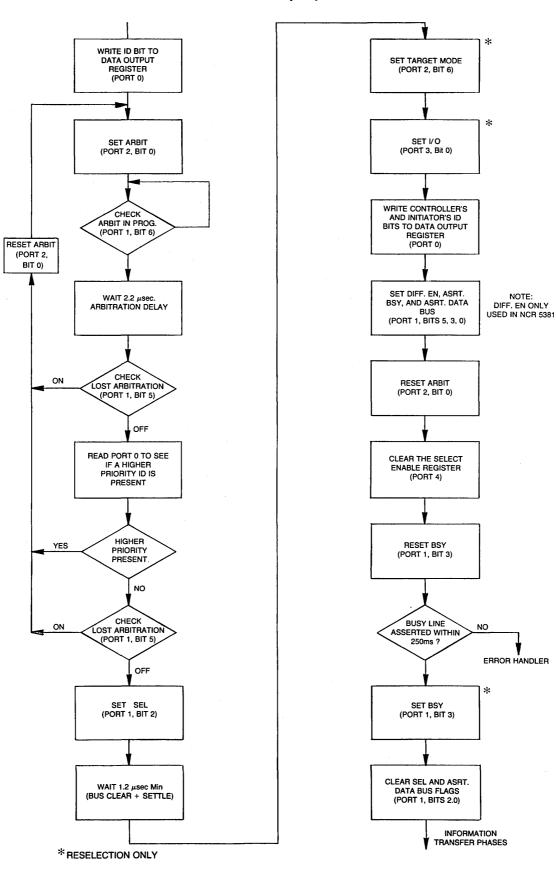

# A2. FLOWCHARTS/SOFTWARE

Flowcharts and sample software drivers are provided as a guideline to facilitate your firmware development. Firmware will vary depending on the application and the level of the SCSI protocol being supported.

**ARBITRATION AND (RE) SELECTION**

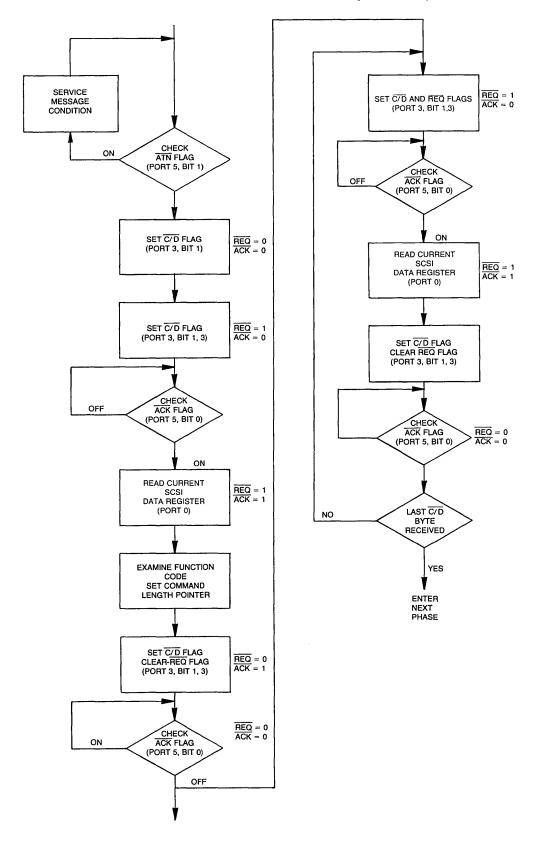

COMMAND TRANSFER PHASE (TARGET)

| LINE# | LOC            | CODE | LINE   |                                       |              |                   |          |       |                             |

|-------|----------------|------|--------|---------------------------------------|--------------|-------------------|----------|-------|-----------------------------|

| 00001 | ଌଌଌଌ           |      | :      | NCR                                   | 5380         | SCSI              | PROTOC   | ю     |                             |

| 00002 | ଉଉଉଭ           |      |        |                                       |              |                   |          |       |                             |

| 00003 |                |      |        | SUPE                                  | ORTS         | вотн              | INITIA   | 277   | OR AND TARGET ROLES         |

| 00004 | 0000           |      | 7      |                                       | w            |                   |          |       |                             |

| 00005 | 0000           |      |        |                                       | IMCC -       | гыдт -            |          | мс    | AND BLOCK (CDB),            |

| 00006 | 0000           |      |        |                                       |              |                   |          |       | THE EXPECTED PHASE          |

|       | 0000           |      |        |                                       |              |                   |          |       |                             |

| 00007 |                |      | ,      | IHBL                                  |              | VE BE             | IN SPEL  | . 1 6 | FIED IN MEMORY              |

| 00008 | 0000           |      | ;      |                                       |              |                   |          |       |                             |

| 00009 | 0000           |      |        |                                       | =\$Ø1        |                   |          | •     | SELECTION FAILED STATUS     |

| 00010 | 0000           |      |        |                                       | =\$02        |                   |          |       | DISCONNECTED STATUS         |

| 00011 | 0000           |      |        |                                       | *\$03        |                   |          |       | PARITY ERROR STATUS         |

| 00012 | 0000           |      | BUS    | RST=                                  | =\$Ø4        |                   |          | -     | SCSI BUS RESET STATUS       |

| 00013 | 0000           |      | CHI    | PFL=                                  | =\$05        |                   |          |       | CHIP FAILURE STATUS         |

| 00014 | 0000           |      | MES    | SAG=                                  | =\$06        |                   |          | ş     | MESSAGE IN BYTE BEING RETND |

| 00015 | ଡ଼ଡ଼ଡ଼ଡ଼       |      | DIF    | FPH=                                  | =\$Ø7        |                   |          | ş     | UNEXPECTED PHASE REQUESTED  |

| 00016 | 0000           |      | ş      |                                       |              |                   |          |       |                             |

| 00017 | 0000           |      | CMD    | CPL=                                  | \$00         |                   |          | ş     | COMMAND COMPLETE MESSAGE    |

| 00018 | ଉଉଉଭ           |      | ;      |                                       |              |                   |          |       |                             |

| 00019 | ଉଡଡଡ           |      | DAT    | -<br>1ØI=4                            | i di di      |                   |          | ÷     | DATA OUT PHASE              |

| 00020 | 0000           |      | CMD    | =\$Ø8                                 | 3            |                   |          |       | COMMAND PHASE               |

| 00021 | ୦ଡଡଡ           |      | STA    | เประ                                  | •\$ØC        |                   |          |       | STATUS PHASE                |

| 00022 | 0000           |      |        |                                       | 5Ø4          |                   |          |       | DATA IN PHASE               |

| 00023 | 0000           |      |        |                                       | 18           |                   |          |       | MESSAGE OUT PHASE           |

| 00024 | 0000           |      |        |                                       | 51C          |                   |          |       | MESSAGE IN PHASE            |

| 00025 | ଉଉଉଡ           |      |        |                                       | \$8Ø         |                   |          |       | FLAG TO DISCONNECT          |

| 00026 | 0000           |      |        |                                       | ≠02<br>=\$4Ø |                   |          |       | FLAG TOWAIT FOR SELECTION   |

| 00027 | ଅଅଅଅ           |      |        |                                       | - 4/ 7 42/   |                   |          | *     | TERO SOWAIT FOR DELECTION   |

| 00028 | 0000           |      | •      | ¢=∈                                   | DEØØ         |                   |          |       | 5380 ADDRESS SPACE          |

| 00029 | 0000           |      |        |                                       | )EØC         |                   |          |       | PSEUDO DMA ADDRESS          |