# DS75160A/DS75161A/DS75162A IEEE-488 GPIB Transceivers

### **General Description**

This family of high-speed-Schottky 8-channel bi-directional transceivers is designed to interface TTL/MOS logic to the IEEE Standard 488-1978 General Purpose Interface Bus (GPIB). PNP inputs are used at all driver inputs for minimum loading, and hysteresis is provided at all receiver inputs for added noise margin. The IEEE-488 required bus termination is provided internally with an active turn-off feature which disconnects the termination from the bus when V<sub>CC</sub> is removed.

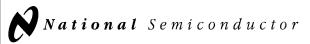

The General Purpose Interface Bus is comprised of 16 signal lines — 8 for data and 8 for interface management. The data lines are always implemented with DS75160A, and the management lines are either implemented with DS75161A in a single-controller system, or with DS75162A in a multicontroller system.

## Features

- 8-channel bi-directional non-inverting transceivers

- Bi-directional control implemented with TRI-STATE® output design

- Meets IEEE Standard 488-1978

- High-speed Schottky design

- Low power consumption

- High impedance PNP inputs (drivers)

- 500 mV (typ) input hysteresis (receivers)

- On-chip bus terminators

- No bus loading when V<sub>CC</sub> is removed

- Pin selectable open collector mode on DS75160A driver outputs

- Accommodates multi-controller systems

© 1996 National Semiconductor Corporation TL/F/5804

RRD-B30M36/Printed in U. S. A.

http://www.national.com

DS75160A/DS75161A/DS75162A IEEE-488 GPIB Transceivers

February 1996

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage, V <sub>CC</sub>                      | 7.0V                              |

|------------------------------------------------------|-----------------------------------|

| Input Voltage                                        | 5.5V                              |

| Storage Temperature Range                            | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Lead Temperature (Soldering, 4 sec.)                 | 260°C                             |

| Maximum Power Dissipation* at 25°C<br>Molded Package | 1897 mW                           |

| *Derate molded package 15.2 mW/°C above 25°C.        |                                   |

| Oper | ating | Cond | itions |

|------|-------|------|--------|

|      |       |      |        |

|                                      | Min  | Max  | Units |

|--------------------------------------|------|------|-------|

| V <sub>CC</sub> , Supply Voltage     | 4.75 | 5.25 | V     |

| T <sub>A</sub> , Ambient Temperature | 0    | 70   | °C    |

| I <sub>OL</sub> , Output Low Current |      |      |       |

| Bus                                  |      | 48   | mA    |

| Terminal                             |      | 16   | mA    |

|                                      |      |      |       |

## Electrical Characteristics (Notes 2 and 3)

| Symbol            | Param                                  | eter         |                                             | Conditions                            | Min  | Тур  | Max         | Units |

|-------------------|----------------------------------------|--------------|---------------------------------------------|---------------------------------------|------|------|-------------|-------|

| VIH               | High-Level Input Vol                   | tage         |                                             | 2                                     |      |      | V           |       |

| VIL               | Low-Level Input Vol                    | tage         |                                             |                                       |      | 0.8  | V           |       |

| V <sub>IK</sub>   | Input Clamp Voltage                    | 1            | $I_{I} = -18 \text{ mA}$                    |                                       |      | -0.8 | -1.5        | V     |

| V <sub>HYS</sub>  | Input Hysteresis                       | Bus          |                                             |                                       | 400  | 500  |             | mV    |

| V <sub>OH</sub>   | High-Level                             | Terminal     | $I_{OH} = -800$                             | μΑ                                    | 2.7  | 3.5  |             | v     |

|                   | Output Voltage                         | Bus (Note 5) | $I_{OH} = -5.2$                             | mA                                    | 2.5  | 3.4  |             | Ů     |

| V <sub>OL</sub>   | Low-Level                              | Terminal     | I <sub>OL</sub> = 16 mA                     |                                       |      | 0.3  | 0.5         | v     |

|                   | Output Voltage                         | Bus          | I <sub>OH</sub> = 48 mA                     | ,                                     |      | 0.4  | 0.5         | Ů     |

| IIH               | High-Level                             | Terminal and | $V_{I} = 5.5V$                              |                                       |      | 0.2  | 100         | μA    |

|                   | Input Current                          | TE, PE, DC,  | $V_{I} = 2.7V$                              |                                       |      | 0.1  | 20          | μ/(   |

| IIL               | Low-Level<br>Input Current             | SC Inputs    | $V_{I} = 0.5V$                              |                                       |      | -10  | -100        | μΑ    |

| V <sub>BIAS</sub> | Terminator Bias<br>Voltage at Bus Port |              | Driver<br>Disabled                          | $I_{I(bus)} = 0$ (No Load)            | 2.5  | 3.0  | 3.7         | v     |

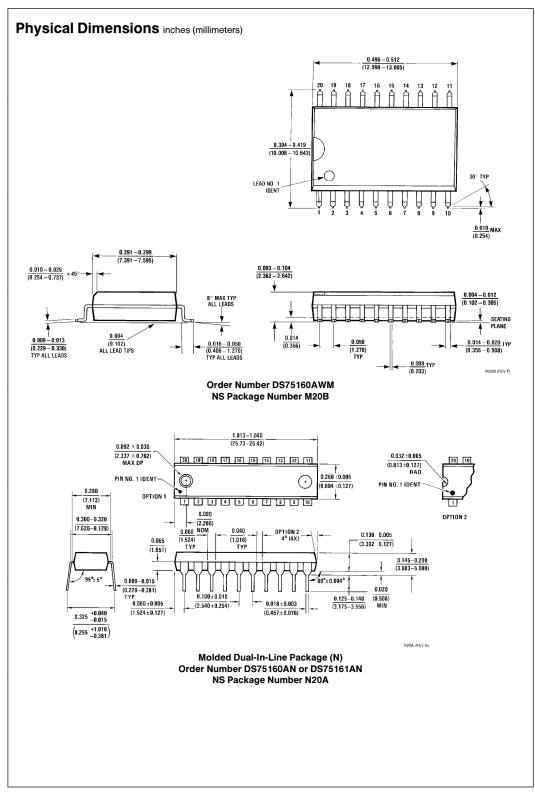

| ILOAD             | Terminator                             |              |                                             | $V_{I(bus)} = -1.5V \text{ to } 0.4V$ | -1.3 |      |             |       |

|                   | Bus Loading<br>Current B               |              | Driver<br>Disabled                          | $V_{l(bus)} = 0.4V$ to 2.5V           | 0    |      | -3.2        |       |

|                   |                                        | Bus          |                                             | $V_{l(bus)} = 2.5V \text{ to } 3.7V$  |      |      | 2.5<br>-3.2 | mA    |

|                   |                                        |              |                                             | $V_{I(bus)} = 3.7V \text{ to } 5V$    | 0    |      | 2.5         |       |

|                   |                                        |              |                                             | $V_{I(bus)} = 5V \text{ to } 5.5V$    | 0.7  |      | 2.5         |       |

|                   |                                        |              | $V_{\rm CC} = 0V, V_{\rm CC}$               | (bus) = 0V  to  2.5V                  |      |      | 40          | μA    |

| I <sub>OS</sub>   | Short-Circuit                          | Terminal     | $V_{I} = 2V, V_{O}$                         | = 0V (Note 4)                         | -15  | -35  | -75         | mA    |

|                   | Output Current                         | Bus (Note 5) |                                             |                                       | -35  | -75  | -150        |       |

| ICC               | Supply Current                         | DS75160A     | Transmit, TE                                | $= 2V, PE = 2V, V_1 = 0.8V$           |      | 85   | 125         |       |

|                   |                                        |              | Receive, TE = 0.8V, PE = 2V, $V_{l} = 0.8V$ |                                       |      | 70   | 100         | mA    |

|                   |                                        | DS75161A     | $TE = 0.8V, DC = 0.8V, V_I = 0.8V$          |                                       |      | 84   | 125         |       |

|                   |                                        | DS75162A     | TE = 0.8V, D                                | $DC = 0.8V, SC = 2V, V_1 = 0.8V$      |      | 85   | 125         |       |

| C <sub>IN</sub>   | Bus-Port<br>Capacitance                | Bus          | $V_{CC} = 5V \text{ or}$<br>f = 1 MHz       | $0V, V_{I} = 0V \text{ to } 2V,$      |      | 20   | 30          | pF    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified, min/max limits apply across the 0°C to +70°C temperature range and the 4.75V to 5.25V power supply range. All typical values are for T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5.0V.

Note 3: All currents into device pins are shown as positive; all currents out of device pins are shown as negative; all voltages are referenced to ground, unless otherwise specified. All values shown as max or min are so classified on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: This characteristic does not apply to outputs on DS75161A and DS75162A that are open collector.

| Symbol           | Demonstern                                          | From                 | То       | Conditions                                            | D        | S7516    | 0 <b>A</b> | D        | S7516                                           | 1A  | D   | S7516 | 2A  | Units |    |  |    |    |    |

|------------------|-----------------------------------------------------|----------------------|----------|-------------------------------------------------------|----------|----------|------------|----------|-------------------------------------------------|-----|-----|-------|-----|-------|----|--|----|----|----|

| Symbol           | Parameter                                           | From                 | 10       | Conditions                                            | Min      | Тур      | Max        | Min      | Тур                                             | Max | Min | Тур   | Max | Units |    |  |    |    |    |

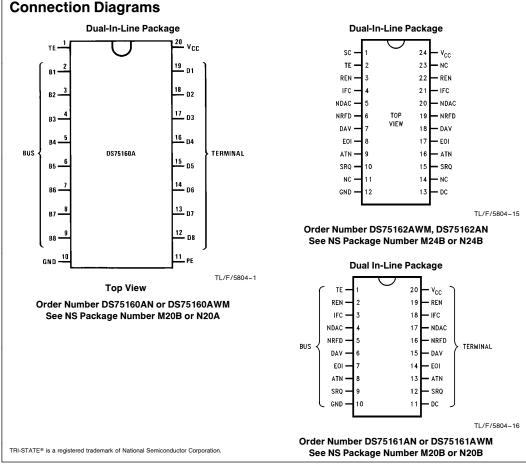

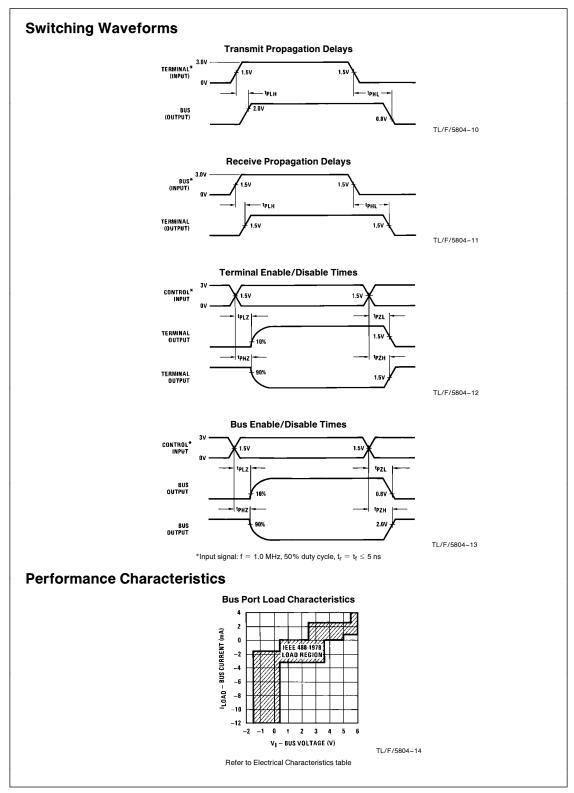

| t <sub>PLH</sub> | Propagation Delay Time,<br>Low to High Level Output | Terminal             | Bus      | $V_L = 2.3V$<br>$R_L = 38.3\Omega$                    |          | 10       | 20         |          | 10                                              | 20  |     | 10    | 20  | ns    |    |  |    |    |    |

| t <sub>PHL</sub> | Propagation Delay Time,<br>High to Low Level Output | Terminal             | Dus      | C <sub>L</sub> = 30 pF<br><i>Figure 1</i>             |          | 14       | 20         |          | 14                                              | 20  |     | 14    | 20  | ns    |    |  |    |    |    |

| t <sub>PLH</sub> | Propagation Delay Time,<br>Low to High Level Output | Bus                  | Terminal | $V_L = 5.0V$<br>$R_L = 240\Omega$                     |          | 14       | 20         |          | 14                                              | 20  |     | 14    | 20  | ns    |    |  |    |    |    |

| t <sub>PHL</sub> | Propagation Delay Time,<br>High to Low Level Output | 500                  | rennina  | C <sub>L</sub> = 30 pF<br><i>Figure 2</i>             |          | 10       | 20         |          | 10                                              | 20  |     | 10    | 20  | ns    |    |  |    |    |    |

| t <sub>PZH</sub> | Output Enable Time<br>to High Level                 |                      |          | $V_{I} = 3.0V$<br>$V_{L} = 0V$                        |          | 19       | 32         |          | 23                                              | 40  |     | 23    | 40  | ns    |    |  |    |    |    |

| t <sub>PHZ</sub> | Output Disable Time<br>From High Level              | TE, DC,<br>or SC     | Bus      | $R_{L} = 480\Omega$ $C_{L} = 15 \text{ pF}$ Figure 1  |          | 15       | 22         |          | 15                                              | 25  |     | 15    | 25  | ns    |    |  |    |    |    |

| t <sub>PZL</sub> | Output Enable Time<br>to Low Level                  | (Note 2)<br>(Note 3) |          | $V_{I} = 0V$<br>$V_{L} = 2.3V$                        |          | 24       | 35         |          | 28                                              | 48  |     | 28    | 48  | ns    |    |  |    |    |    |

| t <sub>PLZ</sub> | Output Disable Time<br>From Low Level               |                      |          | $R_{L} = 38.3\Omega$ $C_{L} = 15 \text{ pF}$ Figure 1 |          | 17       | 25         |          | 17                                              | 27  |     | 17    | 27  | ns    |    |  |    |    |    |

| t <sub>PZH</sub> | Output Enable Time<br>to High Level                 |                      |          | $V_{I} = 3.0V$<br>$V_{L} = 0V$                        |          | 17       | 33         |          | 18                                              | 40  |     | 18    | 40  | ns    |    |  |    |    |    |

| t <sub>PHZ</sub> | Output Disable Time<br>From High Level              | TE, DC,<br>or SC     | Terminal | Terminal                                              | Terminal | Terminal | Terminal   | Terminal | $R_L = 3 k\Omega$ $C_L = 15 pF$ <i>Figure 1</i> |     | 15  | 25    |     | 22    | 33 |  | 22 | 33 | ns |

| t <sub>PZL</sub> | Output Enable Time<br>to Low Level                  | (Note 2)<br>(Note 3) |          | $V_{I} = 0V$<br>$V_{L} = 5V$                          |          | 25       | 39         |          | 28                                              | 52  |     | 28    | 52  | ns    |    |  |    |    |    |

| t <sub>PLZ</sub> | Output Disable Time<br>From Low Level               |                      |          | $R_{L} = 280\Omega$ $C_{L} = 15 \text{ pF}$ Figure 1  |          | 15       | 27         |          | 20                                              | 35  |     | 20    | 35  | ns    |    |  |    |    |    |

| t <sub>PZH</sub> | Output Pull-Up Enable<br>Time (DS75160A Only)       | PE                   | Bus      | $V_I = 3V$<br>$V_L = 0V$                              |          | 10       | 17         |          | NA                                              |     |     | NA    |     | ns    |    |  |    |    |    |

| t <sub>PHZ</sub> | Output Pull-UP Disable<br>Time (DS75160A Only)      | (Note 2)             | 2) Bus   | $R_{L} = 480\Omega$ $C_{L} = 15 \text{ pF}$ Figure 1  |          | 10       | 15         |          | NA                                              |     |     | NA    |     | ns    |    |  |    |    |    |

Note 1: Typical values are for  $V_{CC}=$  5.0V and  $T_{A}=$  25°C and are meant for reference only.

Note 2: Refer to Functional Truth Tables for control input definition.

Note 3: Test configuration should be connected to only one transceiver at a time due to the high current stress caused by the V<sub>I</sub> voltage source when the output connected to that input becomes active.

http://www.national.com

TL/F/5804-9

N914

1N914

# Functional Description DS75160A

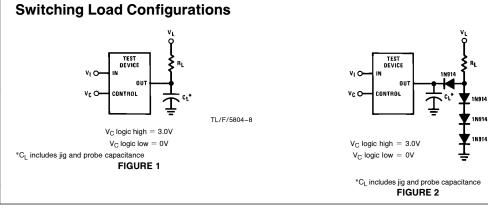

This device is an 8-channel bi-directional transceiver with one common direction control input, denoted TE. When used to implement the IEEE-488 bus, this device is connected to the eight data bus lines, designated DIO<sub>1</sub>-DIO<sub>8</sub>. The port connections to the bus lines have internal terminators, in accordance with the IEEE-488 Standard, that are deactivated when the device is powered down. This feature guarantees no bus loading when V<sub>CC</sub> = 0V. The bus port outputs also have a control mode that either enables or disables the active upper stage of the totem-pole configuration. When this control input, denoted PE, is in the high state, the bus outputs operate in the high-speed totem-pole as open collector outputs which are necessary for parallel polling.

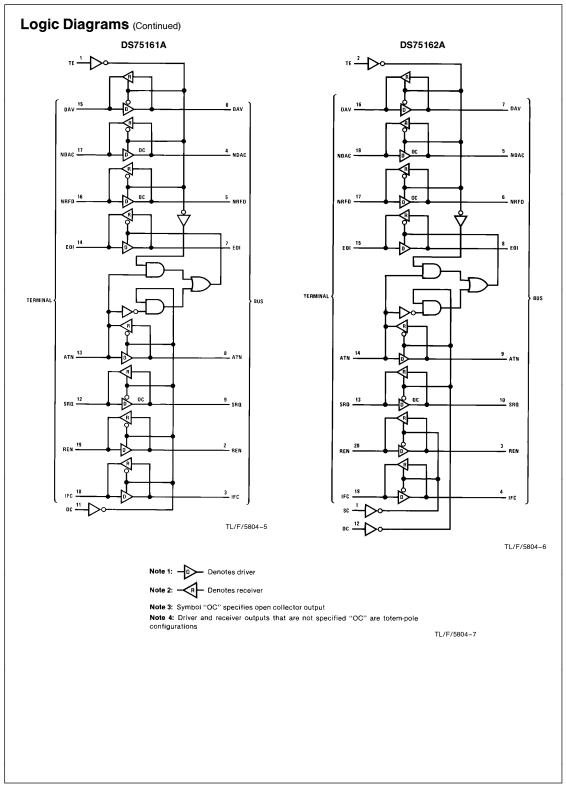

### DS75161A

This device is also an 8-channel bi-directional transceiver which is specifically configured to implement the eight management signal lines of the IEEE-488 bus. This device, paired with the DS75160A, forms the complete 16-line interface between the IEEE-488 bus and a single controller instrumentation system. In compliance with the system organization of the management signal lines, the SRQ, NDAC, and NRFD bus port outputs are open collector. In contrast to the DS75160A, these open collector outputs are a fixed configuration. The direction control is divided into three groups. The DAV, NDAC, and NRFD transceiver directions are controlled by the TE input. The ATN, SRQ, REN, and IFC transceiver directions are controlled by the DC input. The EOI transceiver direction is a function of both the TE and DC inputs, as well as the logic level present on the ATN channel. The port connections to the bus lines have internal terminators identical to the DS75160A.

#### DS75162A

This device is identical to the DS75161A, except that an additional direction control input is provided, denoted SC. The SC input controls the direction of the REN and IFC transceivers that are normally controlled by the DC input on the DS75161A. This additional control function is instrumental in implementing multiple controller systems.

Table of Signal Line Abbr

| Signal Line<br>Classi-<br>fication | Mne-<br>monic | Definition                 | Device                |  |  |  |

|------------------------------------|---------------|----------------------------|-----------------------|--|--|--|

|                                    | DC            | Direction Control          | DS75161A/<br>DS75162A |  |  |  |

| Control                            | PE            | Pull-Up Enable             | DS75160A              |  |  |  |

| Signals                            | TE            | Talk Enable                | All                   |  |  |  |

|                                    | SC            | System Controller          | DS75162A              |  |  |  |

| Data                               | B1-B8         | Bus Side of Device         |                       |  |  |  |

| I/O Ports                          | D1-D8         | Terminal Side<br>of Device | DS75160A              |  |  |  |

|                                    | ATN           | Attention                  |                       |  |  |  |

|                                    | DAV           | Data Valid                 | 1                     |  |  |  |

|                                    | EOI           | End or Identify            |                       |  |  |  |

| Management                         | IFC           | Interface Clear            |                       |  |  |  |

| Signals                            | NDAC          | Not Data Accepted          | DS75162A              |  |  |  |

|                                    | NRFD          | Not Ready for Data         | ]                     |  |  |  |

|                                    | REN           | Remote Enable              | -                     |  |  |  |

|                                    | SRQ           | Service Request            |                       |  |  |  |

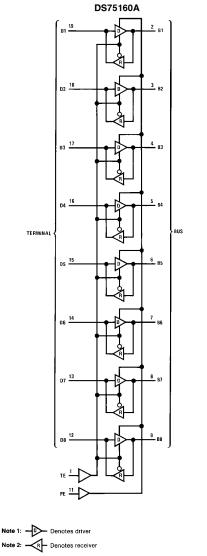

### Logic Diagrams

Note 3: Driver and receiver outputs are totem-pole configurations Note 4: The driver outputs of DS75160A can have their active pull-ups disabled by switching the PE input (pin 11) to the logic iow state. This mode configures the outputs as open collector.

TL/F/5804-4

6

## **Functional Truth Tables**

|               | DS75160A |           |                               |  |  |  |  |  |  |  |  |

|---------------|----------|-----------|-------------------------------|--|--|--|--|--|--|--|--|

| Contro<br>Lev | •        | Da        | ata Transceivers              |  |  |  |  |  |  |  |  |

| TE            | PE       | Direction | <b>Bus Port Configuration</b> |  |  |  |  |  |  |  |  |

| н             | н        | Т         | Totem-Pole Output             |  |  |  |  |  |  |  |  |

| н             | L        | Т         | Open Collector Output         |  |  |  |  |  |  |  |  |

| L             | X        | R         | Input                         |  |  |  |  |  |  |  |  |

|        | DS75161A            |   |   |     |                              |   |         |   |      |     |  |  |  |

|--------|---------------------|---|---|-----|------------------------------|---|---------|---|------|-----|--|--|--|

| Contro | Control Input Level |   |   |     | Transceiver Signal Direction |   |         |   |      |     |  |  |  |

| TE     | TE DC ATN           |   | * | EOI | EOI REN                      |   | IFC SRQ |   | NDAC | DAV |  |  |  |

| н      | н                   |   | R |     | R                            | R | т       | R | R    | Т   |  |  |  |

| н      | L                   |   | Т |     | Т                            | Т | R       | R | R    | Т   |  |  |  |

| L      | н                   |   | R |     | R                            | R | Т       | Т | Т    | R   |  |  |  |

| L      | L                   |   | Т |     | Т                            | Т | R       | Т | Т    | R   |  |  |  |

| н      | Х                   | н |   | т   |                              |   |         |   |      |     |  |  |  |

| L      | х                   | н |   | R   |                              |   |         |   |      |     |  |  |  |

| X      | н                   | L |   | R   |                              |   |         |   |      |     |  |  |  |

| X      | L                   | L |   | Т   |                              |   |         |   |      |     |  |  |  |

| DS75162A |          |         |    |            |                              |     |     |     |      |      |     |  |  |  |

|----------|----------|---------|----|------------|------------------------------|-----|-----|-----|------|------|-----|--|--|--|

| Con      | trol Inp | ut Leve | I  |            | Transceiver Signal Direction |     |     |     |      |      |     |  |  |  |

| SC       | TE       | DC      | AT | <b>N</b> * | EOI                          | REN | IFC | SRQ | NRFD | NDAC | DAV |  |  |  |

| Н        | н        | н       |    | R          |                              | т   | т   | т   | R    | R    | т   |  |  |  |

| н        | н        | L       |    | Т          |                              | Т   | Т   | R   | R    | R    | Т   |  |  |  |

| н        | L        | н       |    | R          |                              | Т   | Т   | Т   | Т    | Т    | R   |  |  |  |

| н        | L        | L       |    | Т          |                              | Т   | Т   | R   | Т    | Т    | R   |  |  |  |

| L        | н        | н       |    | R          |                              | R   | R   | Т   | R    | R    | Т   |  |  |  |

| L        | н        | L       |    | Т          |                              | R   | R   | R   | R    | R    | Т   |  |  |  |

| L        | L        | н       |    | R          |                              | R   | R   | Т   | Т    | Т    | R   |  |  |  |

| L        | L        | L       |    | Т          |                              | R   | R   | R   | Т    | Т    | R   |  |  |  |

| х        | н        | Х       | н  |            | Т                            |     |     |     |      |      |     |  |  |  |

| х        | L        | x       | н  |            | R                            |     |     |     |      |      |     |  |  |  |

| х        | х        | н       | L  |            | R                            |     |     |     |      |      |     |  |  |  |

| х        | х        | L       | L  |            | Т                            |     |     |     |      |      |     |  |  |  |

H = High level input

L = Low level input

X = Don't care

T = Transmit, i.e., signal outputted to bus

R = Receive, i.e., signal outputted to terminal

\*The ATN signal level is sensed for internal multiplex control of EOI transmission direction logic.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications