# STV0903BAC

# Multi-standard advanced demodulator for satellite digital TV set-top boxes

### **Features**

- Multi-standard demodulation

- Legacy DVBS and DirecTV<sup>™</sup> QPSK

- DVBS2 QPSK, 8PSK

- Up to 45Msps DVBS, DSS, DVBS2 QPSK and 8PSK

- Multi-tap equalizer for RF reflection removal

- Wide range carrier frequency tracking loop for offset recovery

- Multi-standard decoding

- DVBS or DirecTV<sup>TM</sup> legacy

- DVBS2 FEC and framing

- Interfaces

Confidentia

- Data to MPEG decoder

- DVB common interface compliant

- I<sup>2</sup>C serial bus interface, including private repeater for tuner

- JTAG interface for boundary scan

- DiSEqC 2.x 22-kHz interfaces

- FSK interface

- Flexible GPIOs and interrupts

- Bit error rate monitoring and reporting

- Technology

- Multi supply: 1.0-V core, 2.5-V analog, 3.3-V digital interfaces

- Power saving features

- LQFP128-EP 14 x 14 mm<sup>2</sup> package, environmentally friendly

May 2009 8073291 Rev F 1/246

Contents STV0903BAC

# **Contents**

| 1     | Desc               | cription                                                    | 8          |

|-------|--------------------|-------------------------------------------------------------|------------|

|       | 1.1                | Overview                                                    | 8          |

|       | 1.2                | Versions                                                    | 8          |

|       | 1.3                | Key features for broadcast applications                     | 9          |

| 2     | Pin i              | information                                                 | 11         |

|       | 2.1                | Pin connections                                             | 11         |

|       | 2.2                | Pin description                                             | 12         |

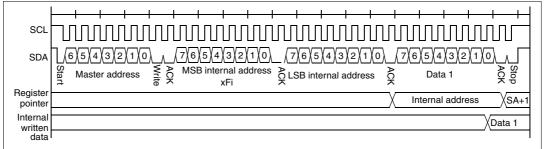

| 3     | l <sup>2</sup> C i | nterface                                                    | 16         |

|       | 3.1                | Introduction                                                | 16         |

|       | 3.2                | I <sup>2</sup> C chip addresses                             | 16         |

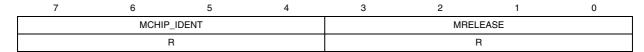

|       | 3.3                | Identification register                                     | 16         |

|       | 3.4                | Register access                                             | 17         |

|       |                    | 3.4.1 Write operation                                       | 17         |

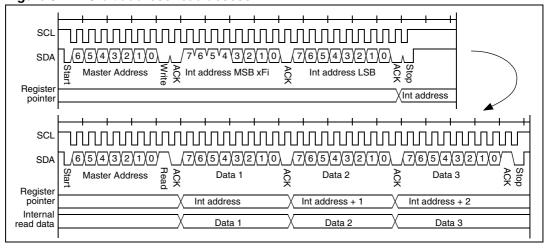

|       |                    | 3.4.2 Read operation                                        | 17         |

|       |                    | 3.4.3 Example                                               |            |

|       |                    | 3.4.4 Advanced modes                                        |            |

|       | 3.5                | Standby mode                                                | 18         |

|       | 3.6                | I <sup>2</sup> C bus repeater                               | 19         |

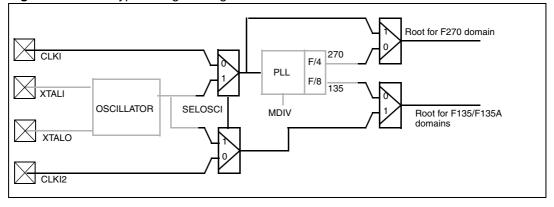

| 4     | Cloc               | k generation                                                | 21         |

|       | 4.1                | Frequency synthesis                                         | 21         |

|       | 4.2                | Starting PLL, power up sequence                             | 22         |

|       | 4.3                | Starting PLL using external clock source (engineering mode) | 23         |

|       | 4.4                | Clock sources                                               | 23         |

|       |                    | 4.4.1 Clock source choice                                   | 23         |

|       |                    | 4.4.2 Standby                                               | 25         |

|       |                    | 4.4.3 Summary                                               | 25         |

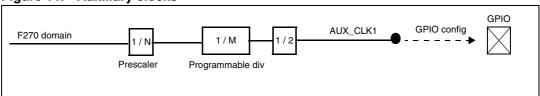

|       | 4.5                | CLKOUT27                                                    | 25         |

|       | 4.6                | AUX_CLK                                                     | 26         |

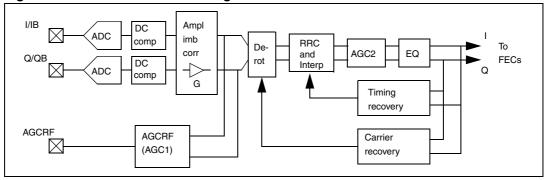

| 5     | Dem                | odulation                                                   | 27         |

| 2/246 |                    | 8073291 Rev F                                               | <b>577</b> |

| STV0903BAC |      |  |  |  |  |

|------------|------|--|--|--|--|

| 5.1        | ADCs |  |  |  |  |

|            |      |  |  |  |  |

|   | 5.1                                                              | ADCs                                                                                                                                                                                                                                                                                                        | . 21                                                                 |

|---|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | 5.2                                                              | DC offset compensation, IQ mismatch and quadrature error correction                                                                                                                                                                                                                                         | . 28                                                                 |

|   | 5.3                                                              | AGC1 tuner level control                                                                                                                                                                                                                                                                                    | . 28                                                                 |

|   | 5.4                                                              | Spectrum inversion                                                                                                                                                                                                                                                                                          | . 29                                                                 |

|   | 5.5                                                              | Roll-off factor                                                                                                                                                                                                                                                                                             | . 29                                                                 |

|   | 5.6                                                              | AGC2 signal amplitude control                                                                                                                                                                                                                                                                               | . 29                                                                 |

|   | 5.7                                                              | Timing loop                                                                                                                                                                                                                                                                                                 | . 30                                                                 |

|   | 5.8                                                              | Timing lock detector                                                                                                                                                                                                                                                                                        | . 30                                                                 |

|   | 5.9                                                              | Carrier loop                                                                                                                                                                                                                                                                                                | . 31                                                                 |

|   | 5.10                                                             | Carrier lock detector (DVBS/DirecTV only)                                                                                                                                                                                                                                                                   | . 31                                                                 |

|   | 5.11                                                             | Equalizer                                                                                                                                                                                                                                                                                                   | . 31                                                                 |

|   | 5.12                                                             | Tuner control                                                                                                                                                                                                                                                                                               | . 32                                                                 |

|   | 5.13                                                             | Algorithmic entry points (AEP)                                                                                                                                                                                                                                                                              | . 32                                                                 |

|   | 5.14                                                             | Results FIFO                                                                                                                                                                                                                                                                                                | . 34                                                                 |

|   | 5.15                                                             | Interrupt controller                                                                                                                                                                                                                                                                                        | . 34                                                                 |

|   | 5.16                                                             | Noise indicators                                                                                                                                                                                                                                                                                            | . 35                                                                 |

|   |                                                                  |                                                                                                                                                                                                                                                                                                             | -                                                                    |

| 6 | DVB-                                                             | -S forward error correction                                                                                                                                                                                                                                                                                 | . 36                                                                 |

| 6 | <b>DVB</b> -<br>6.1                                              | FEC modes, status and error reporting                                                                                                                                                                                                                                                                       |                                                                      |

| 6 |                                                                  |                                                                                                                                                                                                                                                                                                             | . 36                                                                 |

| 6 | 6.1                                                              | FEC modes, status and error reporting                                                                                                                                                                                                                                                                       | . 36<br>. 37                                                         |

| 6 | 6.1<br>6.2                                                       | FEC modes, status and error reporting                                                                                                                                                                                                                                                                       | . 36<br>. 37<br>. 37                                                 |

| 6 | 6.1<br>6.2<br>6.3                                                | FEC modes, status and error reporting                                                                                                                                                                                                                                                                       | . 36<br>. 37<br>. 37                                                 |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                  | FEC modes, status and error reporting  Viterbi decoder                                                                                                                                                                                                                                                      | . 36<br>. 37<br>. 37                                                 |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                  | FEC modes, status and error reporting  Viterbi decoder                                                                                                                                                                                                                                                      | . 36<br>. 37<br>. 38<br>. 38                                         |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                  | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction                                                                                                                                     | . 36<br>. 37<br>. 38<br>. 38<br>. 39                                 |

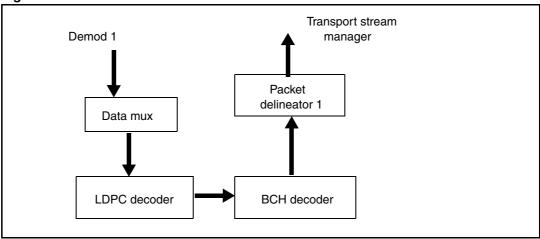

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>DVB</b> -7.1               | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction  Introduction                                                                                                                       | . 36<br>. 37<br>. 38<br>. 38<br>. 39                                 |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>DVB</b> -7.1<br>7.2        | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction  Introduction  Architecture                                                                                                         | . 36<br>. 37<br>. 38<br>. 38<br>. 39<br>. 39                         |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>DVB</b> -7.1<br>7.2        | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction  Introduction  Architecture  Features summary                                                                                       | . 36<br>. 37<br>. 38<br>. 38<br>. 39<br>. 39<br>. 40                 |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>DVB</b> -7.1<br>7.2<br>7.3 | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction  Introduction  Architecture  Features summary  7.3.1 Single input functional description                                            | . 36<br>. 37<br>. 38<br>. 38<br>. 39<br>. 39<br>. 40                 |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>DVB</b> -7.1<br>7.2<br>7.3 | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction  Introduction  Architecture  Features summary  7.3.1 Single input functional description  LDPC/BCH decoder                          | . 36<br>. 37<br>. 38<br>. 38<br>. 39<br>. 39<br>. 40<br>. 40<br>. 40 |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>DVB</b> -7.1<br>7.2<br>7.3 | FEC modes, status and error reporting  Viterbi decoder  Synchronization  Convolutive de-interleaver  Reed-solomon decoder and descrambler  -S2 forward error correction  Introduction  Architecture  Features summary  7.3.1 Single input functional description  LDPC/BCH decoder  7.4.1 Supported MODCODs | . 36<br>. 37<br>. 38<br>. 38<br>. 39<br>. 39<br>. 40<br>. 40<br>. 41 |

**577**

8073291 Rev F

3/246

Information classified Confidential - Do not copy (See last page for obligations)

**577**

STV0903BAC

|    |       | 7.5.1    | Descrambling                                     | 42 |

|----|-------|----------|--------------------------------------------------|----|

|    |       | 7.5.2    | Baseband frames header (BBH) integrity checking  | 42 |

|    |       | 7.5.3    | Lock monitoring                                  | 42 |

|    |       | 7.5.4    | Header processing and transport stream filtering | 43 |

|    |       | 7.5.5    | Data field processing                            | 43 |

|    |       | 7.5.6    | SYNCD estimator                                  | 43 |

|    |       | 7.5.7    | BCH check                                        | 43 |

| 8  | Trans | sport st | tream interface                                  | 44 |

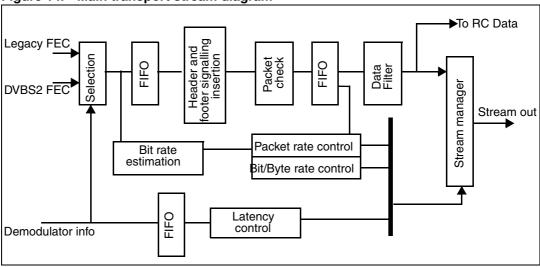

|    | 8.1   | Transp   | ort stream overview                              | 44 |

|    | 8.2   | Transp   | ort stream output processing                     | 44 |

|    |       | 8.2.1    | General                                          | 44 |

|    |       | 8.2.2    | Data rate control                                | 45 |

|    |       | 8.2.3    | Latency Control                                  | 46 |

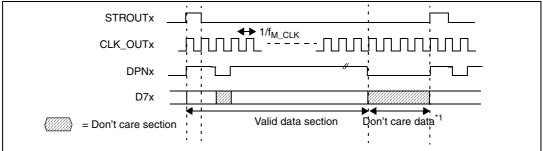

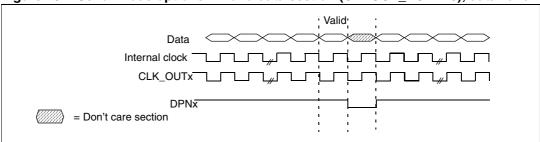

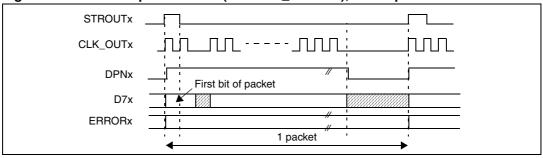

|    | 8.3   | Serial   | output modes                                     | 47 |

|    | 8.4   | Paralle  | el output modes                                  | 49 |

| 9  | DiSE  | qC 2.x   | interface                                        | 51 |

|    | 9.1   | Introdu  | uction                                           | 51 |

|    | 9.2   | Transm   | nit DiSEqC interface                             | 51 |

|    |       | 9.2.1    | Typical byte transfer loop                       | 51 |

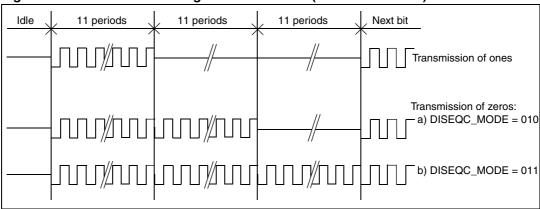

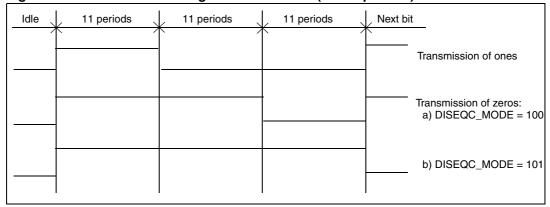

|    |       | 9.2.2    | Transmit format                                  | 51 |

|    |       | 9.2.3    | DiSEqC modes SA, SB and continuous               | 53 |

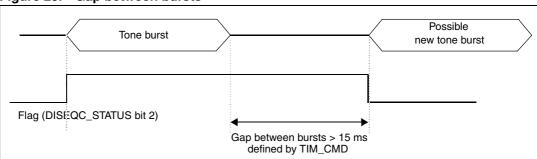

|    |       | 9.2.4    | Transmit burst gap control                       | 53 |

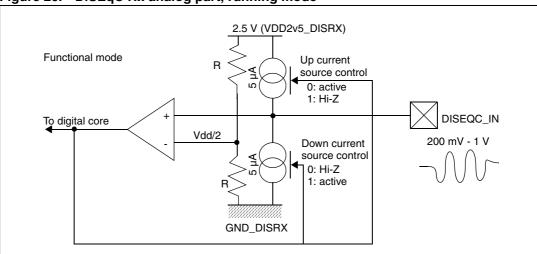

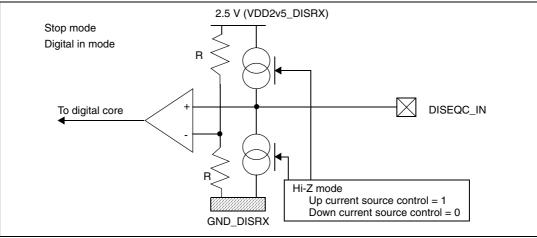

|    | 9.3   | Receiv   | ve DiSEqC interface                              | 54 |

| 10 | FSK   | interfac | ce                                               | 56 |

|    | 10.1  | Introdu  | uction                                           | 56 |

|    | 10.2  | FSK a    | ctivation                                        | 56 |

|    | 10.3  |          | ansmitter                                        |    |

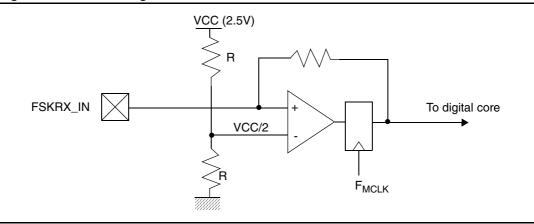

|    | 10.4  |          | eceiver                                          |    |

| 11 | Gane  | eral nur | pose I/O (GPIO)                                  | 60 |

|    | 11.1  | Overvi   | • • •                                            |    |

|    |       |          |                                                  |    |

|    | 11.2  |          | ogrammed GPIOs                                   |    |

|    | 11.3  | Unallo   | cated GPIO functions                             | 61 |

8073291 Rev F

4/246

Confidential

Contents

Contents

# Confidential

STV0903BAC

| 12        | Interr | rupt request (IRQ)                       | 64    |

|-----------|--------|------------------------------------------|-------|

|           | 12.1   | Overview                                 | 64    |

|           | 12.2   | IRQ configuration                        | 64    |

| 13        | JTAG   | interface                                | 65    |

| 14        | Electi | rical specifications                     | 66    |

|           | 14.1   | Absolute maximum ratings                 | 66    |

|           | 14.2   | Thermal data                             | 66    |

|           | 14.3   | DC electrical specifications             | 67    |

|           | 14.4   | AC electrical specifications             | 68    |

|           | 14.5   | Dual ADC 8-bit specifications            | 69    |

|           | 14.6   | Transport stream timing specifications   | 70    |

|           | 14.7   | I <sup>2</sup> C bus specifications      | 71    |

|           | 14.8   | Crystal oscillator specifications        | 72    |

|           | 14.9   | FSK receiver, transmitter specifications | 73    |

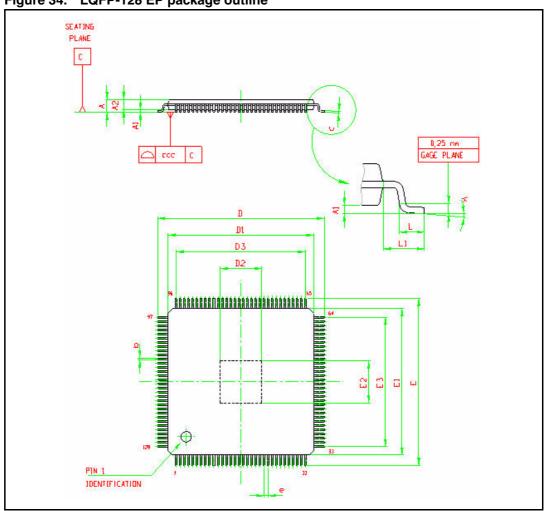

| 15        | Packa  | age mechanical data                      | 74    |

|           | 15.1   | Environmentally-friendly packaging       | 75    |

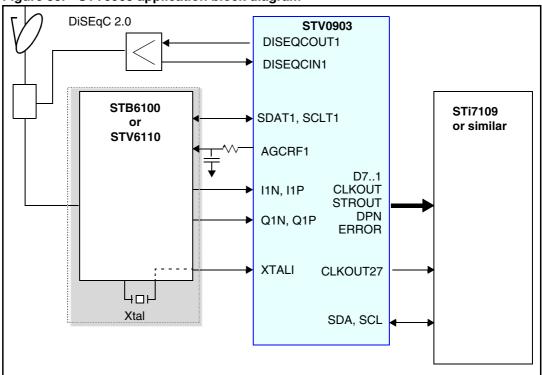

| 16        | Appli  | cations block diagram                    | 76    |

| 17        | Regis  | sters                                    | 77    |

|           | 17.1   | Register Summary                         | 77    |

|           | 17.2   | SYS register descriptions                | 87    |

|           | 17.3   | FSK register descriptions                | 107   |

|           | 17.4   | DIS register descriptions                | 115   |

|           | 17.5   | DMD register descriptions                | 121   |

|           | 17.6   | TUN register descriptions                |       |

|           | 17.7   | DVB1 register descriptions               | 197   |

|           | 17.8   | DVB2 register descriptions               | 206   |

|           | 17.9   | TS register descriptions                 | 220   |

|           | 17.10  | TST register descriptions                | 243   |

| 18        | Revis  | sion history                             | 245   |

| <b>57</b> |        | 8073201 Ray F                            | 5/246 |

List of tables STV0903BAC

# List of tables

| Table 1.  | Maximum symbol rate limitations                                   | . 9 |

|-----------|-------------------------------------------------------------------|-----|

| Table 2.  | Transport stream output limitations                               | 10  |

| Table 3.  | DVB-S2 profile implemented and supported for the broadcast market | 10  |

| Table 4.  | Pin list                                                          |     |

| Table 5.  | I <sup>2</sup> C addresses                                        |     |

| Table 6.  | MDIV recommended values                                           |     |

| Table 7.  | Clock generation registers                                        |     |

| Table 8.  | Prescaler ratios                                                  | 26  |

| Table 9.  | Divider ratios                                                    |     |

| Table 10. | MODCOD encoding                                                   |     |

| Table 11. | TSFIFO_MANSPEED configuration                                     | 45  |

| Table 12. | TS allowed speeds                                                 | 45  |

| Table 13. | Chip total latency                                                |     |

| Table 14. | Rate compensation mode settings                                   |     |

| Table 15. | Rate compensation mode settings                                   |     |

| Table 16. | Modulator gain values                                             |     |

| Table 17. | Pre-defined GPIOs                                                 |     |

| Table 18. | GPIO configuration                                                |     |

| Table 19. | STREAM_STATUS16 configuration                                     |     |

| Table 20. | List of IRQs                                                      |     |

| Table 21. | TAP control signals                                               |     |

| Table 22. | Absolute maximum ratings                                          |     |

| Table 23. | Thermal data                                                      |     |

| Table 24. | DC electrical specifications                                      |     |

| Table 25. | AC electrical specifications                                      |     |

| Table 26. | ADC specifications                                                |     |

| Table 27. | Transport stream timing specifications                            |     |

| Table 28. | I <sup>2</sup> C bus specifications                               |     |

| Table 29. | Crystal oscillator specifications                                 |     |

| Table 30. | Tested crystals and their parameters                              |     |

| Table 31. | FSK specifications                                                |     |

| Table 32. | LQFP-128 EP package dimensions                                    |     |

| Table 33. | SYS register list                                                 |     |

| Table 34. | FSK register list                                                 |     |

| Table 35. | DIS register list                                                 |     |

| Table 36. | DMD register list                                                 |     |

| Table 37. | TUN register list                                                 |     |

| Table 38. | DVB1 register list                                                |     |

| Table 39. | DVB2 register list                                                |     |

| Table 40. | TS register list                                                  |     |

| Table 41. | TST register list                                                 |     |

| Table 42. | Document revision history                                         | 45  |

6/246 8073291 Rev F

STV0903BAC List of figures

# **List of figures**

| Figure 1.  | Package pin out                                                        | 11 |

|------------|------------------------------------------------------------------------|----|

| Figure 2.  | 16-bit address write access                                            | 17 |

| Figure 3.  | 16-bit address read access                                             | 18 |

| Figure 4.  | Example of normal mode read and write operation                        | 18 |

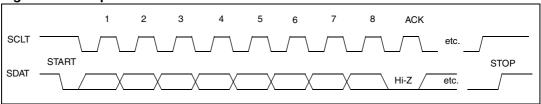

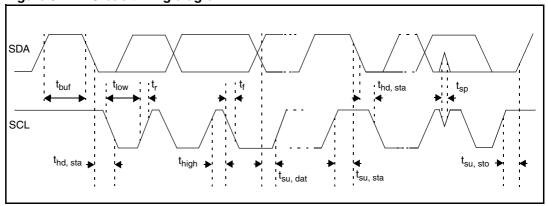

| Figure 5.  | I <sup>2</sup> C protocol                                              |    |

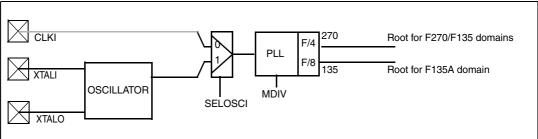

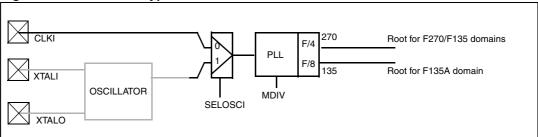

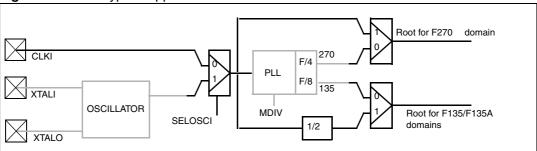

| Figure 6.  | Clock domains                                                          | 22 |

| Figure 7.  | Oscillator active mode                                                 | 23 |

| Figure 8.  | Oscillator bypass mode                                                 | 23 |

| Figure 9.  | PLL bypass application mode                                            | 24 |

| Figure 10. | PLL bypass engineering mode                                            | 24 |

| Figure 11. | Auxiliary clocks                                                       | 26 |

| Figure 12. | Demodulator block diagram                                              | 27 |

| Figure 13. | DVB-S2 FEC architecture                                                | 39 |

| Figure 14. | Main transport stream diagram                                          |    |

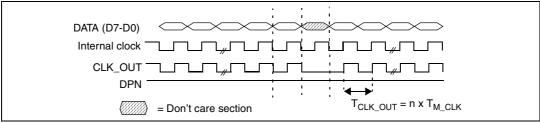

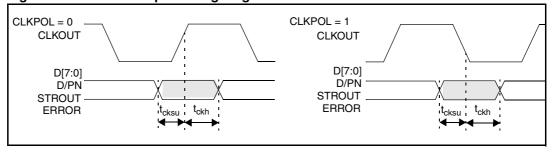

| Figure 15. | Serial output interface (CLKOUT_XOR = 1), data valid                   | 47 |

| Figure 16. | Serial mode options in valid data section (CLKOUT_XOR = 0), data valid | 47 |

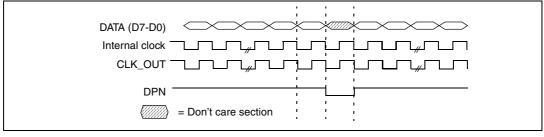

| Figure 17. | Serial output interface (CLKOUT_XOR = 1), envelope                     |    |

| Figure 18. | Serial mode options in valid data section (CLKOUT_XOR = 0), envelope   | 48 |

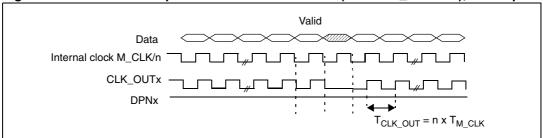

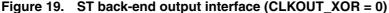

| Figure 19. | ST back-end output interface (CLKOUT_XOR = 0)                          | 49 |

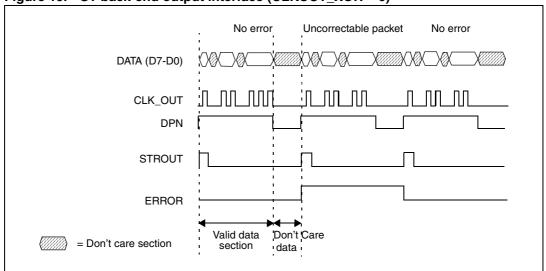

| Figure 20. | DVB-CI output interface (CLKOUT_XOR = 0)                               | 50 |

| Figure 21. | ST back-end in valid data section (CLKOUT_XOR = 0 example)             |    |

| Figure 22. | DVB-CI in valid data section (CLKOUT_XOR = 0)                          | 50 |

| Figure 23. | Schematic showing bit transmission (modulated mode)                    |    |

| Figure 24. | Schematic showing bit transmission (envelop mode)                      | 52 |

| Figure 25. | Gap between bursts                                                     |    |

| Figure 26. | DiSEqC Rx analog part, running mode                                    | 54 |

| Figure 27. | DiSEqC Rx analog part, bypassed mode                                   |    |

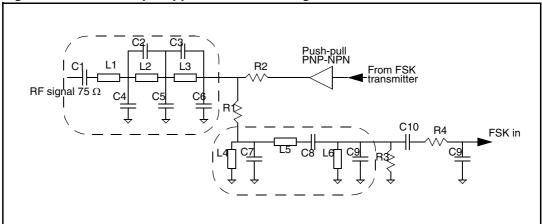

| Figure 28. | FSK analog receiver                                                    |    |

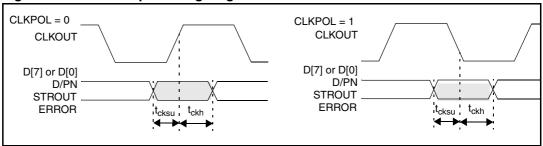

| Figure 29. | Parallel output timing diagram                                         | 70 |

| Figure 30. | Serial output timing diagram                                           | 70 |

| Figure 31. | I <sup>2</sup> C bus timing diagram                                    | 71 |

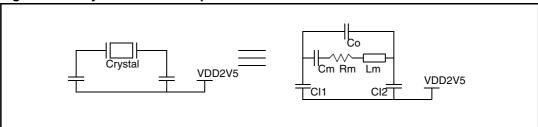

| Figure 32. | Crystal oscillator equivalent model                                    |    |

| Figure 33. | FSK example application circuit diagram                                |    |

| Figure 34. | LQFP-128 EP package outline                                            | 74 |

| Figure 35  | STV0003 application block diagram                                      | 76 |

8073291 Rev F

Information classified Confidential - Do not copy (See last page for obligations)

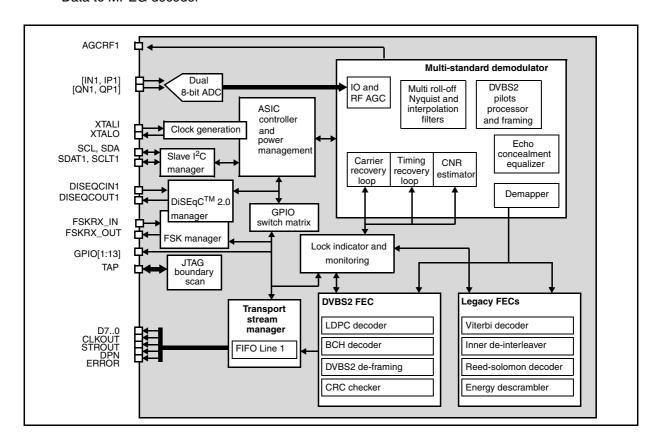

# 1 Description

### 1.1 Overview

The STV0903 is a cost effective, high performance demodulator-decoder for advanced DVB satellite reception. The device supports DVB-S and DirecTV<sup>TM</sup> legacy transmission standards, as well as DVBS2 in QPSK and 8PSK.

The STV0903 features a high-speed DVB-S2 forward error corrector (FEC) which is designed to handle up to 190 channel-Mbit/s at its input. To feed the FEC the STV0903 implements a demodulator, capable of handling QPSK legacy and DVBS2 constant coding and modulation for satellite broadcast

The STV0903 integrates all the features needed to provide a low cost broadcast satellite receiver solution including: integrated crystal oscillator, DiSEqC controller, tuner I<sup>2</sup>C repeater, FSK modem, ancillary DACs and ADCs and many unattributed general purpose input output ports for peripheral control.

A number of state machines and algorithms have been implemented to allow standard functions to be accessed easily and with a minimum of code overhead. Blind scan is implemented allowing an entire band to be searched automatically once a minimum of parameters have been provided. Cold and warm start acquisition and re-acquisition procedures are provided.

Advanced power saving features have been implemented, the LDPC stops once the solution is sufficiently converged and the various blocks of the IC (demodulator, LDPC, Legacy FEC etc.) may be completely shut down if not required.

A real-time constellation output is also available, allowing improved monitoring and debug during product development. Full error monitoring facilities are available and signal statistic are provided via I<sup>2</sup>C. For example, antenna pointing may be assisted via the carrier to noise ratio metric or the electrical installation may be judged according to received RF level and equalizer tap readings (reflection intensity).

### 1.2 Versions

STV0903BAC - Broadcast -This Datasheet from rev F

STV0903BAB - Broadcast -This Datasheet up to rev E

STV0903BAC Description

# 1.3 Key features for broadcast applications

- Single-channel DVB-S / DVB-S2 demodulator/decoder

- Demodulator:

- Two 8-bit ADCs

- One ΣΔ digital RF AGC

- QPSK, 8PSK

- CCM

- Automatic detection and configuration of:

- a) Modulation type

- b) Filter roll-off

- c) Symbol rate

- d) Pilot presence (on/off)

- e) Short or long frames (long frames only)

- Cold or warm start

- Blind recovery of symbol and carrier frequency

- Forward error correction:

- Viterbi and reed-solomon dual decoder (DVBS)

- LDPC + BCH dual decoder (DVBS2)

- Error monitoring

- Transport stream interface:

- Parallel or serial TS interface

- Transport bit rate automatic regulation corresponding to transport clock

- DVB common interface compliant

- DiSEqC 2.0 interface

- FSK interface

- I<sup>2</sup>C repeaters

- JTAG interface.

The STV0903 has been extensively validated for the broadcast operating range of 1 to 45 Msymb/s in DVB-S2 (QPSK and 8PSK) and 1 to 62Msymb/s in DVBS (and DTV legacy). Full test results, reference designs and supporting software are provided.

For DVB-S2 the machinery exists and has been tested as functional from below 1 Msymb/s and up to the rates given in the table below.

Table 1. Maximum symbol rate limitations

| Modulator | Msymb/s |      |             |               |  |

|-----------|---------|------|-------------|---------------|--|

| Modulator | Demod   | LDPC | Theoretical | Design rating |  |

| QPSK      | 67.5    | 95   | 67.5        | 45            |  |

| 8PSK      | 67.5    | 63   | 63          | 45            |  |

Table 2. Transport stream output limitations

| (with 50% duty cycles) | TS clock (MHz) | Max data rate (Mbit/s) |  |

|------------------------|----------------|------------------------|--|

| Single parallel        | 135/4=33.75    | 270                    |  |

| Serial (Div 1)         | 135            | 108                    |  |

| Serial (Div 2)         | 67.5           | 54                     |  |

Table 3. DVB-S2 profile implemented and supported for the broadcast market

| System configuration                | Case                                    | Supported |

|-------------------------------------|-----------------------------------------|-----------|

| QPSK                                | 1/4, 1/3, 2/5                           | No        |

| QF5K                                | 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9, 9/10 | Yes       |

| 8PSK                                | 3/5, 2/3, 3/4, 5/6, 8/9, 9/10           | Yes       |

| 16APSK                              | 2/3, 3/4, 4/5, 5/6, 8/9, 9/10           | No        |

| 32APSK                              | 3/4, 4/5, 5/6, 8/9, 9/10                | No        |

| CCM                                 |                                         | Yes       |

| VCM                                 |                                         | No        |

| ACM                                 |                                         | No        |

| FECFRAME(normal)                    | 64800 (bits)                            | Yes       |

| FECFRAME(short)                     | 16200 (bits)                            | No        |

| Single transport stream             |                                         | Yes       |

| Multiple transport stream           |                                         | Yes       |

| Single Generic Stream               |                                         | Yes       |

| Multiple generic stream             |                                         | Yes       |

| Combined single generic & single TS |                                         | Yes       |

| Roll-off                            | 0,35 0,25 0,20                          | Yes       |

| ISSYI (input stream synchronizer)   |                                         | Yes       |

| Null packet deletion                |                                         | No        |

| Dummy frame insertion               |                                         | Yes       |

| RCS Specific                        |                                         |           |

| SOF & NCR synchronization           |                                         | No        |

10/246 8073291 Rev F

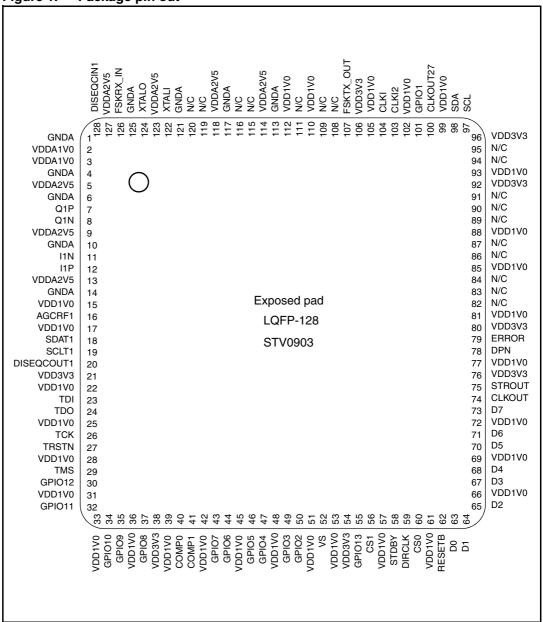

### 2 Pin information

### 2.1 Pin connections

Figure 1. Package pin out

Pin information STV0903BAC

# 2.2 Pin description

Table 4. Pin list

| Table 4. | Pin list   | T      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number   | Name       | Туре   | Voltage | Description / Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EPAD     | GND        | Ground | 0       | Digital core ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1        | GNDA       | Ground | 0       | DiSEqC, FSK and Oscillator analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2        | VDDA1V0    | Supply | 1.0     | DiSEqC, FSK and Oscillator analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3        | VDDA1V0    | Supply | 1.0     | PLL analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4        | GNDA       | Ground | 0       | PLL analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5        | VDDA2V5    | Supply | 2.5     | PLL analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6        | GNDA       | Ground | 0       | PLL analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7        | Q1P        | Analog | -       | ADC1 quadrature phase signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8        | Q1N        | Analog | -       | ADC1 quadrature phase signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9        | VDDA2V5    | Supply | 2.5     | ADC1 analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10       | GNDA       | Ground | 0       | ADC1 analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11       | I1N        | Analog | -       | ADC1 in phase signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12       | I1P        | Analog | -       | ADC1 in phase signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13       | VDDA2V5    | Supply | 2.5     | ADC1 analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14       | GNDA       | Ground | 0       | ADC1 analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15       | VDD1V0     | Supply | 1.0     | Digital core supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |